V dnešních zapojeních s rychlými digitálními obvody už není spoj pouhým spojem. Jeho vysokofrekvenční vlastnosti silně ovlivňují integritu převáděného signálu až do té míry, že se zapojení může stát nefunkčním. Vývojář potom stojí před problémy, které se projevují na prototypu a které je velmi obtížné najít. Nový nástroj pro analýzu integrity signálu Felicitas PCBSim od firmy Felicitas je určen právě pro tento typ úloh, protože analyzuje zapojení už v počáteční fázi vývoje.

Mnohé vlastnosti systému jsou známé už na začátku vývoje zapojení obvodu. Když nic jiného, mohou být alespoň odhadnuty hlavní integrované obvody, konektory a dostupná plocha na desce plošných spojů. Už tyto informace mohou být nápomocny pro vyhodnocení, zda bude konečný návrh z pohledu Signal Integrity funkční, nebo ne. A pokud ne, potřebné modifikace mohou být provedeny ještě ve fázi vývoje, kdy takové změny nejsou finančně náročné a nezpůsobují žádné zpoždění.

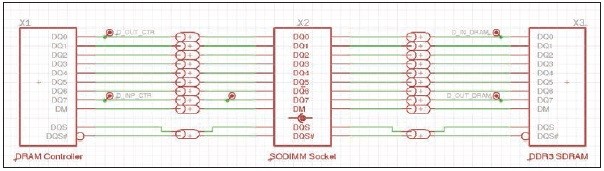

Pro ilustraci typického postupu při vývoji je dále použita synchronní DRAM interface moderního procesoru, na které se provede analýza (obr. 1). Signál prochází (zleva doprava) od procesoru plošným spojem, DRAM paticí a opět krátkým spojem na DRAM čip. Při průchodu všemi těmito spoji musí zůstat signál celistvý a jeho časování musí splňovat určitá omezení s ohledem na ostatní spoje.

Obr. 1 Zapojení DR3 SDRAM obvodu

Integrované obvody jsou obvykle reprezentovány pomocí IBIS modelů. Chování konektorů nebo patic je normálně popsáno prostřednictvím souborů S-parametrů. Vlastnosti plošných spojů jsou odvozeny ve Felicitas PCBSim ze zamýšlené geometrie na budoucí desce plošných spojů. Všechny tyto údaje jsou ve Felicitas PCBSim kompilovány tak, aby se mohl vytvořit komplexní model pro SPICE simulaci, která potom přesně ukáže chování simulovaného obvodu. Provedená simulace zobrazí vývojáři průběhy signálů v jakémkoliv místě obvodu. Tak může být identifikována a provedena požadovaná změna v zapojení ještě před zhotovením vlastního prototypu. Může to být například změna v zakončení spoje přizpůsobovacím členem pro DRAM nebo změna geometrie plošných spojů (šířka, přiřazení vrstvy desky atd.) na desce.

Felicitas PCBSim je nezávislý na programech pro kreslení schémat, ale má dobře propracované návaznosti na tyto nástroje. Výhodou tohoto uspořádání tedy je, že si vývojář může kreslit schéma ve svém programu. V současnosti Felicitas PCBSim podporuje návrhový systém EAGLE, podpora jiných nástrojů se připravuje. Firma Felicitas nabízí také balíček obsahující Felicitas PCBSim a EAGLE. Při napojení na program EAGLE přidá Felicitas PCBSim některé nové prvky do uživatelského rozhraní kreslení schématu v tomto programu a speciální simulační knihovnu. Tak může uživatel systému EAGLE pracovat a nemusí se starat o detaily návaznosti mezi Felicitas PCBSim a editorem schématu.

Uživatel kompletně navrhuje schematické zapojení v editoru schématu. Zvláštní komponenty, jako jsou přenosové linky nebo IO, jsou editovány pomocí kontextové nabídky. Všechny vlastnosti související se simulací jsou uloženy se schématem, čímž je zaručeno, že všechny informace jsou pohromadě a kdykoliv k dispozici.

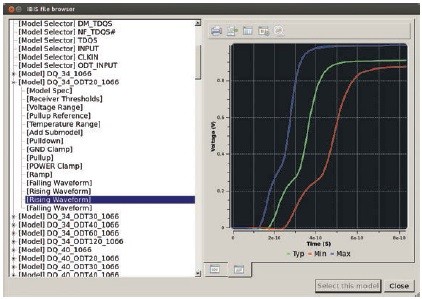

Do programu Felicitas PCBSim je integrován IBIS-Viewer, takže je možné prohlížet IBIS modely dodávané výrobci polovodičových součástek. Pro vývojáře bývá často velmi užitečné podívat se na vstupní nebo výstupní charakteristiky, aby si mohli vybrat odpovídající konfiguraci pro zdroj nebo příjemce signálu.

Obr. 2 IBIS Viewer ve Felicitas PCBSim

V případě, že IBIS model není konzistentní, prohlížeč na tuto skutečnost upozorní. Všechny elementy modelu jsou zobrazeny ve stromové struktuře. Data z IBIS souboru, která představují průběhy, jsou zobrazena graficky. V současné době Felicitas PCBSim podporuje IBIS soubory až do verze 5.1.

Felicitas PCBSim používá křivky průběhu IBIS modelu k vytvoření přesných simulačních modelů. Speciální doplňky ke standardnímu SPICE umožňují, že tyto modely mohou být simulovány přesně a rychle.

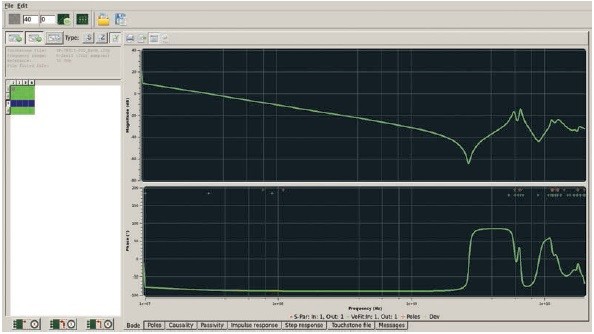

S-parametry (scattering parameters) jsou tabulková data, která popisují odezvu systému v závislosti na kmitočtu. Místo S-parametrů jsou někdy použity admitanční parametry (Y) nebo impedance (Z). Felicitas PCBSim umí pracovat se všemi třemi.

Obr. 3 Editor S-Parametrů ve Felicitas PCBSim

Soubory modelů často zahrnují více vývodů, než je v daném případě pro účely simulace požadováno. To sice v podstatě není na závadu, ale vede to k časově delším simulacím. Felicitas PCBSim proto umožňuje snížit počet vývodů v modelu. Odstraněné vývody mohou být chápány jako zkratované, otevřené nebo přizpůsobené zakončovacím členem pomocí referenční impedance (obvykle 50 Ω).

Data založená na kmitočtech potřebují být přeložena do podoby, která umožňuje přesné a efektivní simulace v časové oblasti. Simulační modely tvořené ze souborů S-parametrů musí splňovat určitá kvalitativní kritéria, jinak simulace nebude úspěšná. Musí být stabilní, to znamená, že určitý vstupní signál musí dát vzniknout určitému výstupnímu signálu. Musí také zajistit, že vstupní signál nevytváří výstupní signál, který začíná ještě před vstupním. A musí být pasivní (pro konektory a patice), protože tyto součástky nevytvářejí energii.

Modely vytvořené ve Felicitas PCBSim svojí povahou splňují výše uvedené požadavky. Jejich pasivní vlastnost je zaručena pokročilým algoritmem, který obvykle zavede do modelu neviditelnou změnu. Vývojář může převést vstupní model ve formátu Touchstone souboru krok za krokem na model připravený pro simulaci. Tím může ovlivnit některé převodové parametry a zkontrolovat výsledky. Je také možné nechat program Felicitas PCBSim, aby ohodnotil všechny vlastnosti modelu a provedl konverzi na stisknutí jednoho tlačítka. Několik různých zobrazení umožňuje detailní náhled na specifické vlastnosti dat S-parametrů. Navíc je zde zabudován textový editor pro kontrolu Touchstone souboru a provedení drobných změn, pokud jsou potřeba.

Simulační modely vytvořené v programu Felicitas PCBSim z originálních Touchstone souborů jsou uloženy jako jednotlivé soubory a jsou tak rychle přístupné pro budoucí simulace.

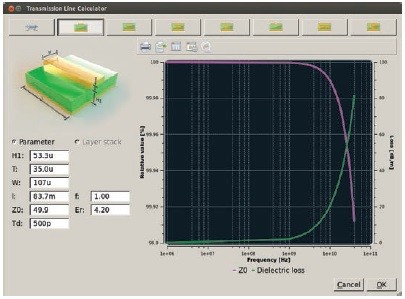

Kalkulátor přenosové linky činí vybrání správné geometrie přenosové linky snadné a intuitivní. Uživatel si může vybrat z nabídky provedení spojů pro microstrip a stripline. Změny v jakémkoliv parametru se okamžitě promítnou v hlavních ukazatelích (impedance, zpoždění) a v diagramech, které zobrazí chování přenosové linky v závislosti na kmitočtu.

Obr. 4 Kalkulátor přenosové linky

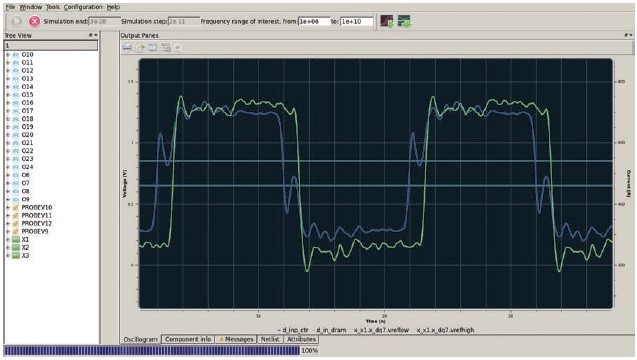

Do Felicitas PCBSim je zabudován plně vybavený SPICE simulační program. Firma Felicitas navíc přidala některé zvláštní funkce, aby bylo možné přesně a rychle simulovat IBIS modely a S-parametry modelů. Na obr. 5 jsou výsledky příkladu zapojení uvedeného na obr. 1. Zde je možné vidět, že vstupní signál pro řadič paměti DRAM zvoní a dokonce překračuje prahovou úroveň (modrá čára). Tato situace pravděpodobně způsobí, že obvod nebude funkční. Vstupní signál DRAM (zelená čára) je v pořádku.

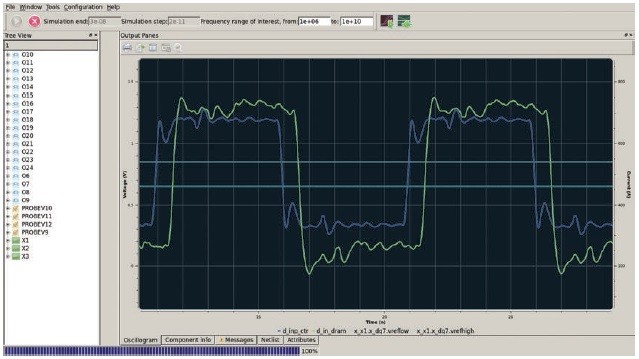

Obr. 5 První výsledek simulace: prahové úrovně jsou překročeny

Aby bylo možné napravit vzniklý problém, byly provedeny následující změny: Impedance přenosové linky byla snížena z 50 na 35 Ω. Vstup DRAM byl ošetřen 40Ω rezistorem, u řadiče 40Ω. U řadiče DRAM byla vybrána jiná vstupní konfigurace. Testováno bylo použití sériových rezistorů, ale ty situaci nezlepšily.

Výsledkem těchto úprav je výrazně nižší zvonění a přijatelný odstup od prahových úrovní, což vede ke spolehlivému funkčnímu návrhu. Některé modifikace by nebyly v případě použití prototypu možné. Navíc najít příčinu problému měřením by bylo velmi obtížné.

Obr. 6 Výsledek simulace opraveného obvodu

Program Felicitas PCBSim umožňuje kontrolovat integritu kritických signálů již v počátečním stadiu návrhu. Možné problémy jsou identifikovány a jednoduchým způsobem opraveny. Pravděpodobnost úspěchu prvního prototypu je tak výrazně vyšší, a Felicitas PCBSim tak účinně pomáhá splnit dané požadavky na vývoj.