Návrh programovatelných hradlových polí FPGA bývá často automaticky spojován s použitím vývojových nástrojů (simulátoru i implementačních nástrojů) jednotlivých výrobců FPGA, jako například Xilinx, Altera, Lattice, Actel a dalších. Pro domácí použití a pro návrh menších obvodů v komerční sféře jsou tyto nástroje většinou dostačující. Nicméně pro skutečně profesionální práci a pro návrh velkých obvodů FPGA bývají limitace těchto nástrojů často kritické. V případě souběžného návrhu zákaznických integrovaných obvodů ASIC a obvodů FPGA je pak použití většiny volně dostupných nástrojů prakticky vyloučené.

1.jpg)

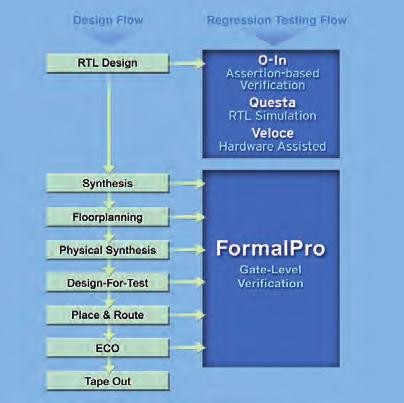

Obr. 1 Program FormalPro

Pro návrháře na všech úrovních, kteří chtějí pracovat efektivně a bez omezení, nabízí firma Mentor Graphics, která má v této oblasti dlouholeté vedoucí postavení, celé spektrum vhodných softwarových nástrojů. Cílem tohoto článku je seznámit odbornou veřejnost alespoň stručně s těmito nástroji pro návrh a verifikaci FPGA a ASIC.

HDL Designer kombinuje schopnosti provádět detailní analýzu, pokročilé editory a management celého projektu, to vše vytváří výkonné návrhové prostředí HDL, které zvyšuje produktivitu jednotlivých návrhářů i návrhových týmů (lokálních i vzdáleně propojených) a umožňuje opakovatelný a předvídatelný návrhový proces.

2.jpg)

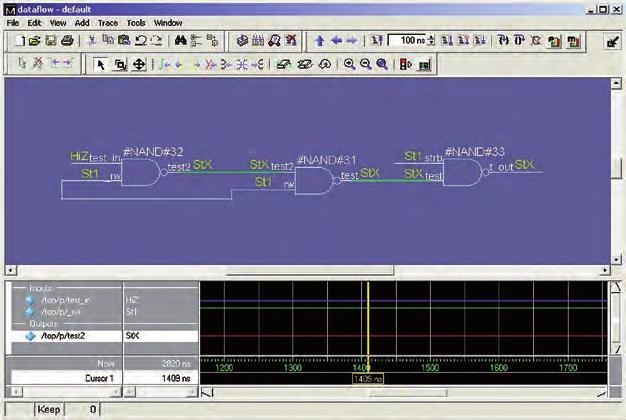

Obr. 2 Program ModelSim

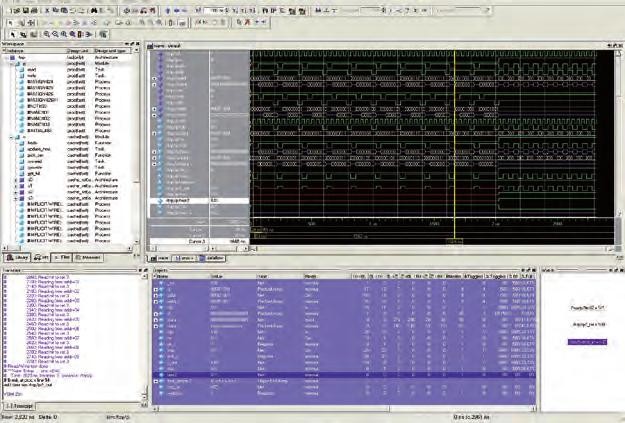

ModelSim je nejrozšířenější SW nástroj pro simulaci a verifikaci FPGA, zejména díky výkonu a optimálně integrovanému prostředí pro ladění a analýzu. Jeho architektura podporuje všechny standardní jazyky včetně VHDL, Verilog, SystemC, SystemVerilog a PSL, a to jednotlivě i v jejich kombinaci.

3.jpg)

Obr. 3 Program ModelSim

Precision RTL Plus je vlajková loď firmy Mentor Graphics pro syntézu FPGA, která disponuje mnoha jedinečnými funkcemi zejména pro aplikace komerční, letecké, vojenské a aplikace s extrémními požadavky na bezpečnost. Nejnovější verze zahrnuje například podporu pro Xilinx Virtex 7, Actel SmartFusion, Altera Stratix V a Cyclone IV E/GX, optimalizace aplikací s nízkým příkonem, bezpečnostní mód pro vojenské a letecké aplikace a aplikace s vysokými nároky na bezpečnost, integrace s nástrojem ReqTracer a šifrování IP.

Tyto nástroje slouží pro:

Questa je mocná platforma pro funkční verifikaci zahrnující verifikaci založenou na assertions, verifikaci řízenou sledováním pokrytí, automatizaci vytváření stimulů a testbenchů, přecházení mezi hodinovými signály a verifikaci IP jader. Simulátor nativně podporující všechny standardní jazyky, VHDL, Verilog, SystemVerilog, C, C++, SystemC (SCV a TLM) a PSL.

Precision Hi-Rel je nejnovější přírůstek do rodiny produktů Mentor Graphics pro syntézu FPGA, který zaručuje snížení výskytu soft chyb vyplývajících z jevů typu SEU (Single Event Upset) a SET (Single Event Transient) pro aplikace v letectví a tam, kde je vyžadována vysoká spolehlivost. Zahrnuje v sobě všechny pokročilé funkce z Precision RTL Plus.

ReqTracer řídí požadavky v návrhových tocích pro FPGA a ASIC. ReqTracer zjednodušuje, automatizuje a umožňuje trasování požadavků od specifikace hardware, přes kódování HDL, až po implementaci a validaci výsledku. Podporuje práci s požadavky pro certifikaci DO-254.

FormalPro je řešení vhodné pro výkonnou kontrolu ekvivalence pro regresní testování obvodů ASIC (FPGA) a IC se 100 000 a více hradly. FormalPro ověřuje s využitím techniky formální verifikace, zda je návrh ekvivalentní s referenčním („zlatým“) modelem.

Certe Testbench Studio nabízí výkonné a přehledné prostředí umožňující pohodlnou tvorbu testbenchů založených na UVM/OVM a SystemVerilog pro složité návrhy ASIC/FPGA.

Visual Elite nástroj postavený na silné infrastruktuře pro implementaci HDL, umožňující vytvářet nejpokročilejší mechanismy a koncepty pro modelování na systémové úrovni (electronic system level – ESL) a modelování na úrovni přechodů (transaction level modeling – TLM).

Vista je kompletní řešení založené na TLM 2.0 určené pro návrh architektury, analýzu, verifikaci a virtuální prototypování usnadňující systémovým architektům a návrhářům SoC rozhodování o architektuře a umožňující hardwarovým a softwarovým inženýrům ověřovat hardware a software.

Catapult C Synthesis je nástroj pro syntézu, který pracuje na vysoké, a tedy produktivnější, úrovni abstrakce. Umožňuje návrhářům ASIC a FPGA vyžívat průmyslové standardy ANSI C++ a SystemC k popisu funkce. Generuje RTL kód nejvyšší kvality.