Když dorazí z výroby první obvody nového zařízení, možnosti testování tohoto zařízení jsou omezené.

Technici zabývající se návrhem či validací si mohou pronajmout čas na drahém a složitém automatickém testovacím systému (ATE), který bude výhledově testovat čip i při výrobě. Druhou možností je složit potřebné vybavení z tradičních přístrojů a ověřit tak, zda vlastní obvod splňuje funkční požadavky návrhu.

Obě možnosti s sebou nesou určité problémy. V případě ATE nefunguje tradiční přístup digitálního testování, jelikož přístup k testovacím bodům systémů na čipu je omezený. Složitější zařízení vyžadují funkční testy spíše na systémové úrovni, což není silná stránka konvenčních ATE systémů. Tradiční stolní měřicí přístroje naproti tomu v systémových funkčních testech již dlouho excelují a v průběhu návrhu dávají relevantnější informace. Na druhou stranu je takřka nemožné dosáhnout stejné reakční doby v rámci cyklu nebo rychlosti testu vyžadované pro měřené zařízení.

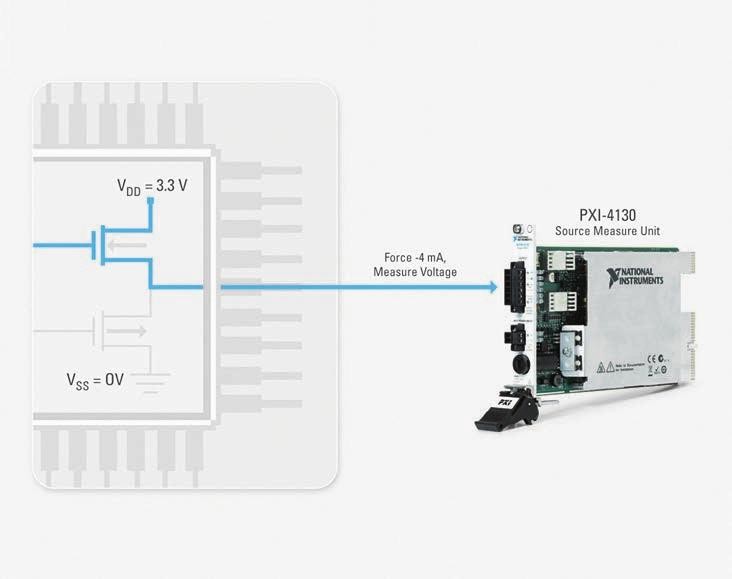

Obr. 1 Uživatelé mohou provádět běžné parametrické testy na platformě PXI tak, že pro přívod a měření napětí či proudu s vysokou přesností použijí jednotku SMU NI PXI-4130

Nedávný rozvoj platformy PXI a grafického návrhu systémů nabízí alternativu k těmto dvěma přístupům pro validaci polovodičových obvodů. Oblast využití softwaru NI LabVIEW se posunuje ještě blíže ke každému vývodu zařízení. Zatímco možnosti vysokorychlostních digitálních vstupů a výstupů platformy PXI v průběhu posledních let rostly a staly se srovnatelnými s elektronikou pro vývody v systémech ATE, schopnosti platformy v oblasti stejnosměrného napájení stagnovaly. Nový přesný měřicí zdroj (SMU) NI PXI-4130 představuje v této oblasti významný pokrok. Kombinace tohoto přístroje s vysokorychlostním přepínačem obsahujícím vysoký počet kanálů řeší většinu nejběžnějších problémů s parametrickým testováním. Grafický návrh systémů také představuje nejlepší způsob testování zařízení v jeho přirozeném prostředí. Moduly pro PXI s obvody programovatelných hradlových polí (FPGA) mohou častokrát předstihnout možnosti klasických testů typu hardware-in-the-loop i u těch nejvýkonnějších ATE systémů. Napomáhají abstrahovat nízkoúrovňové detaily čipu a zprostředkovat tak kompletní test funkcionality zařízení v podmínkách jeho očekávaného nasazení. Takové řešení se dnes nazývá „ATE se znalostí protokolu“ neboli ATE, který zná a emuluje předpokládané použití testovaného zařízení. PXI a LabVIEW jsou používány pro funkční verifikaci čipů stejným způsobem, jakým se dlouho verifikovaly řídicí jednotky motorů – při reakcích na jejich přirozené prostředí.

Před kontrolou reakce na příslušný podnět je proveden soubor měření, která prověří výrobu samotného zařízení. To často zahrnuje kontrolu výkonu CMOS tranzistorů a ochranných diod, celkového proudového odběru a ztrát. Tyto testy se často označují jako „parametrické“ testy a zahrnují stejnosměrné i střídavé charakteristiky. Pro stejnosměrná měření jsou potřebná zařízení jako parametrická měřicí jednotka (PMU) či přesný měřicí zdroj (SMU). Používají se k přivádění a měření proudu a napětí na jednotlivých vývodech čipu.

PXI-4130 je programovatelný měřicí zdroj s vysokým výkonem, který má podobu PXI modulu o velikosti 3U zabírající 1 pozici v PXI skříni. Modul má jeden izolovaný SMU kanál, který nabízí napěťový výstup ±20 V se vzdáleným (4vodičovým) snímáním. S pěti proudovými rozsahy, které nabízejí rozlišení zdroje a měření až 10, resp. 1 nA, dokáže tento přesný přístroj provádět většinu ze standardních stejnosměrných parametrických testů, které polovodičová zařízení potřebují. Mimo jiné jde o následující:

Mnoho z těchto testů používá testovací sekvenci podobnou následující (pro VOH):

1. Uvedení zařízení do stavu output-high

2. Přivedení proudu − 4 mA ze SMU (SMU se chová jako zátěž)

3. Změření výsledného napětí na výstupním vývodu – je vyhodnocena chyba, pokud je menší než 2,4 V

Dalším klíčovým požadavkem na stejnosměrná měření je vysokorychlostní přepínací modul s dlouhou životností pro připojení SMU ke každému vývodu. Nedávno představené maticové moduly NI PXI-2535 a PXI-2536 s 544 uzly a tranzistory FET mohou SMU PXI-4130 připojit ke stovkám testovacích bodů a přepínat s rychlostí až 50 000 cyklů za sekundu. Protože tento přepínač používá technologii FET a nemá žádné pohyblivé části, má takřka neomezenou životnost – to je klíčová vlastnost pro výrobní systém či odolnou validační stanici.

Tyto produkty doplňují platformu PXI o důležité vlastnosti požadované pro parametrická měření. Jakmile jsou provedeny parametrické testy, pokračuje validace čipu obvykle funkčními testy. Pro jednoduché digitální zařízení mohou probíhat tak, že jsou na obvod aplikovány různé testovací vektory, které prověří celou pravdivostní tabulku, a současně jsou kontrolovány odpovídající výstupy. S tím, jak se zařízení stávají složitějšími, například v podobě systému na čipu, mají funkční testy stále omezenější přístup k jednotlivým komponentám a stále častěji vyžadují komunikaci s obvodem na vyšší úrovni. Je při testování mikrokontroléru lepší aplikovat testovací vektory se správným časováním a měřit odezvu, nebo jej prostě nastartovat a spustit na něm nějaký kód? Test obvodu se tak stává spíše testem osazené desky, čímž se přibližuje více k funkčnímu testu systému.

V případě mikrokontroléru nebo v případech, kdy komunikace s čipem probíhá prostřednictvím protokolů jako SPI či I2C, musí být tester schopen přijímat a odesílat příkazy na zařízení inteligentně a komunikovat s ním v obou směrech. Nejjednodušším vyjádřením je, že tester by měl emulovat prostředí okolo obvodu a testovat zařízení v souladu s jeho zamýšleným použitím (někdy též nazýváno mission mode). Je to víc než jen pouhý seznam vzorů pro generování očekávaných výsledků. Jde spíše o rozhodování a reagování v závislosti na vzorech, které tester dostává. Často je nutné provést rozhodnutí v rámci jednoho časovacího cyklu zařízení. Ačkoliv existují protokolové testery v podobě stolních přístrojů, pro takovou úroveň interakce je potřebné sofistikovanější řešení.

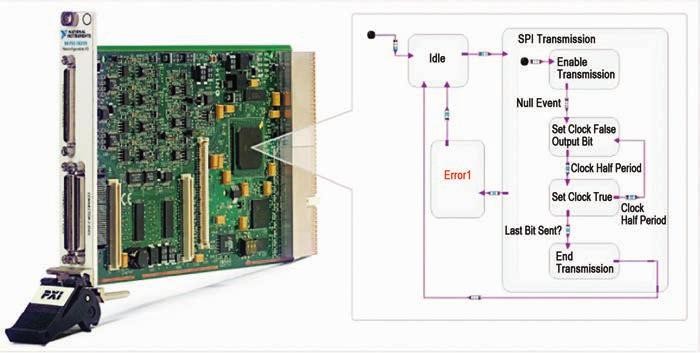

Obr. 2 Jak se polovodičová zařízení stávají stále složitějšími, začíná se metoda pro jejich podrobnější testování více podobat funkčnímu testu systému namísto testu obvodu.

Andrew Evans nedávno publikoval článek s názvem „The New ATE – Protocol Aware" u příležitosti konference International Test Conference (ITC) ve městě Santa Clara v Kalifornii. V něm vyzval výrobce obvodů a dodavatele testovacích systémů, aby spolupracovali na vyřešení tohoto problému. Jeden úryvek říká: „Chybějícím prvkem je programovatelná logika, která by se použila pro emulaci. Tato logika by primárně měla podobu FPGA a nacházela by se mezi elektronikou ATE pro vývod a zbytkem vývodu ATE, který představuje paměť vektorů, generátory vzorů, časování a formátovače.“

Grafický návrh systémů představuje intuitivní metodologii pro simulaci přirozeného prostředí zařízení v FPGA; uživatelé mohou graficky navrhnout systém okolo obvodu a emulovat tak jeho okolí. Jako příklad zvažte implementaci komunikace SPI s použitím LabVIEW Statechart Module a LabVIEW FPGA pro modul NI PXI-7831R řady R. Implementace komunikace přes SPI do obvodu FPGA umožňuje reakci v rámci jednoho cyklu při obousměrné komunikaci s čipem.

Jednou z možností, jak mohou uživatelé rozdělit časovací diagram SPI na jednotlivé stavy stavového automatu, je:

1. Nastavit ChipSelect na low

2. Nastavit Data (0)

3. Nastavit Clock na high

4. Nastavit Clock na low

5. Nastavit Data (1)

6. Nastavit Clock na high

7. Nastavit Clock na low

8. Opakovat Data a Clock pro bity 2 až 15

9. Nastavit ChipSelect na high

Tento příklad obsahuje pět jedinečných kroků, z nichž některé se opakují pro každý datový bit. Obrázek 3 ukazuje stavový diagram LabVIEW pro zařízení v roli master neboli v tomto případě digitální vývod testeru. Každý z výše uvedených kroků je ve stavovém diagramu rozdělen do pěti stavů. Každý stav odpovídá nastavení jedné z digitálních linek, které vedou z FPGA.

Obr. 3 LabVIEW Statechart Module reprezentuje komunikaci SPI grafickým způsobem a usnadňuje nasazení kódu na FPGA pro reakce v rámci jednoho cyklu a intuitivní způsob hledání chyb.

Se stavovými diagramy a grafickým návrhem systémů mohou uživatelé vytvářet systémy tak, že nadefinují stavy, přechody a události. Při hledání chyb mohou uživatelé zobrazit chyby podle místa jejich výskytu – stavu, přechodu či události, při které se vyskytly – a to v grafické podobě. To je podobné, jako když vývojáři softwaru upřednostňují ladění ve vysokoúrovňovém jazyku namísto prohlížení kódu ve strojovém jazyku, což by byla obdoba testovacích vektorů. Po vytvoření mohou uživatelé nasadit stavové diagramy z LabVIEW přímo na cílový systém PXI FPGA, který komunikuje s testovaným zařízením. Tímto způsobem mohou dosáhnout komunikace pro každý digitální vývod.

Měřicí zdroj PXI-4130 a přepínače PXI- 2535/36, spolu s technologií FPGA, přinášejí sílu LabVIEW blíže k samotným vývodům čipu. Umožňují provádět parametrické a funkční validační testy intuitivním, a přitom velice výkonným způsobem. Využijte tyto technologie pro stavbu validačního systému pro polovodiče, který v sobě spojuje ty nejlepší vlastnosti stolních a automatických výrobních testovacích systémů.

Luke Schreier je manažer skupiny NI pro přesné stejnosměrné a digitální testy. Má bakalářské vzdělání v oboru strojního inženýrství z University of Nebraska – Lincoln.

Více informací o National Instruments je k dispozici na http://czech.ni.com, nebo na ni.czech@ni.com.