Metody interní komunikace mezi HPS a FPGA

Úvod

Minulá část článku popisovala možnosti konfigurace obou částí Altera SoC – procesorové části HPS a části hradlového pole FPGA. Dnešní pokračování se zaměří na metody komunikace mezi těmito bloky.

Možnosti interní komunikace mezi HPS a FPGA

Architektura Altera SoC počítá s různými scénáři komunikace mezi procesorovou částí a periferiemi implementovanými v FPGA. Nejjednodušší formou komunikace je signalizace pomocí 32 linek pro obecné použití v každém směru (obdoba běžných GPIO), které jsou HPS přístupné přes registry bloku FPGA Manager.

Další možností je přesměrování některého ze standardních komunikačních rozhraní HPS z externích pinů do FPGA. Toto je možné např. u Ethernetu, UARTu, I2C nebo SPI rozhraní. Tato možnost je k dispozici spíše proto, aby HPS mohlo využít piny FPGA a v některých případech může usnadnit přechod ze starších systémů, kde bylo FPGA a procesor v samostatných pouzdrech, bez nutnosti zásadních uprav jak IP modulů, tak i softwaru.

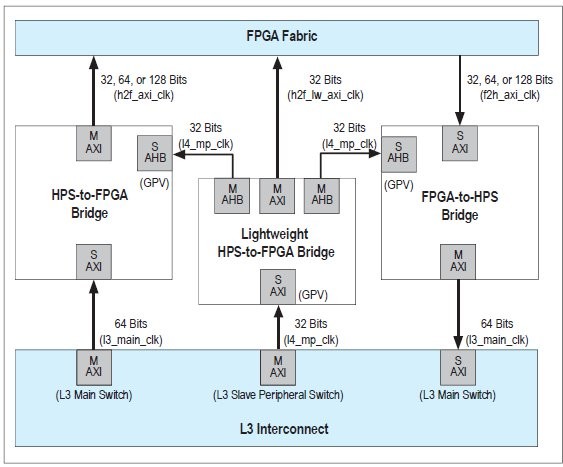

Obr. 1 Propojení tří interních sběrnic mezi HPS a FPGA

Většina periferií však vyžaduje komplexnější komunikaci. Obrázek 1 ukazuje propojení tří interních sběrnic mezi HPS a FPGA, které jsou pro tento typ komunikace určeny. Společným rysem těchto sběrnic je použití protokolu AMBA AXI3. Blok Lightweight HPS- -to-FPGA Bridge je připojen do FPGA svým master portem, přenosy na této sběrnici (dále LwAXI) jsou tedy řízeny HPS. Primárně je LwAXI určena pro „pomalé“ přenosy, zejména pro přístup k bankám řídicích registrů periferií. Šířka sběrnice je 32 bitů a dostupný adresový prostor je 2 MB. Master interface je taktován hodinovým signálem dodávaným uživatelem z FPGA, který je zcela nezávislý na hodinovém taktu HPS. Bezpečný přechod mezi časovými doménami je zajištěn interní logikou výše zmíněného bridge. Tato vlastnost je společná i sběrnicím popsaným v následujících odstavcích. Do systému je bridge propojen 32bitovým portem taktovaným na l4_mp_clk, které běží nejvýše na polovině kmitočtu hodin jádra HPS.

Pro rychlé přenosy jsou určeny sběrnice poskytované bloky HPS-to-FPGA Bridge a FPGA-to-HPS Bridge. Na rozdíl od LwAXI mají konfigurovatelnou šířku datové sběrnice (32, 64 nebo 128 bitů) a jejich adresový prostor je téměř 1 GB. Dalším rozdílem je rychlejší připojení do systému pomocí 64bitového portu taktovaného na poloviční frekvenci procesoru. Tím je také určena maximální teoretická přenosová rychlost propojení. Vzájemně se tyto sběrnice liší pouze tím, že HPS-to-FPGA Bridge poskytuje FPGA master port, stejně jako LwAXI, kdežto FPGA-to-HPS Bridge poskytuje slave port. Umožňuje tak připojení periferie, která sama řídí provoz na sběrnici bez jakékoliv spolupráce s procesorem a může nezávisle přistupovat k periferním zařízením HPS (např. používat jeho I2C rozhraní) a do pamětí HPS.

Z hlediska softwaru, který používá periferie připojené k těmto sběrnicím, je důležité, aby bylo zajištěno, že FPGA je v době přístupu k těmto sběrnicím již řádně nakonfigurováno a spuštěno. V opačném případě nebude přístup nikdy dokončen a software havaruje. Stejná situace může nastat při změně konfigurace FPGA za běhu HPS. Vždy je nutné sběrnice nejprve deaktivovat v konfiguračních registrech a znovu je aktivovat až po dokončení konfigurace. Deaktivace a aktivace může byt provedena kdykoli a je pro ni podpora jak v zavaděči U-Boot, tak v OS Linux.

Sběrnice popsané v předchozích odstavcích poskytují jak komfortní přístup procesorového jádra HPS k datům poskytovaným periferiemi v FPGA, tak i přístup opačným směrem, tedy autonomním periferiím do celého paměťového prostoru HPS a pokryjí tak velkou část potřeb na předávání informací mezi HPS a FPGA.

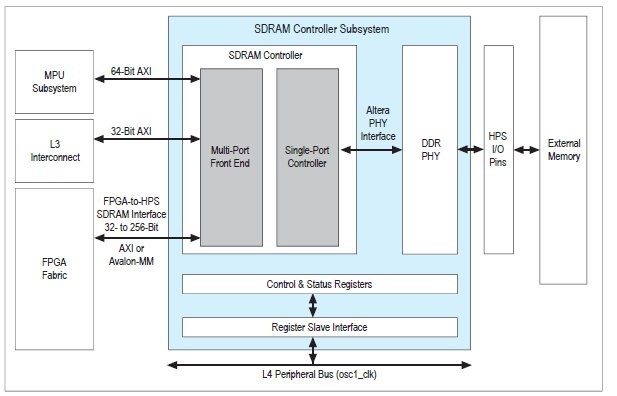

Obr. 2 Postup inicializace HPS programem v BOOT ROM

Představme si nyní případ, kdy je potřeba pravidelně přenášet velké množství dat z FPGA do hlavní paměti HPS (tedy nejspíše DDR SDRAM) – např. data přijatá z kamery. Periferie se bude chovat jako master, použijeme tedy FPGA-to-HPS Bridge. Data musí nejprve projít tímto bridgem, pak procházejí propojovacím blokem L3 Interconect, kde může dojít ke kolizi s toky mezi ostatními periferiemi, a teprve potom data prochází do řadiče paměti (přes 32bitový kanál), kde je další možnost kolize s přístupy z jádra HPS, a do paměti samotné. Přenos na jedné straně ovlivňuje fungování systému, na straně druhé může být zpomalen jinými přenosy. V této situaci je výhodné použít SDRAM2FPGA bridge, který přímo propojuje řadič pamětí SDRAM a FPGA. Obrázek 2 ukazuje řadič paměti SDRAM. SDRAM2FPGA bridge je zde reprezentován spojnicí označenou FPGA-to-HPS SDRAM Interface.

Tento bridge je vysoce konfigurovatelný, nabízí 4 porty (64 bit) pro čtení, 4 porty (64 bit) pro zápis a 6 řídicích portů. To umožňuje použít např. až 6 jednosměrných sběrnic (4 čtení, 2 zápis) s protokolem Avalon-MM, 3 obousměrné AXI sběrnice nebo jednu 256bitovou sběrnici pro zápis a jednu 256bitovou sběrnici pro čtení (výčet konfigurací není kompletní a zachycuje typické případy). Bridge je opět schopen zajistit přechod z libovolné časové domény, periferie mohou pracovat na libovolných kmitočtech. Šířka sběrnice 256 bitů umožňuje dosáhnout nejvyšší komunikační rychlosti s připojenými pamětmi.

Do přenosů přes toto rozhraní je zapojen pouze řadič paměti. K ovlivnění fungování HPS tak dochází pouze sdílením přenosové rychlosti paměti.

Omezujícím faktorem při použití tohoto rozhraní je způsob jeho inicializace. Na rozdíl od předchozích rozhraní, kde jejich nastavení bylo dáno pouze konfiguračními registry, nastavení SDRAM2FPGA bridge je dáno signály přicházejícími z FPGA, které jsou uvedeny do správného stavu až konfigurací FPGA. Okamžik, kdy jsou řídicí signály vzorkovány a kdy je fakticky rozhraní nakonfigurováno, je možné řídit softwarově a kdykoli opakovaně vyvolat. Omezující podmínkou je, že vše musí nastat v době, kdy je řadič paměti zcela nečinný. To znamená, že neprobíhají žádné transakce na žádném z jeho portů. Takový stav je složité navodit v době běhu operačních systémů, jako je Linux, kde transakce od řadiče paměti cache, DMA kanálů nebo periferií mohou nastat kdykoli. Prakticky je možné nastavení korektně provést pouze při inicializaci v zavaděči U-Boot, kdy není problém zavést konfiguraci do FPGA. V této době běží pouze jedno jádro, periferie jsou pod kontrolou a je možné běh programu dočasně relokovat z externí SDRAM do vnitřní paměti. V tomto klidovém stavu může být bridge bezpečně inicializován. Při dodržení shodných hlavních parametrů (tj. počet portů, protokoly a šířky sběrnic) je již možné bridge deaktivovat, změnit konfiguraci FPGA a znovu bridge aktivovat kdykoli, i za běhu operačního systému.

Závěr

Dnešní díl článku shrnul možnosti interní komunikace obvodů Altera SoC, tedy komunikace mezi procesorovou částí HPS a částí hradlového pole FPGA. V příštím díle popíšeme připojení jednoduché periferie ke sběrnici LwAXI.