Nároky na zpracování informací a algoritmická složitost neustále rostou. Tento trend je patrný nejen ve výpočetní technice, ale i u komerčních zařízení, která zpracovávají velké objemy dat pomocí složitých algoritmů. Převážně se jedná o zařízení zpracovávající video signál, datové a telekomunikační spoje, realtimové řídicí systémy, medicínské aplikace a v neposlední řadě i komponenty pro automobily.

Zákazníci požadují vyšší výpočetní výkon a flexibilitu obvykle za srovnatelnou nebo nižší cenu oproti předcházejícím verzím systému. Alternativou mohou být systémy platforem SoC (System on Chip) implementované v hradlových polích typu FPGA.

Evoluční vývoj struktur SoC postupně ukázal některé přístupy a řešení dané problematiky. První systémy byly obvykle konstruovány na bázi tzv. soft-core jader. To znamená, že veškerá funkcionalita je tvořena pomocí prostředků ve struktuře hradlového pole (propojovací síť, kombinační a sekvenční logika, vstupy a výstupy) bez další hardwarové podpory uvnitř FPGA. Takto koncipované řešení má celou řadu výhod, kdy je řešení plně v režii návrháře, a obecně lze říci, že nedochází k plýtvání zdrojů v FPGA. Nevýhodou je, že vlastní řešení obvykle nedosahuje optimální pracovní rychlosti, sestavování výsledného designu je časově náročné a spotřebovává větší množství prostředků FPGA.

Druhým přístupem je doplnění struktury hradlového pole o další funkční bloky. V prvopočátcích se jednalo o blokové paměti, moduly zpracovávající hodinové signály (DCM, PLL) a DSP bloky. Modernější hradlová pole byla doplňována o složitější bloky, jako jsou PCI Express a paměťové řadiče, MAC bloky, rychlé transceivery a procesorová jádra. Tento koncept vyžadoval využití interních prostředků FPGA, kdy pro připojení procesoru k paměti byla spotřebována významná část zdrojů FPGA. Tento koncept byl v posledních letech nahrazen novým přístupem, kdy v FPGA nezávisle existují procesor a logická síť. Tento koncept je patrný v rodinách FPGA řady Zynq od společnosti Xilinx a SoC od společnosti Altera. Dnešní článek se bude věnovat popisu platformy SoC od společnosti Altera.

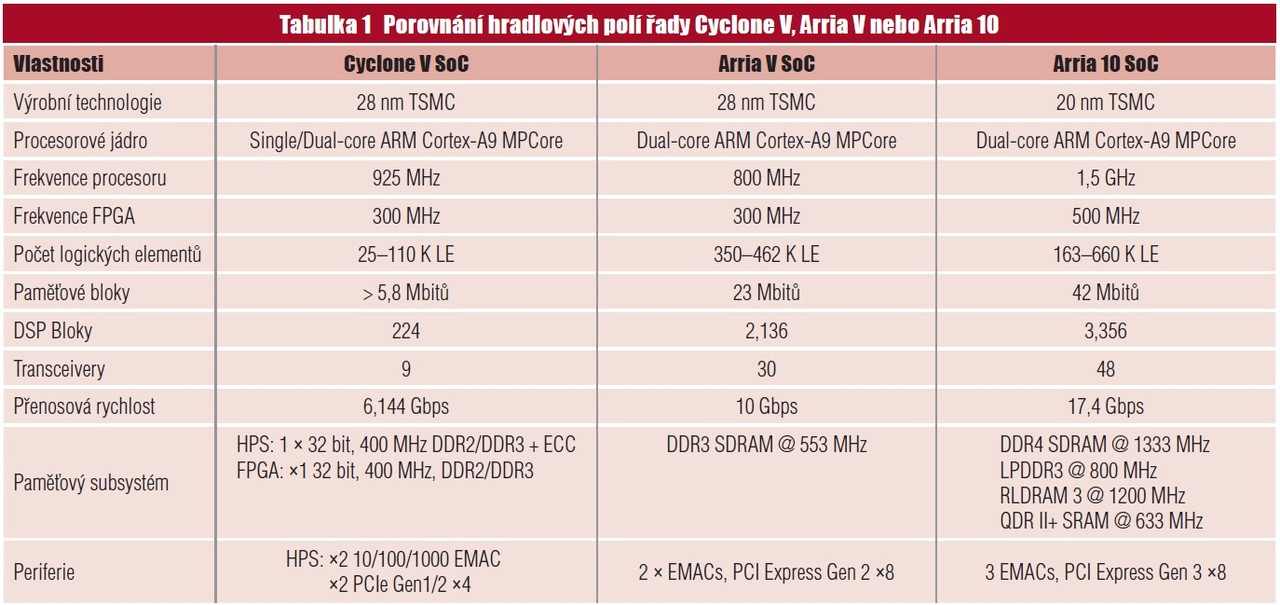

Základním stavebním prvkem obvodu SoC je jedno- nebo dvoujádrový procesor rodiny ARM Cortex A9 označovaný jako HPS (Hard Processor System) a hradlové pole řady Cyclone V, Arria V nebo Arria 10. HPS je vybaven vlastními periferními zařízeními, od základních sériových rozhraní (I2C, SPI, CAN, USB) přes řadič pamětí až po gigabitový ethernetový MAC. Maximální pracovní frekvence procesoru se pohybuje od 667 MHz do 1GHz dle rychlostní třídy obvodu. Hradlová pole využitá v SoC jsou rozdělena do tří skupin. První skupinou jsou pole rodiny Cyclone V určené pro aplikace s požadavky na nejnižší cenu. Řada Cyclone V se dělí na tři dílčí podskupiny, a to SE – určená pro obecné aplikace včetně DSP aplikací, SX – určená pro datové komunikace a embedded PCI Express aplikace. Poslední podskupinou je řada ST, která je určena pro výkonnější komunikace a PCI Express aplikace do pracovní frekvence 6,144 Gbit/s na transceiver. Střední řada je založena na FPGA Arria V a Arria 10 a je určena především pro medicínské aplikace, digitální rádio a komunikace v rozsahu od 40 do100 Gbit/s. Samozřejmostí je vybavení rychlými transceivery, rozhraním PCI Express ve verzi Gen 2 4× a 8×. V neposlední řadě stojí za zmínku i DSP bloky dosahující ekvivalentního výkonu od 100 do 2 600 GMAC. Uspořádání platformy SoC je na obr. 1.

Obr. 1 Blokové schéma obvodu řady SoC Altera

Důležité je upozornit na fakt, že piny obvodu jsou rozděleny na dvě hlavní skupiny. Do první skupiny patří vstupně výstupní piny procesoru. Tyto piny nejsou přímo ovládané z FPGA, byť za jistých okolností existuje cesta, jak s těmito piny pracovat. Druhá skupina pinů patří hradlovému poli. Hradlové pole podporuje široké spektrum standardů (LVCMOS, LVTTL, SSTL, HSTL) v napěťových úrovních od 1,2 do 3,3 V včetně diferenciálních standardů LVDS a RSDS. Vstupně výstupní piny jsou doplněny o rozšiřující konfigurovatelné funkce typu pull-up/down, sériovým nebo paralelním zakončením, řízením výkonu proudového výstupu a dalšími funkcemi zlepšujícími signálovou integritu.

Vnitřní komunikace mezi procesorem a hradlovým polem je zajištěna pomocí víceportového rozhraní sběrnice AMBA – AXI v 32-, 64- nebo 128bitové verzi. Porty jsou rozděleny na porty s vysokou propustností, obecné porty a porty pracující s pamětí.

Konfigurace obvodu je flexibilní a umožňuje nezávislou inicializaci jak procesoru, tak hradlového pole. Procesor lze konfigurovat z paměti SPI, SD/MMC karty nebo paměti NAND. Konfigurace hradlového pole probíhá z paměti typu SPI, paralelní paměti nebo sběrnice PCI Express. Uživatel si může vybrat, zda konfigurace bude šifrovaná, či nikoliv.

Stručný úvod popsal hardwarové prostředky architektury SoC Altera. Komplexnost celého řešení klade vysoké nároky na softwarové vybavení. Je tře ba si uvědomit, že neobsluhujeme pouze procesor, ale celou infrastrukturu hradlového pole a periferních zařízení. Nezbytností pro rychlý a kvalitní vývoj jsou softwarové nástroje a balíčky. Pro procesor ARM je k dispozici ladicí nástroj DS-5, zaváděč U-boot, operační systém Linux, Windows CE a široká podpora realtimových systémů. Vývoj softwaru nemusí probíhat přímo v obvodu SoC, ale na virtualizovaných platformách emulujících procesor Cortex A9.

Vývoj aplikací hradlového pole a jeho periferních zařízení primárně probíhá ve vývojovém prostředí Quartus a Qsys. Samozřejmostí je podpora široké škály IP funkcí (od řadičů pamětí, uživatelských periferních zařízení až po zpracování vícerozměrných signálů), jazyka VHDL a Verilog až po OpenCL. Nástroje disponují podporou pro částečnou dynamickou rekonfiguraci FPGA.

Platformy SoC kombinující procesor a hradlové pole nacházejí v posledních letech široké uplatnění v automobilovém průmyslu, medicíně, vojenské technice, ale i ve spotřebním zboží. V současné době existuje několik variant uspořádání architektury SoC, obvykle s procesory PPC a ARM. V příštích pokračováních seriálu se zaměříme na detailnější popis architektury SoC rodiny Cyclone V.