Na každodenní novinky v oblasti elektronických zařízení jsme si v poslední době zvykli tak, že nás prakticky nic nepřekvapí. Elektronika je v dnešní době všudypřítomná a málokoho dnes udiví stále dokonalejší komunikační zařízení, telefony, počítače a takto bychom mohli pokračovat v nekonečném výčtu elektronických zařízení, která používáme v každodenním životě. Všechny tyto aplikace by však neexistovaly, nebýt neustálého zdokonalování výrobních polovodičových technologií, které se vyvíjejí v skrytu uzavřených hal několika elektronických gigantů. Přitom vynález integrovaného obvodu před dvěma lety oslavil teprve padesát let! V tomto článku se podíváme na moderní trendy ve výrobních technologiích v oblasti křemíkových integrovaných obvodů.

Obr. 1 V roce 1958 Jack Kilby z Texas Instruments zkonstruoval první integrovaný obvod. Měl 1 tranzistor a 4 odpory na čipu. V roce 2000 byla panu Kilbymu udělena za tento vynález Nobelova cena. Zdroj: Texas Instruments

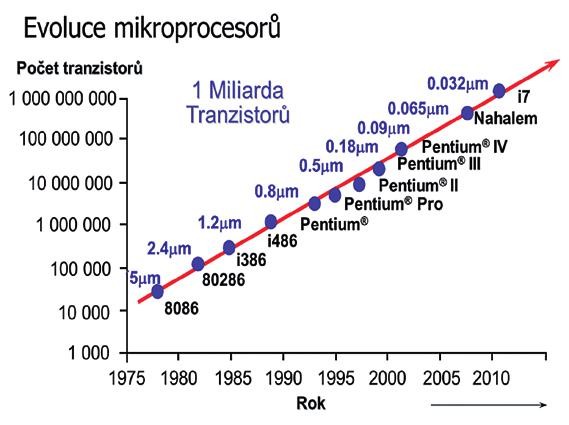

Vše začalo před padesáti lety, když Jack Kilby z Texas Instruments přišel s myšlenkou, jak realizovat integraci více tranzistorů na jeden čip (obr. 1). Vývoj nejdříve postupoval relativně pomalu a tak hustota integrace na začátku osmdesátých let byla jen několik tisíc tranzistorů na jednom čipu. Vývoj hustoty integrace, kterým se již přes 40 let řídí polovodičový průmysl, se nazývá Moorův zákon, který formuloval v roce 1965 jeden ze zakladatelů firmy Intel, Gordon Moore. Tehdy pan Moore předpověděl, že každých 18 měsíců bude zdvojnásoben počet tranzistorů na čipu a též bude zdvojnásoben jejich spínací kmitočet (obr. 2). Zákon dlouho platil jako neměnná a nezpochybnitelná definice rozvoje polovodičového průmyslu a v jistém smyslu platí až dodnes.

Obr. 2 Evoluce mikroprocesorů Intel. První mikroprocesory měly kolem 1000 tranzistorů na čipu a taktovací frekvenci 108 kHz. Dnes mají mikroprocesory kolem jedné miliardy tranzistorů s taktovací frekvencí přes 3 GHz.

Současné submikronové CMOS (Complementary Metal Oxide Semiconductor) technologie jsou stále vylepšovány díky vývoji výroby planárních integrovaných struktur. Nové technologie umožňují další škálovatelnost rozměrů tranzistorů. Dnes se stále daří technologicky držet trend zmenšování rozměrů elektronických komponent na čipu. Hlavní výhodou je zvyšování spínací rychlosti tranzistorů, snižování spotřeby a úspora obsazeného místa na čipu. Rozměry elektronických součástek (tranzistorů) se dnes v nejvyspělejších technologiích vyrábějí pomocí 32nm technologického procesu a dokáží integrovat více než jednu miliardu elektronických součástek na jeden polovodičový čip.

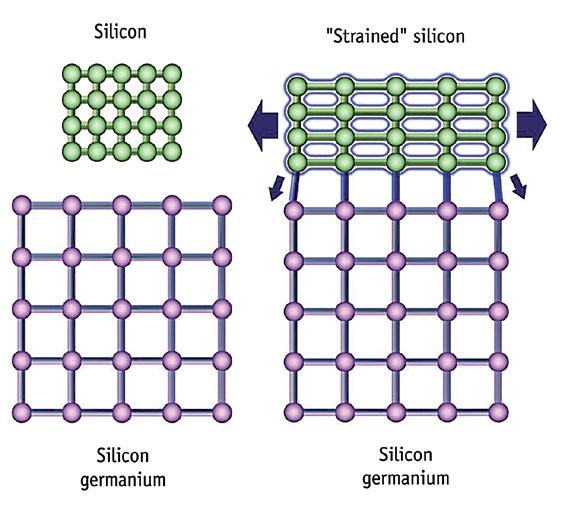

Neustálé zmenšování velikosti tranzistorů (délky kanálu) s každou novou technologickou generací přináší kromě zrychlení a větší hustoty integrace řadu nových problémů při výrobě a mnoho neblahých efektů ve funkci tranzistorů („horké“ nosiče, podprahové proudy atd.). Dnes se vynakládají mnohamiliardové investice do vývoje a hledání nových technologických metod, pomocí kterých bychom dosáhli rychlejších spínacích vlastností tranzistoru, aniž by bylo nutno zkracovat délku hradla tranzistoru. Jelikož spínací rychlost tranzistoru je přímo úměrná pohyblivosti nosiče náboje (elektrony a díry), bylo by jedním z možných řešení použití materiálů s vyšší pohyblivostí náboje. Takové materiály jsou dnes relativně dobře dostupné (například GaAs nebo InP). Bohužel tyto materiály nejsou vhodné pro velkoobjemovou výrobu. Proto se výrobci elektronických čipů snaží stále držet křemíkových technologií. V posledních letech se daří nalézat řešení především v modifikaci vlastností křemíkového substrátu. Jednou z takových možností je využití principu nataženého křemíku (Strained Silicon), která již byla zavedena v komerčních 45nm a 32nm výrobních procesech. Základní myšlenka je založena na změně vnitřní struktury monokrystalického křemíku. Při mechanickém natažení křemíkového monokrystalu dojde ke zvýšení pohyblivosti elektronů v krystalové mřížce a tím i spínacích rychlostí tranzistoru.

Obr. 3 Princip technologie předepjatého křemíku

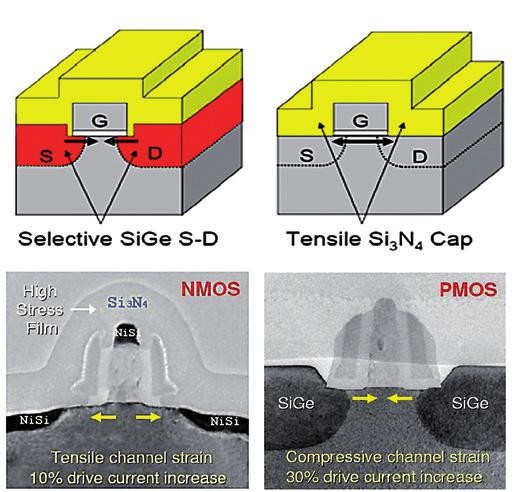

Otázkou je, jak mechanicky napnout aktivní vrstvu křemíku ve vodivostním kanálu tranzistoru. Při růstu dostatečně tenké vrstvy monokrystalického křemíku na vrstvě SiGe, dochází ke změně mřížkové konstanty krystalu křemíku, která roste s mřížkovou konstantou podkladové vrstvy (obr. 3). Uvedený jev je možný pouze u skladby materiálů s rozdílem mřížkových konstant do cca 4 %. Jelikož samotný křemík má mřížkovou konstantu (a=5,42 Å) menší než SiGe, dojde k natažení vazby mezi sousedními atomy křemíku a částečně také dochází ke stlačení v rovině kolmé k rozhraní mezi křemíkem a SiGe. V tomto případě budeme mluvit o tzv. napnutí ve dvou směrech (biaxial strain). Pro zvýšení pohyblivosti děr je účinnější komprese a u elektronů natažení. Proto je nutná jiná technologie pro PMOS a NMOS tranzistor. Pro dosažení nejlepšího výkonu se oba typy tranzistorů optimalizují separovaně. Na obr. 4 je zachycena struktura PMOS a NMOS tranzistoru s indikovaným směrem natažení křemíkové vrstvy. Celkové snížení spínací doby tranzistoru je přibližně 17 %. Přibližný nárůst finančních prostředků na zavedení této technologie jsou pouhá 2 %.

Obr. 4 Struktura NMOS a PMOS při jednoosém natažení

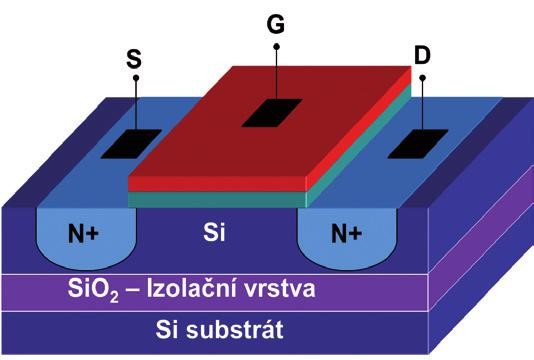

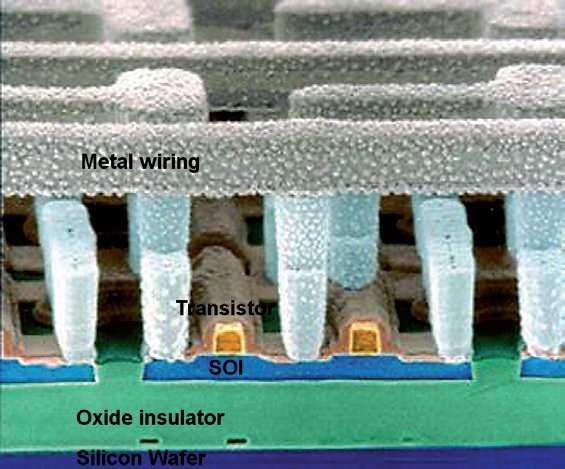

Největším omezením klidové spotřeby čipů jsou svodové proudy a omezujícím faktorem spínací rychlosti jsou parazitní kapacity tranzistorů. S rostoucím počtem tranzistorů na čipu by klidová spotřeba rostla na neúnosnou mez. Proto byla v technologiích pod 90 nm aplikována technologie SOI (Silicon On Insulator), která se tak stala alternativou ke klasickému objemovému CMOS procesu. Technologie SOI má oddělenou aktivní vrstvu polovodiče od substrátu pomocí izolační vrstvy SiO2 (obr. 5). Touto dnes jednoduchou úpravou dosáhneme řady vynikajících vlastností. Především nárůstu výkonu tranzistorů díky odstranění parazitních substrátových kapacit. Dále umožňuje funkci tranzistorů při menším napájecím napětí, zamezuje svodovým proudům do substrátu, má vyšší hustotu integrace, snižuje ztrátový výkon a navíc je možné dosahovat vyšší provozní teploty čipu. Nevýhodou této technologie je horší odvod tepla a mírný nárůst nákladů na výrobu křemíkových plátků (3 až 10 %).

Obr. 5 Řez tranzistorem CMOS SOI. Mezi substrátem a aktivní vrstvou tranzistoru je umístěna izolační vrstva. Nejčastěji se používá SiO2

Obr. 6 Silicon On Insulator pro čipy PowerPC. Zdroj: IBM

Další významnou novinkou používanou v posledních letech je technologie SSOI (Strained Silicon On Insulator), která kombinuje výhody technologie napnutého křemíku a křemíku na izolantu (SOI). V dnešní době jsou používány technologie SGOI a SSOI, tzv. první a druhá generace. V technologii SGOI je mezi vrstvou předepnutého křemíku a izolační vrstvou napínací vrstva SiGe, zatímco v případě SSOI leží vrstva předepnutého křemíku přímo na izolační vrstvě. Někdy bývá tato technologie označována jako SSDOI (Strained Silicon Directly On Insulator).

|  |

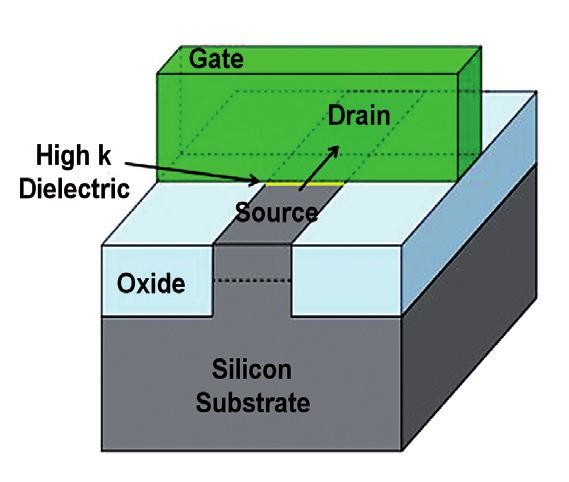

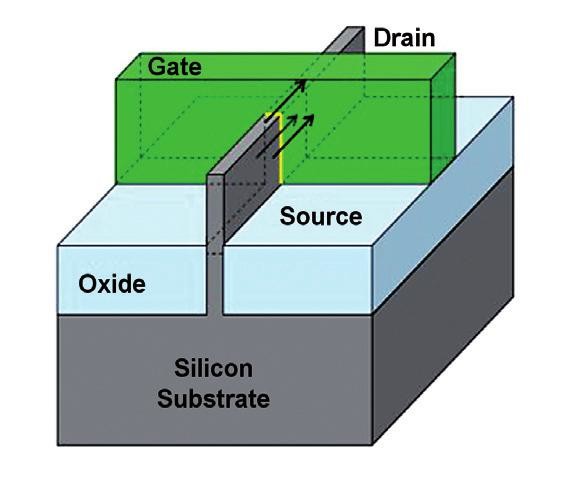

| Obr. 7 Planární tranzistor v 32nm technologii. Zdroj: Intel | Obr. 8 22nm tříhradlový transistor (3-D Tri Gate). Zdroj: Intel |

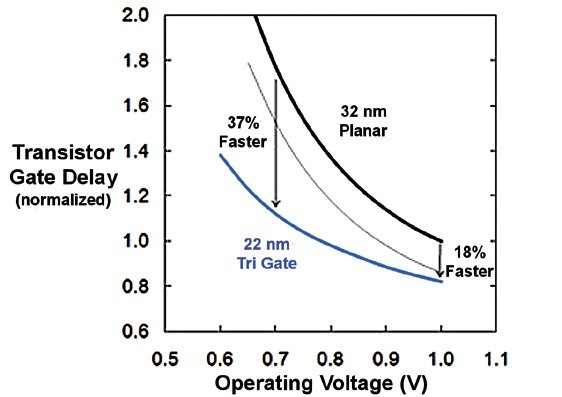

Obr. 9 Nové tříhradlové tranzistory vykazují až o 37 % lepší spínací vlastnosti. Zavedení do výroby se odhaduje na polovinu roku 2012. Zdroj: Intel

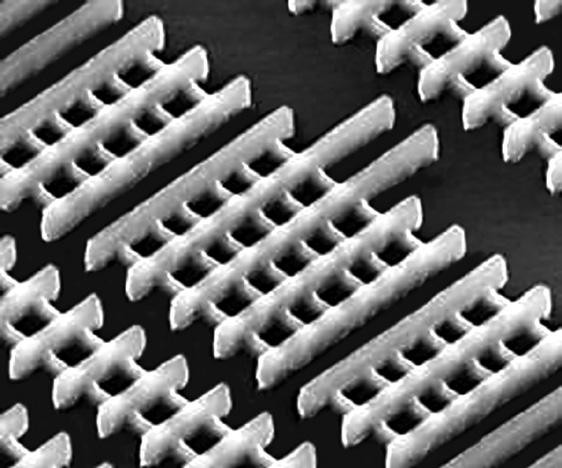

V květnu tohoto roku představila firma Intel přelomovou novinku nových typů tranzistorů, tzv. 3-D Tri-Gate tranzistory, které budou v první fázi vyráběny 22nm výrobním procesem. Současné tzv. planární tranzistory (obr. 7) mají kanál vedoucí elektrický proud pod rovinným hradlem. Nové tranzistory mají vodivostní kanál i hradlo trojrozměrné (obr. 8). Tato modifikace přináší nejen menší rozměry tranzistoru, ale také vylepšení ztrát energie až o 50 % a zvýšení spínacích rychlostí tranzistorů (obr. 9). Obrovské výhody této technologie jsou vykoupeny jen o cca 3 % vyššími výrobními náklady.

Obr. 10 Fotografie tříhradlových tranzistorů. Zdroj: Intel

Rozsáhlý vývoj technologií integrovaných polovodičových struktur dovolil v posledních několika letech překročit mnohá dříve nemyslitelná technologická omezení a zajistit tak profesionální i spotřební elektronice využívání vyšších výkonů, umožnil značnou miniaturizaci zařízení při snížené spotřebě. Mnohé aplikace moderních polovodičových technologií jsou využívány ve výpočetní technice, v měřicí technice, v komunikační technice či v biomedicíně.