Platforma Xilinx Zynq®-7000 spojuje flexibilitu embedded procesoru se surovým výpočetním výkonem programovatelného hradlového pole. Efektivní způsob jejího programování ve spojení s grafickým návrhem a podrobnou verifikací algoritmů přináší vývojové a výpočetní prostředí MATLAB & Simulink firmy MathWorks.

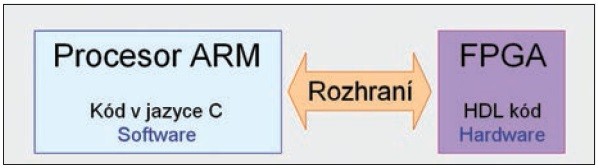

Embedded procesory a programovatelná hradlová pole (FPGA) jsou dnes nedílnou součástí většiny technických systémů. Předností první skupiny je pružnost a komplexnost poskytovaných řešení, zatímco druhá skupina disponuje vysokým výpočetním výkonem. Výhody obou skupin spojuje platforma Xilinx Zynq-7000, která nabízí embedded procesor ARM a programovatelné hradlové pole v jediném celku (obr. 1).

Obr. 1 Xilinx Zynq, spojení flexibility embedded procesoru s výpočetním výkonem FPGA

Simulink je grafický nástroj založený na symbolice blokových schémat, určený pro modelování a simulaci dynamických systémů a vývoj algoritmů (Model-Based Design). Díky simulačním modelům můžete navrhnout, simulovat i verifikovat vaše algoritmy, provádět „what-if“ analýzu a optimalizovat jejich parametry. Přímé a uživatelsky příjemné propojení systému MATLAB a Simulink s platformou Xilinx Zinq je mimořádně výkonným nástrojem pro návrh embedded systémů.

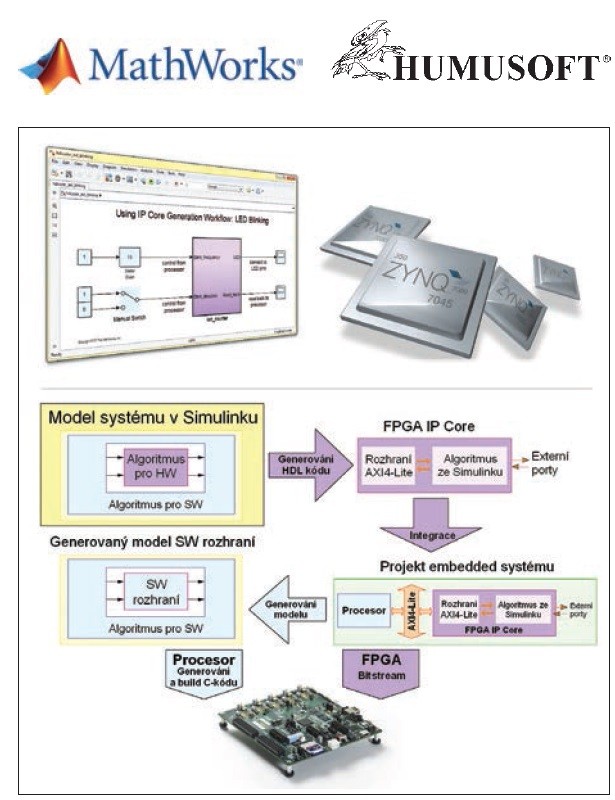

Nasazení algoritmů na platformu Zynq zajišťuje automatizovaný postup, který využívá nástroje Embedded Coder a HDL Coder pro generování embedded kódu ze simulačních modelů. Uživatel je tak oproštěn od manuálního zápisu algoritmů ve dvou rozdílných jazycích (jazyk C, HDL kód). Postup nasazení algoritmů je znázorněn na obr. 2.

Obr. 2 Nasazení algoritmu z prostředí Simulink na platformu Xilinx Zynq

Návrh hardwarové a softwarové implementace algoritmů je vytvářen v rámci jediného modelu. Model je simulován jako jeden celek, takže lze detailně prověřit jeho kompletní funkčnost. Uživatel určí, která část modelu bude převedena do programovatelné logiky (algoritmus pro HW) a která část bude spuštěna v procesoru ARM (algoritmus pro SW). Uživateli je k dispozici grafický průvodce, který jej celým procesem nasazení algoritmu provede.

Z modelu je nejprve generován VHDL® kód pro programovatelnou logiku. Kód je automaticky opatřen rozhraním AXI4-Lite pro komunikaci mezi FPGA a procesorem. Průvodce založí projekt embedded systému v nástrojích Xilinx a vytvořený FPGA IP Core do něj začlení. Dále je průvodcem spuštěna syntéza HDL kódu s následným nasazením algoritmu na programovatelné hradlové pole.

Z části původního modelu určené pro procesor je automaticky sestaven nový Simulinkový model, kde je algoritmus pro HW nahrazen rozhraním pro komunikaci s FPGA ze strany procesoru. Z nového modelu je generován kód v jazyce C, který je buildován a nasazen na procesor. Tím je implementace celého systému na platformu Zynq dokončena.

Nyní přichází na řadu verifikace. Systém implementovaný na platformě Zynq je možné propojit s prostředím Simulink a v reálném čase algoritmus v procesoru ovládat nebo z něj číst hodnoty signálů. Uživatelé tak mohou snadno vyhodnotit, zda se chování výsledného systému shoduje s modelovaným návrhem.

Pokud Vás zajímá více informací, navštivte stránku http://www.mathworks.com/zynq.html, kde najdete nejen podrobný popis nabízeného řešení, ale též ukázkové video (4:08 min), které názorně předvádí nasazení vyvíjeného algoritmu na platformu Zynq.

Distributorem produktů společnosti MathWorks v České republice a na Slovensku je firma HUMUSOFT s. r. o., http://www.humusoft.cz