Nenechte si ujet rychlík aneb procesor ARM + FPGA na jednom čipu

Cílem tohoto článku je seznámit čtenáře s další etapou zvyšování integrace spolu s počtem funkcí na jednom čipu. Poukážeme na nové a již dostupné obvody od firmy Xilinx, které představují spojení dvoujádrového procesoru ARM s jádrem Cortex-A9 a hradlového pole FPGA poslední generace do jednoho čipu, tzv. SoC (System on Chip). Tyto nové obvody byly uvedeny na trh ve skupině s názvem ZYNQ-7000.

Jaké jsou výhody použití SoC v embedded aplikacích?

Pro zachování korektnosti je třeba uvést, že použití těchto obvodů je potřeba zvážit, abychom nešli, jak se lidově říká, s kanónem na vrabce. Jistě ale existuje velké množství aplikací, kde nám tyto nové obvody mohou usnadnit vývoj zařízení. Problémem není ani tak vysoká cena obvodů (cca 100 USD) nebo vývojových prostředků (jsou zdarma), ale množství literatury, kterou je potřeba nastudovat. Pro řešení dané úlohy někdy stačí použít rychlý procesor, jindy je potřeba přidat navíc hradlové pole pro sběr dat a jejich předzpracování. To mi připomíná debatu, kterou jsem před nějakým časem vedl s kolegou, kdy jsme měli každý jiný názor na řešení určité úlohy. Já jsem zastával metodu použití rychlého procesoru, zatímco můj kolega se snažil navrhnout řešení pomocí hradlového pole a masivního využití paralelismu. Nakonec z dané zakázky sešlo, ale s výše uvedeným dilematem se setkávám stále častěji. Použití procesoru je mnohem jednodušší na naprogramování, kdy implementace zpravidla probíhá ve vyšším programovacím jazyce C/C++. Problém se objeví, pokud má být aplikace skutečně realtime. Začneme řešit problémy priorit přerušení, vnořených přerušení atd. A pokud je zapotřebí rychlý sběr dat třeba z AD převodníků s rychlostí 200 milionů vzorků za sekundu, tak jsme při použití procesoru v koncích. Při použití FPGA není naopak problémem sběr velkého množství dat paralelně, přičemž rychlost sběru dat je zpravidla násobkem rychlosti při použití procesoru.

Nevýhodou je naopak značně složitější implementace úlohy v hradlovém poli, třeba pomocí jazyka VHDL. Nutno podotknout, že i zde odvedla firma Xilinx velký kus práce, protože dodávaný software také obsahuje program Vivado HLS (High Level Synthesis). Ten dovede převést program napsaný v C/C++ do jazyka VHDL. Tím samozřejmě nelze říci, že nám vygeneruje VHDL popis z jakéhokoliv C programu, ale zkoušel jsem některé úlohy, a ty se převést povedlo. Navíc lze výpočet paralelizovat, takže když např. potřebujeme sečíst dvě pole a výsledek uložit do třetího pole, potom pomocí direktivy rozložíme smyčku jazyka C na takový počet paralelních součtů, který odpovídá velikosti pole. Této operaci se říká „unrolling loops“.

Jestliže tedy naše úloha vyžaduje použití procesoru i hradlového pole, tak stojí za zvážení užití těchto obvodů. Jak jsem se už zmínil, jistým problémem může být prostudování příslušné literatury, které je velké množství, ale na druhou stranu se některé věci značně zjednoduší ve vztahu spojení procesoru s hradlovým polem. Pokud použijeme samostatný procesor a hradlové pole, tak vznikne velmi složité spojení a celá řada problémů při jeho návrhu. To nás pochopitelně omezuje, zejména počtem spojů a rychlostí. V obvodech firmy Xilinx je z procesoru ARM do hradlového pole vedeno několik vnitřních sběrnic procesoru na interní frekvenci, přičemž se jedná asi o 3000 spojů. Takto masivní spojení mezi dvěma obvody je na desce plošných spojů neproveditelné. Jako další velkou výhodu vidím možnost testování návrhu, kdy je možné připojit sběrnice ARM procesoru do různých míst FPGA návrhu, a tak snadno otestovat jeho chování.

Stručný popis rodiny obvodů ZYNQ-7000

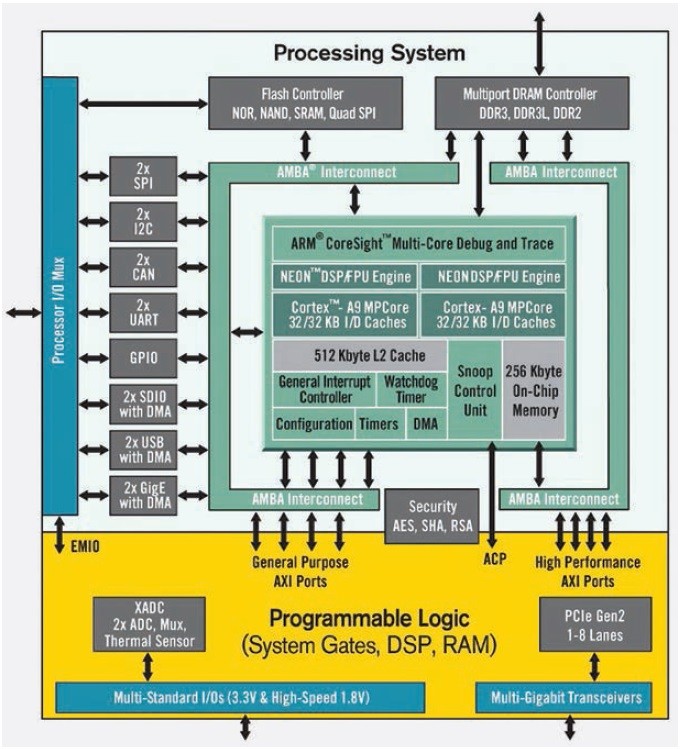

Velmi zjednodušené schéma je na obr. 1. Řada obvodů zahrnuje členy s číselných označením 7010, 7020, 7030, 7045, 7100. Tyto obvody se liší hlavně velikostí hradlového pole, přičemž obvody 7030, 7045 a 7100 mají navíc vyvedeny linky PCI Express a multigigabitové sériové komunikační kanály.

.jpg)

Obr. 1 Zjednodušené schéma obvodu řady ZYNQ-7000 (zdroj www.xilinx.com)

My si představíme typ ZYNQ-7020, včetně vývojového kitu, který si popíšeme později. Obvod ZYNQ-7020 obsahuje dvoujádrový procesor ARM s jádry Cortex-A9, které pracují na frekvenci 720 MHz. Procesor také obsahuje řadič DDR2/3 paměti a je úzce spojen s periferií v podobě USB, gigabitovým ethernetem, SPI, CAN sběrnicí. Tento ARM procesor neobsahuje žádný LCD driver, který je tak nutno řešit v hradlovém poli. Co je ale velmi důležité, obsahuje několik sběrnic, které vedou do hradlového pole. Hradlové pole obsahuje 85 000 logických elementů, což je ekvivalent 1,5 milionů hradel. Jenom pro představu – pokud bychom chtěli toto hradlovém pole postavit z obvodů 7400, tak by při jejich naskládání za sebou vzniknul „vláček“ dlouhý asi 5 km. Toto hradlové pole je také připojeno na vývody BGA pouzdra, čímž lze v úplně nejjednodušší realizaci rozšířit interní procesor ARM o stovky vstupů a výstupů.

Lze se seznámit s obvody firmy Xilinx za přijatelnou částku?

Ano lze. Je však potřeba si uvědomit, o jak komplexní prvek se jedná, a tak se nemůžeme divit, že se s cenou Raspberry nebo BeagleBoard nedá porovnávat. Na druhé straně je pravda, že u výše uvedených projektů se nedá mluvit o nějakém použitelném systému. S těmi několika vstupy a výstupy, které mají, toho moc neuděláme. Proto se mi nezdá částka kolem 6 tisíc korun za vývojový kit Zed- Board dodávaný firmou Digilent nijak přehnaná, vezmeme-li navíc v úvahu, že si s tím nakonec můžeme sestavit třeba digitální osciloskop.

Vývojový kit ZedBoard

Celý kit je na obrázku 2. Jedná se o otevřený projekt hostovaný na stránkách www.zedboard.org, kde lze také stáhnout komplexní dokumentaci, včetně schémat a výrobních dat desky. Deska obsahuje obvod ZYNQ-7020, 512MB RAM paměti, konektor SD karty pro nabootování operačního systém Linux, konektor HDMI, VGA, ethernet, USB, OLED display, několik LED diod a tlačítek a asi 80 I/O pinů. Deska také obsahuje flash paměť pro konfiguraci hradlového pole a další pseudostatickou paměť RAM. Právě zmíněných přibližně 80 I/O vývodů dělá tento kit skutečně vývojovým kitem, protože si k němu můžeme připojit A/D a D/A převodníky, senzory atd.

Obr. 2 Vývojový kit ZedBoard

Jak se seznámit s vývojovým kitem ZedBoard?

Tuto úlohu lze rozdělit na několik částí:

- Pro většinu čtenářů bude asi nejméně známou částí programovatelné hradlové pole. Pro práci s ním je nutné si stáhnout dodávané vývojové prostředí Vivado Design tools, které je zdarma. Potom je už možné začít zkoušet si jednoduché projekty, např. rozblikat LED a postupně přidávat další složitější části. Námi vytvořený konfigurační soubor vždy snadno nahrajeme do kitu pomocí USB.

- Další věcí, kterou musíme zvládnout, je ARM procesor. S kitem je dodávána SD karta s Linuxem, a pokud spojíme vývojový kit pomocí sériového portu se stolním počítačem a připojíme napájecí napětí, tak v komunikačním programu lze vidět a pracovat v Linuxu. Potom můžeme začít psát jednoduché programy v C nebo C++.

- Jako třetí a asi nejsložitější částí se mi jeví spojení ARM procesoru s hradlovým polem. Zde nám mohou pomoci nástroje pro konfiguraci sběrnic procesoru, které jsou dodávány zdarma. Funkci sběrnice ARM procesoru musíme nastudovat poměrně detailně kvůli napojení na hradlové pole. Můžeme si také stáhnout rozšíření, které umožní zobrazení LCD monitoru, zatímco zobrazení je již naprogramováno v hradlovém poli. Pokud začneme s jednoduchou úlohou; jako je třeba rozblikání LED, a pokračujeme např. přes dvourozměrnou síť procesorů naimplementovanou v hradlovém poli; domnívám se, že na hranice možností kitu jen tak snadno nenarazíme.

Závěr

V článku jsme si představili nejnovější obvod od firmy Xilinx, který představuje spojení hradlového pole a ARM procesoru. I když seznámení s tímto obvodem není zrovna jednoduchou záležitostí, jedná se o velmi výkonný obvod vhodný pro vyzkoušení. Snad jenom pro představu – instalace zdarma dodávaných nástrojů spotřebuje na pevném disku 20 GB. Pokrok v technologii výroby integrovaných obvodů umožnil naimplementovat čipy, které jsme si před několika málo lety nedovedli představit. Když se tak dívám na součástky dodávané u nás velkoobchody a srovnám to s těmito obvody, vidím rozdíl mnoha generací, což je jistě škoda.