Před časem byl v tomto časopise uveden článek o optimalizaci rozmístění vývodů FPGA v programu I/O Designer od Mentor Graphics. Chtěl bych se této problematice věnovat z jiného pohledu a doplnit již uvedené informace. V textu se budu opírat o 3 zdroje: návrhový systém Allegro od Cadence (Allegro FPGA System Planner), PADS I/O Designer od Mentor Graphics a moje vlastní zkušenosti z oblasti optimalizačních procesů při řešení úloh, jako je rozmísťování součástek nebo autorouting.

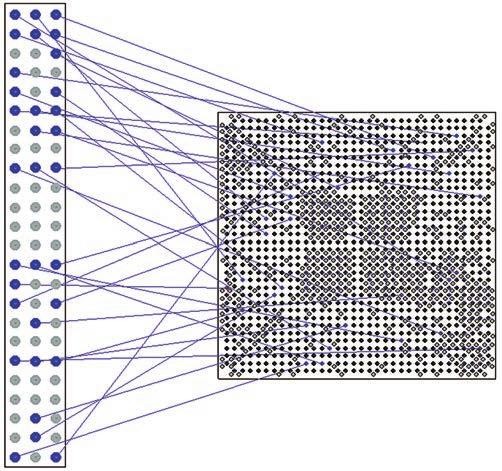

Obr. 1 Spoje od FPGA s prvotním přiřazením vývodů

Prvotní přiřazení vývodů (pin assignment) FPGA pochází od programových nástrojů (Place and Route) výrobců FPGA součástek. Ty ovšem neberou v úvahu rozmístění součástek na desce plošných spojů, a tím ani optimální rozložení spojů mezi FPGA a navazujícími součástkami, čímž trpí kvalita propojení FPGA s dalšími součástkami. Problém vzniká např. při routování rychlé sběrnice z FPGA, kdy požadavek na stejné délky jednotlivých spojů sběrnice lze jen těžko splnit při neoptimalizovaném přiřazení vývodů. Manuální optimalizace přiřazení vývodů FPGA podle dané situace na desce je časově velmi náročná, protože vyžaduje opakované použití nástroje výrobce FPGA a opakované odzkoušení na desce. Proto vznikly programové nástroje k řešení této náročné úlohy, které optimalizaci provádějí při návrhu desky, rychle a skutečně optimálně, protože interní algoritmy provádějí velké množství skrytých optimalizačních pokusů ještě před prezentací výsledku.

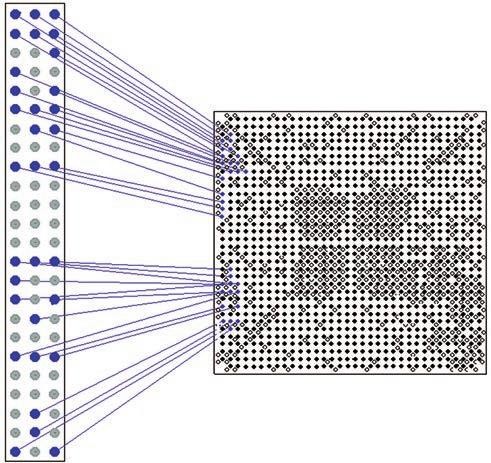

Obr. 2 Spoje od FPGA s optimalizovaným přiřazením vývodů (I/O Designer)

Všeobecně se uvádí, že použitím optimalizačních nástrojů, jako jsou např. PADS I/O Designer, lze ušetřit až jeden týden práce návrhu desky pro zhruba každých 500 použitých vývodů FPGA na desce [1]. Současně se s tím eliminuje opakované prototypování, které si jinak manuální optimalizace přiřazení vývodů FPGA vyžaduje po každé změně.

Výrobní náklady na desku plošných spojů jsou jedním z nejsledovanějších údajů každého výrobce. Pokud se vyskytne problém s routováním spojů od FPGA, obvyklým náhradním řešením je potom přidání dalších vrstev desky. Tím se ovšem náklady na výrobu desky podstatně zvýší, zatímco použitím optimalizačních nástrojů pro přiřazení vývodů FPGA lze naopak mnohdy již předpokládaný počet vrstev desky snížit nebo přinejmenším udržet na navržené hodnotě.

Optimální rozložení zapojených vývodů umožňuje provést i propojení s navazujícími součástkami v nejkratší možné délce. Není tajemstvím, že použitím optimalizačních nástrojů lze zkrátit délku spojů od FPGA až 10x oproti neoptimalizovanému stavu. To je pochopitelně vítaná záležitost s ohledem na dobrý přenos signálu plošným spojem (Signal Integrity).

Jiným důvodem pro použití optimalizačních nástrojů FPGA je také rozšířená bariéra mezi vývojáři a návrháři desek, kdy problém s optimálním přiřazením vývodů FPGA se řeší jinde a odděleně od návrhu desky. Nástroje jako PADS I/O Designer či Allegro FPGA System Planner umožní provést optimalizaci FPGA vývodů přímo v součinnosti s návrhem desky, s minimální vazbou zpět na vývoj. I tak ovšem není nad dobrou spolupráci celého týmu, protože i optimalizace přiřazení vývodů u FPGA může mít svoje limity s ohledem na fyzické umístění vývodů na čipu.

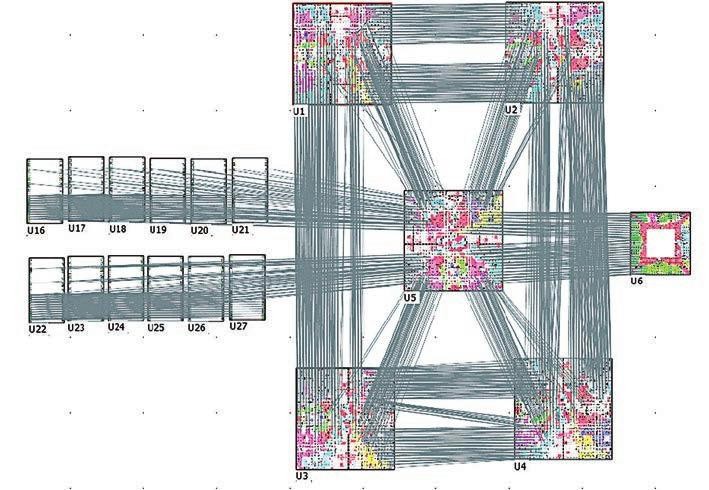

Obr. 3 ilustruje již optimalizovanou situaci [2], kdy je na desce několik součástek s mnoha vývody a s mohutnou soustavou vzájemných vazeb. Čtenář si jistě dovede představit počáteční neoptimalizované zadání, které je sice elektricky správné, ale nebere ohled na rozmístění a natočení všech součástek zúčastněných na vazbách s FPGA.

Škoda jen, že ani jeden ze zmíněných přístupů neumí automaticky rotovat součástky v případě potřeby a ovlivnit tak délku spojů nebo jejich křížení.

[1] PADS I/O Designer (www.mentor.com)

[2] Allegro FPGA Systém Planner datasheet (www.cadence.com)