V minulém díle tohoto seriálu jsme vás seznámili s rodinou Zynq®-7000 Xilinx® All Programmable SoC, která představuje unikátní spojení procesorového systému ARM® Cortex™-A9 s periferiemi, řadičem paměti a především velmi výkonným programovatelným polem na jediném čipu.

V tomto čísle se podíváme blíže na modul SQM4-ZY7, který usnadňuje nasazení i takto komplikovaného obvodu v běžných průmyslových aplikacích nebo i v hobby projektech. Při použití modulu SQM4 již není nutné řešit problémy s vysokorychlostními signály DDR3, s připojením gigabitového rozhraní Ethernet, ani s komplikovanými napájecími zdroji. Modul je možné jako celek osadit povrchovou montáží na základní aplikační desku s plošnými spoji, na níž již nejsou kladeny tak vysoké nároky na přesnost nebo počet vrstev.

Cílem celého seriálu je vyvinout jednoduchou aplikaci pro platformu Zynq, která bude demonstrovat jak bohaté možnosti procesorové části (PS) systému, tak i použití programovatelné logiky (PL) pro syntézu periferie řadiče displeje. Nejprve ale dokončíme téma, které jsme otevřeli v závěru předchozí části.

Základními nástroji pro syntézu logických obvodů (nejen) v hradlových polích jsou všeobecně známé dva jazyky: VHDL a Verilog. Tyto jazyky pracují na tzv. Register Transfer Level úrovni, což znamená, že vývojář popisuje podmínky a logické stavy, ve kterých dochází ke čtení a zápisům tzv. registrů. Registry jsou tvořeny klopnými obvody D, schopnými uchovat v určený okamžik hodnotu vstupního signálu a poskytnout tuto hodnotu jako svůj výstup. Velikost registrů se vždy udává v bitech a na první pohled mohou připomínat běžné proměnné v konvenčních programovacích jazycích.

Zásadní rozdíl je zde ovšem ten, že k běžným proměnným musí softwarový algoritmus přistupovat postupně, v systému programovatelné logiky všechny registry existují a fungují najednou a neustále. Algoritmus v rámci programovatelné logiky je vlastně reprezentován logickými nebo výpočetními výrazy, které definují vstupy, a podmínkami, za kterých dojde k přesunu takto vypočtených hodnot do příslušného registru.

Mezi vývojáři VHDL a Verilog nepanují žádné zásadní spory o to, který jazyk je lepší tak, jako je tomu ve světě softwaru. Oba jazyky mají podobné vlastnosti a stejný přístup k řešení problémů. Oba pracují na úrovni RTL a jejich výstupy se dokonce dají kombinovat v rámci jediného projektu. V praxi je běžné, že vývojový tým pracuje např. ve Verilogu, ale používá knihovní prvky vytvořené ve VHDL. Velmi zjednodušeně se dá říci, že jazyk Verilog je stručnější než VHDL a je syntakticky bližší jazyku C. Je tedy častější volbou vývojářů, kteří se zabývají i softwarem, protože je pro ně i lépe zapamatovatelný. Jazyk VHDL je naproti tomu důslednější a rigoróznější v deklaracích i v syntaxi kódu. Je proto oblíbený především u vývojářů zabývajících se více elektronikou než konvenčním programováním. Obecně je dobré, když vývojář zná jeden jazyk dobře a ve druhém se dokáže alespoň orientovat a pochopit základní myšlenky.

Modul jednoduchého řadiče displeje v naší ukázkové aplikaci bude napsán v jazyce Verilog, takže si pojďme nyní jen v krátkosti představit jeho základní strukturu. Pro bližší seznámení s tímto jazykem existuje nepřeberné množství knih a kurzů. Za tým SQM4 můžeme doporučit:

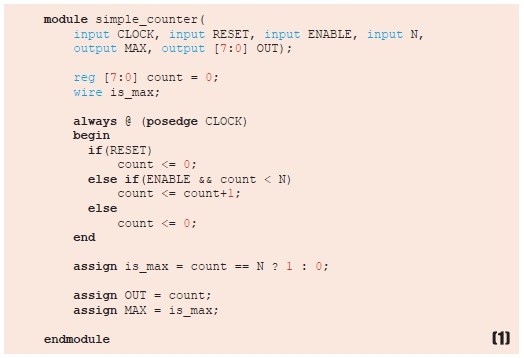

Jedná se o skvělou učebnici jazyka Verilog, která osvětlí nejen syntaxi, ale i principy „toho jiného“ přístupu k řešení problémů než v softwarovém světě. Zároveň naučí čtenáře používat jazyk i k sestavení simulačních prostředí pro důkladné otestování navržených obvodů. Podívejme se na Verilog kód (1), který implementuje jednoduchý synchronní 8bitový čítač od 0 do N.

Kód je víceméně čitelný jen se základní znalostí angličtiny. Definujeme modul, který má vstupní a výstupní signály. V 8bitovém registru count, jehož bity jsou řazeny sestupně od 7 do 0 (little endian formát), budeme udržovat hodnotu našeho čítače. Tuto hodnotu inkrementujeme s každou nástupnou hranou hodinového vstupu CLOCK, ovšem jen pokud není vyžadován RESET a čítač zároveň dosud nedosáhl svého maxima. Kromě registru count, jehož hodnota se mění pouze s hodinovým signálem, máme definován i signální „drát“ is_max, jehož stav závisí na okamžité hodnotě count a limitu N. V závěru kódu přiřazujeme výstupním signálům signály používané interně v rámci modulu.

Uvedený kód vypadá tak trochu jako běžný softwarový algoritmus vykonávaný odshora dolů, ale fakticky to tak není. Jednotlivé části je možné klidně přeskládat, například všechna přiřazení assign by mohla být přemístěna na začátek kódu hned za deklarace. Dokonce i výpočet a přiřazení hodnoty is_max by bylo možné přesunout před místo, kde se inkrementuje registr count. Zdánlivě by se tak pro určení is_max testovala neplatná hodnota count; ale nenechte se plést, vše by stále pracovalo správně.

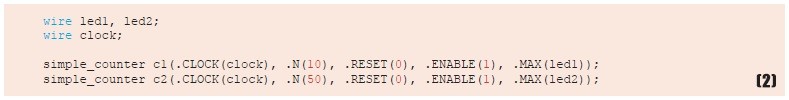

Nyní máme tedy hotový kód čítače. V jiném (např. top-level) modulu můžeme definovat jeho instance. V našem příkladu budou tyto instance dvě. Přiřadíme jim společný hodinový vstup a jejich výstupní signály, které indikují dosažení maxima, přivedeme na interní signální dráty ovládající LED viz (2).

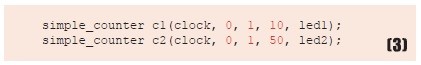

Pokud pomineme trochu zvláštní zápis předávání signálů pomocí tečkové notace se jménem argumentů, může nám tento kód připomínat dvě volání stejné funkce v C nebo spíše volání konstruktoru dvou objektů stejného typu v C++. Tečková notace s pojmenovanými argumenty není povinná. Používá se v případech, kdy není praktické uvádět všechny argumenty nebo se spoléhat na dodržení jejich správného pořadí (což je téměř vždy). Při dodržení správného pořadí argumentů modulu simple_counter by se daly deklarace instancí c1 a c2 zkrátit viz (3)…

…a iluze volání C/C++ funkce je téměř dokonalá. Opět zde ale můžeme dobře demonstrovat rozdílné chování softwaru a našeho zápisu ve Verilogu. V tomto kódu nedochází k žádnému volání nebo inicializaci. Fakticky zde jen deklarujeme dvě instance čítače, z nichž každý je tvořen svým registrem, logikou komparátoru a sčítačkou. Tyto instance se stávají součástí našeho designu a pracují nepřetržitě od okamžiku startu systému až do odpojení napájení. Naše LED budou pulsovat s periodou 10 a 50 hodinových taktů bez nutnosti dalšího kódu a zcela nezávisle na zbytku systému. Na umístění výše uvedených řádek v rámci zdrojového kódu modulu opět nezáleží.

Pochopení tohoto rozdílu mezi sekvenčním chováním software a paralelním chováním RTL je klíčem k úspěšnému zvládnutí práce s hradlovými poli, ať už použijete Verilog, VHDL, či vyšší jazyky jako SystemC a C. Ano, čtete správně. V dnešní době umožňují nástroje tzv. High-Level Language Synthesis (HLS) překlad a paralelizaci kódu běžných jazyků typu C do RTL. Tato technologie ovšem vyžaduje velmi specifický přístup a navíc i značné investice do vývojových nástrojů, takže se jimi nebudeme zabývat. Bez základní znalosti RTL je navíc slepé použití HLS jen zřídka kdy úspěšné.

Na závěr tohoto dílu si ještě popišme jednotlivé části hardwaru, které budeme k realizaci projektu potřebovat:

SQM4-EasyBoard na obr. 1 je univerzální základová deska pro prototypový vývoj aplikací s moduly standardu SQM4. Kromě centrálního soketu, do kterého se SQM4 modul vkládá, poskytuje Easy- Board modulu napájecí napětí a fyzické rozhraní pro komunikace RS232, RS485 a Ethernet včetně oddělovacích transformátorů. Bohužel modul SQM4-ZY7 tak trochu předběhl vývoj samotného EasyBoardu, a tak zde máme k dispozici jen jeden síťový port, a to navíc limitovaný na rychlost 100 Mbps. V různých konfiguracích disponuje modul SQM4-ZY7 jedním nebo dvěma Ethernet PHY adaptéry pro rychlost až 1 Gbps, které ovšem se současnou verzí EasyBoardu nevyužijeme. Na druhou stranu EasyBoard poskytuje i propojení na konektory USB a na zvukový řadič I2S, které naopak ponecháme nevyužité v rámci naší ukázkové aplikace.

SQM4-ZY7 je modul s centrálním čipem Zynq Z-7020 a s obvody nezbytnými pro jeho správnou funkci. Při návrhu modulu bylo hlavním záměrem zbavit uživatele nutnosti zabývat se složitým návrhem mnohavrstvého plošného spoje a dosáhnout vyváženého časování signálů DDR3L, gigabitového Ethernetu a USB. Nadto modul řeší i ne zcela jednoduchou problematiku napájení celého systému, který vyžaduje napěťové úrovně 1 V, 1,5 V, 1,8 V a 3,3 V. Modul je k dispozici v několika variantách podle osazení i podle typu montáže na základní desku. Varianta ZY7-L disponuje dvěma gigabitovými PHY a je bez rozhraní USB, varianta ZY7-U má jeden gigabitový PHY a USB rozhraní. Varianty montáže zahrnují jak zmíněnou instalaci do soketu, tak i dva způsoby povrchové montáže včetně strojního osazování.

7" barevný TFT displej s rozlišením 800 × 480 je součástí vývojového kitu EasyBoard pro SQM4-ZY7. Signály displeje jsou propojeny s obecnými IO piny platformy Zynq, které jsou řízeny z programovatelné logiky.

Veškerá schémata a dokumentace k jednotlivým částem platformy jsou zdarma k dispozici všem zákazníkům a uživatelům modulu SQM4-ZY7.

V příštím díle seriálu vás provedeme prvními kroky s nástrojem Vivado a ukážeme si, jak připravit kostru jednoduché periferie připojené k PS pomocí sběrnice AXI4-Lite. Podíváme se také blíže na specifikaci zvoleného displeje a navrhneme logiku jeho řízení.