Co přesně znamená code coverage?

Code coverage (pokrytí kódu testy) je metoda, která se používá ke stanovení efektivity testu pro část HDL kódu. Metoda měří a indikuje, jaké procento kódu bylo otestováno. Koncept původně přišel ze světa softwaru, kde ho ve svých verifikačních cyklech používají téměř všechny softwarové firmy. Navzdory podobnosti HDL kódu a softwaru napsanému v jazyku, jako např. C, se pro testování HDL kódu tento koncept v takové míře nepoužívá.

Bez použití code coverage návrhář těžko zjistí (nebo nezjistí vůbec), zda všechny aspekty RTL kódu byly otestovány. Code Coverage je zabudován do simulátoru a návrháři indikuje, které oblasti byly otestovány, a co je ještě důležitější, které části otestovány nebyly. Co se tedy během code coverage testuje a jaké jsou jeho typy? Následující text popisuje typy pokrytí, které můžeme použít.

Statement coverage

U tohoto typu pokrytí kódu simulátor monitoruje všechny proveditelné příkazy HDL kódu. Máte například ve vašem návrhu 1 000 proveditelných příkazů, ale provedeno jich je pouze 800, což nám dává statement coverage 80 %. Aby návrhář dosáhl úplného pokrytí, bude potřebovat buď napsat cílenější testy, nebo omezeně upravit náhodné testy.

Branch coverage

U příkazů ‘case’ nebo ‘if-then-else’ bude mít simulátor na výběr alternativní větve, které návrh obsahuje, a test by měl všechny projít a zkontrolovat jejich úplnost. Může se stát, že i když na příkazy ‘case’ nebo ‘if-then-else’ narazí několikrát, nemusí dojít k otestování všech možných větví. Tento typ identifikuje neotestované větvě. Jestliže část kódu vykázala v branch coverage pokrytí 100 %, znamená to, že všechny větve kódu byly provedeny alespoň jednou. Zde je jednoduchý příklad:

case address is

when 1 =>

x <= ”001”;

when 2 =>

x <= ”010”;

when others =>

x <= ”100”;

end case;

V tomto příkladu bude branch coverage identifikovat, zda byly provedeny všechny tři větve příkazu ‘case’. Pokud budou provedeny jen dvě větve, dostaneme hodnotu branch coverage 66,7 %.

Condition coverage

Zde se jedná o hlubší formu branch coverage. Tento typ rozkládá podmínky větve na elementy, které mají výsledek true nebo false. Jestliže část kódu vykázala v condition coverage 100 %, znamená to, že všechny větve kódu byly alespoň jednou provedeny na všechny logické podmínky. Zde je jednoduchý příklad:

if (a = ’1’ or rst = ’1’) then

y := ‘0’;

else

y := not y;

end if;

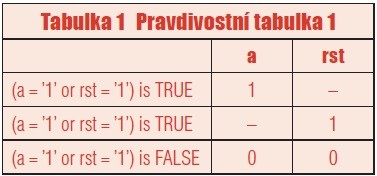

V tomto příkladu bude condition coverage identifikovat všechny možné způsoby, jakými se větve dají provést. Ty jsou zobrazeny v pravdivostní tabulce 1:

Pokud byl například signál rst vždy nula a my provedeme branch coverage na tomto kousku kódu, dostaneme 100% pokrytí za předpokladu, že otestujeme větve true a false. Condition coverage bude ale hledat všechny možné kombinace. Tři možné jsou uvedeny v tabulce 1. V případě, že je rst permanentně low, dostaneme 100% branch coverage, ale jen 66,7% condition coverage.

Expression coverage

Tento typ přináší statistiku pro všechny výrazy v HDL kódu, kde daný výraz může být buď průběžné, nebo procedurální přiřazení. Expression coverage, podobně jako condition coverage, identifikuje výrazy, které nejsou dostatečně otestovány. Zde je příklad jednoduchého příkazu průběžného přiřazení.

z <= (b = ’1’ and c = ’1’);

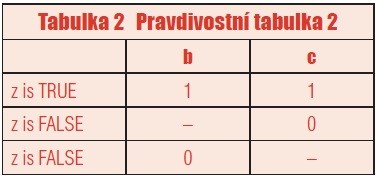

V tomto příkladu by statement coverage zjistil, zda byl tento příkaz proveden, ale nezjistil by, zda byly provedeny všechny možné prostředky vytvářející podmínku true nebo false. Z tabulky 2 je patrné, že pro dosažení 100% pokrytí u tohoto kousku kódu musí být tento kód proveden alespoň jednou pro všechny tři kombinace uvedených vstupů.

FSM (Finite State Machine) coverage

Tento typ pomáhá analyzovat různé styly konečného automatu zapsané v HDL kódu. Abychom konečný automat důkladně ověřili, je podstatné zkontrolovat, zda jsme dosáhli všech jeho stavů, a také, zda jsme otestovali všechny platné stavové přechody.

Toggle coverage

Tento typ se tradičně používá pro návrhy ASIC, kde je z důvodu testování při výrobě nutné testovat křemík, aby byla zajištěna 100% funkčnost. U návrhů FPGA to obecně není nutné, protože dodavatelé FPGA tyto výrobky před distribucí 100% testují. Proto se dále tímto typem nebudeme zabývat, ale pro úplnost jej uvádíme.

Závěr

Použití code coverage v dnešním HDL návrhu a ověřovacích fázích je zásadním prvkem zlepšování kvality výrobků. Všichni odborníci, kteří se chtějí dozvědět více, mohou navštívit náš webinář archivovaný na webových stránkách: www.mentor.com/products/fv/multimedia/ code-coverage-automation.