Číslicové zpracování dat a signálů platformou FPGA

Úvod

Cílem článku je demonstrovat využití struktur hradlových polí v oblasti zpracování číslicových signálů a periferních zařízení mikroprocesorů nebo PC. V současné moderní elektronice převažují výhody číslicového zpracovaní signálu nad zpracováním analogovým. V minulosti byla limitujícím faktorem nízká vzorkovací frekvence, malá rozlišovací schopnost A/D a D/A převodníků a v neposlední řadě i cena číslicových výpočetních systémů. Dnešní digitální systémy jsou schopny zpracovávat signály se vzorkovací periodou menší než 1 ns a přenášet data rychlostí vetší než 100 Gbitů/s.

Zpracování číslicových signálů

Komerční nasazení výpočetní techniky a číslicových systémů vedlo ke snížení ceny, spotřeby a k razantnímu zvýšení spolehlivosti a výpočetního výkonu těchto systémů. Trend je patrný především u systémů masové spotřeby jako jsou set top boxy, audio a video přehrávače, mobilní sítě a telefony, internet a telekomunikace. Výrobci digitálních integrovaných obvodů se nesnaží jen o zvýšení integrace periferních zařízení a řadičů paměti a také o zvýšení výpočetního výkonu vlastního jádra procesoru. Jedná se o nové instrukce typu SIMD (Single Instruction Multiple Data), ale také o výkonné jednotky provádějící sekvence složitých matematických operací, které probíhají nad tokem dat obvykle bez účasti procesoru – šifrování, komprese dat, podpora modulací, vícekanálové kódování. V některých aplikacích se dnes běžně využívají vícejádrové procesory, známé třeba z platforem PC, nebo speciální aplikační procesory. Aplikační procesory obvykle obsahují několik výkonných jednotek a to zpravidla o různých platformách na rozdíl od PC. Příkladem muže být aplikační procesor firmy Texas Instruments, který obsahuje jádro procesoru ARM Cortex A8, jádro signálového procesoru řady 64xx (jádro 64xx obsahuje osm výkonných jednotek) a dále jednotky pro zpracování videa. Obvyklé využití více jádrových aplikačních procesorů je rozděleno do několika částí, kdy jeden procesor vykonává činnosti spojené s uživatelským rozhraním (čtení dat z klávesnice, kreslení na obrazovku, provádění uživatelského programu, síťové komunikace) a je obvykle vybavený operačním systémem Linux nebo zákaznickým systémem. Další jednotky slouží pro zajištění akcelerace a realtimového běhu paralelních procesů (řízení technologických procesů, komprese videa). Je běžné, že jednotky pracují na frekvencích větších než 600 MHz a dosahují výpočetních výkonů desítek GMAC (1×109 operací typu A=A+(B×C)).

Čtenář si jistě položí otázku, jak problematika hradlových polí souvisí s architekturou na bázi procesorů. V první řadě je třeba si uvědomit skutečnost, že procesory přes svoji univerzálnost a velmi slušný výpočetní výkon v některých aplikacích nesplňují parametry kladené na cílovou aplikaci nebo realizace pomocí procesorových systémů by byla velmi nákladná a málo flexibilní.

Obvykle se využívají dva základní principy. V prvním případě se používá pro zpracování dat pole samotné bez externího procesoru a ve druhém je pole připojeno k externímu procesorovému systému pomocí komunikačního rozhraní nebo vytváří přímo periferii procesoru – popis bude uveden v dalším pokračování tohoto článku. V následujících odstavcích si popíšeme oba způsoby využití FPGA pro zpracování číslicových signálů.

Před vlastním popisem je třeba uvést, jaké prostředky máme v hradlovém poli typu FPGA k dispozici. Výpočetní operace lze realizovat buď přímo pomocí logických prvků tvořených generátory logické funkce nebo pomocí tzv. DSP bloků. Využití logiky v FPGA má v dnešní době smysl pro jednodušší operace, podpůrné části výpočtů, řízení výpočtů nebo pro tvorbu „nestandardních“ funkcí. Výhodou logiky je poměrně vysoká flexibilita, nevýhodou takto generovaných operací je obvykle nižší pracovní frekvence (neplatí obecně) a pochopitelně větší spotřeba logických bloků v FPGA. Existuje však celá řada úloh, kdy jsou tyto zdroje dostatečné. Obvykle se jedná o operace prahování, základní aritmetické operace – součet, rozdíl, rotace a logické operace. Pro obecné operátory součinu je obvykle výhodnější využívat DSP bloku.

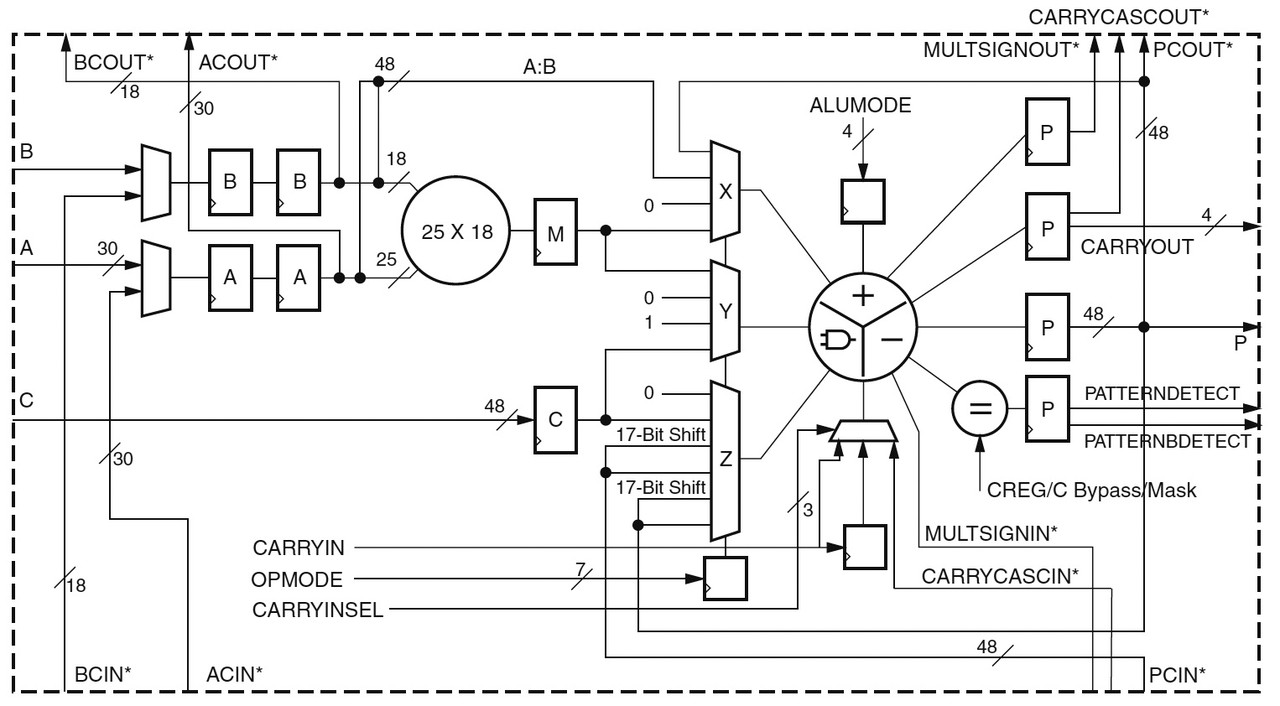

V následující části příspěvku budou popsány funkce DSP bloku FPGA řady Virtex 5 viz obr. 1 (popis funkcí je pouze informativní a nezabývá se praktickým využitím nebo detailním nastavením, což by vydalo na seriál několika článků).

Obr. 1 DSP48E blok v FPGA řady Virtex 5

DSP blok s označením DSP48E nabízí tyto základní funkce:

- násobičku 25×18 bitů s plnou podporou MACC operací až se 48bitovým výsledkem vhodné pro konstrukci IIR filtrů

- dynamický výběr operací v ALU jednotce (součet, rozdíl, logické operace) – kaskádní řazení DSP bloků s podporou přenosu výsledků až do hloubky 96 bitů

- SIMD operace 4×12 bitů nebo 2×24 bitů v jednom DSP48E bloku a taktu

- 48bitovou logickou jednotku, barrel shifter

- rychlý 48bitový čítač, detekce vzorů

- zaokrouhlování výsledků, saturace, přetečení a podtečení

- podpora multiplexování dat v čase.

V hradlovém poli Virtex 5 může DSP blok pracovat do frekvence 550 MHz, přičemž počet jednotek v jednom pouzdru se pohybuje od desítek až po tisíce bloků čemuž také odpovídá cena obvodu. Z výše uvedeného stručného popisu vyplývá, že FPGA je schopno řešit výpočetně náročné úlohy rychleji než klasické procesorové systémy. Na druhé straně je jasné, že výhody použití těchto struktur jsou omezeny vývojovými nástroji a schopnostmi návrháře cílové platformy. Návrh vlastních komponent vychází z možností architektury FPGA. Jedná se především o využití vnitřních zdrojů (blokové paměti, DSP bloky, logické bloky), stanovení vhodného časování a pochopitelně z omezení prostorových nároků uvnitř čipu na požadovanou funkci. Pro tvorbu vlastního designu se obvykle používají programovací jazyky typu HDL (VHDL, Verilog). Jazyk HDL neposkytují návrháři dostatečnou formu abstrakce pro takto složité algoritmy, což značně komplikuje práci a snižuje flexibilitu řešení, kdy i jednoduché změny a jejich ověření zaberou nemálo času.

K zefektivnění práce přispívají generátory funkcí (FFT, maticové operace), které zpravidla bývají přístupny i v základních verzích SW bez poplatku. Dále je možné využívat hotové IP funkce (komprese, modulace), které jsou vázány na zakoupení licence.

Nezbytnou součástí zpracování číslicových signálů jsou paměťové prostředky určené pro uchovávání mezivýsledků výpočtů podobně, jak je známe z klasických procesorů. Hradlová pole disponují třemi základními typy paměťových prostředků. Prvním a v celku logicky očekávaném je klopný obvod. Klopné obvody slouží pro uchovávání menšího počtu dat, se kterými je třeba rychle pracovat, nebo kdy je nutné přistupovat k více hodnotám v jeden časový okamžik – hodinový takt. Druhým paměťovým typem jsou distribuované paměti, které se budují v LUT v CLB nebo LAB blocích. Distribuované paměti jsou adresovatelné v hloubce 16–64 úrovní v bitové šířce 1–n bitů, kde n je omezeno velikostí pole a schopnostmi propojovací sítě uvnitř FPGA (standardně nabývá hodnot 256), paměť podporuje jedno nebo dvou portový přístup k datům v jedné časové doméně. Používají se pro uchování mezivýsledků, časové multiplexování konstant nebo výsledků. Při rozumném využití dosahují vysoké pracovní rychlosti a jsou šetrné k prostředkům FPGA. Posledním prostředkem pro uchování dat v hradlovém poli je bloková paměť RAM. Jedná se o blok, který je integrální součástí čipu a podporuje obvykle jen paměťové funkce. Paměti mají hloubku řádově v jednotkách kB, jsou konfigurovatelné v šířce od 1 do 36 bitů, podporují kaskádování a jsou plně dual porte – každý port může operovat s jinou pracovní frekvencí. Využití najdou jako úložiště dat/konstant, pro složitější operace (FFT, komprese), při zpracování vícerozměrných signálů – práce nad obrazem pomocí filtrů.

Pozn. V textu nebyly diskutovány externí paměti, které se využívají jako úložiště dat velkých objemů.

Nyní se pojďme věnovat popisu první metody využití FPGA při zpracování číslicové informace. Jak bylo uvedeno v předchozím odstavci, FPGA se využívá jako samostatná jednotka, která data zároveň získává, zpracovává, vyhodnocuje a také provádí a generuje předpokládanou odezvu na výstupu. Postup je obvykle takový, že na vstup FPGA je připojen převodník nebo vhodný datový proud, který je logikou v FPGA předzpracován, dále postupuje do vyhodnocovací jednotky, která data zpracuje (FIR, IIR, FFT, komprese) a předá na výstup ve vhodném formátu. Typickým výstupem jsou filtrovaná data, náhodné číslo, výsledek vyhodnocení z kamerového systému, dekomprimovaná obrazová data vkládaná přímo do obrazu nebo data odeslaná po sériové lince. Příkladem může být kamera vyhodnocující stopu laserového paprsku na projekční stěně s velmi vysokou frekvenci vzorkování (500 Hz) a vysokým rozlišením (1280×1024 v 10bitové hloubce), kde datový tok dosahoval 700 MB/s. Řízení CCD čipu, vyhodnocení a komunikace probíhala v low-cost poli typu Spartan3E. Generované výsledky měly datový tok několik kB/s.

Druhou používanou metodou je spolupráce FPGA s jiným procesorovým systémem (ARM, PC, DSP), aby tato spolupráce mohla byt účinná, je třeba navázat komunikaci mezi oběma platformami a vhodným způsobem spojit FPGA s procesorem nebo sběrnicovým subsystémem počítače. Moderní hradlová pole jsou vybavena pro styk s okolím obvykle pomocí rychlých sériových linek a nad nimi fungujících protokolů (RapidIO, PCI Express v 1.1 a 2.0, 1–10Gbit Ethernet, XAUI a další). Pokud se omezíme na standardní a běžně používané rozhraní, jedná se především o využití Ethernetu o rychlosti 100–10000 Mbit/s, sběrnice PCI Express a u DSP RapidIO. Využití a přednosti Ethernetu jsou široce známy, standard RapidIO je využíván především v komunikacích, a proto tyto standardy nebudeme dále diskutovat a pozornost zaměříme na sběrnici PCI Express a její využití v zajímavých aplikacích.

Výhodou sběrnice PCI Express je malý počet vodičů nutných k připojení na sběrnici, duplexní komunikace vysokou rychlostí (pro x1 od 250 MB/s až do 500 MB/s dle revize a to plně duplexně) a poměrně robustní a dobře zabezpečený komunikační protokol. Pro sestavení funkčního linku x1 jsou ve své podstatě potřeba jen 3 signály (PETp/n vysílací pár, PERp/n přijímací pár a hodinový signál REFCLKp/ n). Ze značení p/n plyne, že se jedná o signály diferenciální. Při návrhu desek plošných spojů je nutno na tento fakt pamatovat a dodržovat předepsaná doporučení.

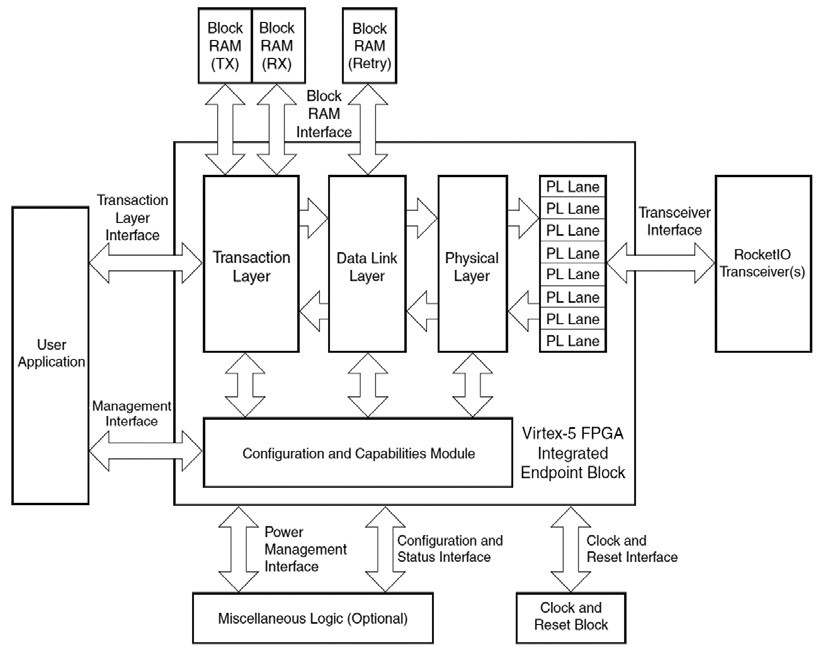

Obr. 2 PCI Express end point v FPGA řady Virtex 5 firmy Xilinx

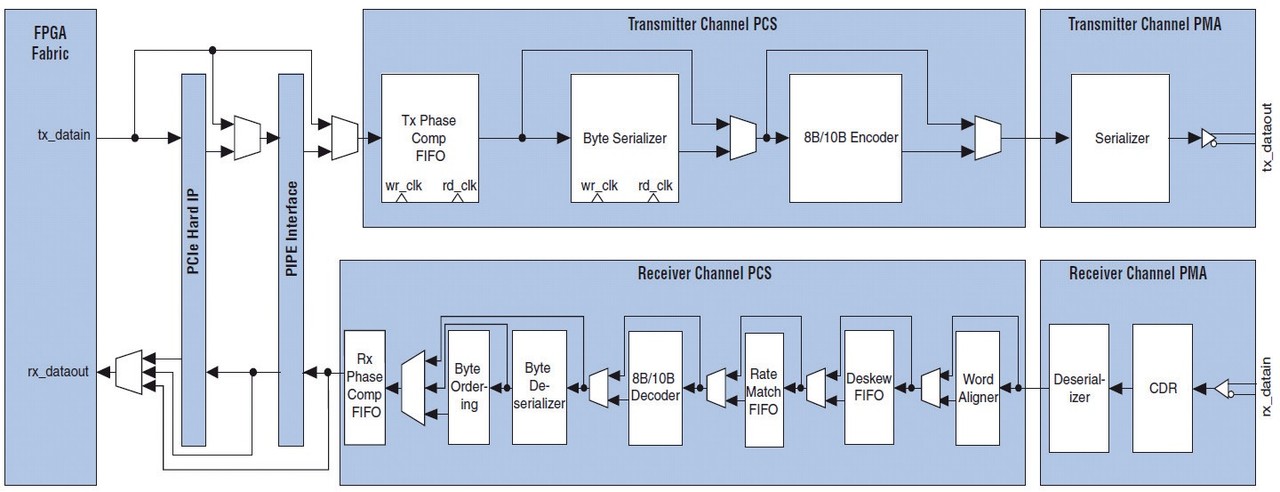

Nevýhodou této koncepce je značná složitost implementace samotného protokolu. Tuto nevýhodu se snaží výrobci hradlových polí odstranit integrací PCI Express End-pointu nebo root-complexů do struktury FPGA. Typické uspořádání je vidět na obr. 2, kde je v poli integrovaná fyzická, datová a transakční vrstva. Posledním blokem nutným pro zdárné připojení ke sběrnici je transceiver, který zajišťuje přístup k médiu, kódování, synchronizace a řízení úrovní signálů. Tyto bloky jsou v moderních polích k dispozici a je možné je přímo připojit k funkčnímu bloku PCI Express viz obr. 3, kde je zobrazeno propojení PCI Express a transceiver v hradlovém poli Cyklone IV firmy Altera (transceiver dále nebude popisován).

Obr. 3 PCI Express IP core a transceiver v FPGA řady Cyclone IV firmy Altera

Tyto funkce uvnitř FPGA nám umožňují bez problémů připojit a budovat univerzální systémy s platformami PC a to i vhodnými pro průmyslové využití například se sběrnicí ComExpress (Computer- on Module) nebo QSeven při zachování malých rozměrů, jednoduché a levné rozšiřující desce. Příklad počítače s procesorem Intel Atom a rozhraním Com Express je na obr. 4. Výhodou této koncepce jsou malé rozměry, rychlá realizace aplikace (využívají se standardní nástroje v prostředí Windows XP/7 nebo Linux), kde hradlové pole zajišťuje realtimové zpracování dat a přenos do hlavní paměti procesoru PC. Pochopitelně se nemusí jednat o složité aplikace kompresních algoritmů, ale je běžné, že se vyrábí technologické moduly jen se vstupy/výstupy, časovači, převodníky na jiné protokoly. V těchto aplikacích počítač třídy PC slouží jako nadřazený systém zajišťující komunikaci s okolím a realizující řídicí funkce složitějších algoritmů, které nevyžadují odezvu v reálném čase, jejichž implementace do FPGA by byla velmi komplikovaná, drahá nebo takřka nemožná. Velkou výhodou je schopnost měnit obsah struktury FPGA pomocí nadřazeného PC, což dále zvyšuje flexibilitu řešení.

Obr. 4 Počítač třídy PC s rozhraním Com Express

Více informací, referenčních příkladů a návodů je možno získat u společnosti DFC Design na adrese www.dfcdesign.cz, která také poskytuje školení v oblasti FPGA, DSP a vývoj zařízení a periferii pro FPGA a DSP.

Společnost DFC Design je zaměřena na vývoj hardwaru a softwaru v oblasti číslicového zpracování signálu, emdedded zařízení a průmyslových aplikacích. Jednou z oblastí, ve kterých společnost dosahuje významných výsledků, je vývoj aplikací na bázi programovatelné logiky a mikroprocesorových systémů.