Programovatelné logické obvody se sebelepší vnitřní architekturou by nebyly prakticky použitelné bez odpovídající podpory vývojových prostředků. Teoreticky je při znalosti vnitřní architektury konkrétního PLD možné přímo vytvořit finální schéma propojení jednotlivých funkčních bloků. U jednoduchých PLD, jako jsou obvody PAL nebo GAL, je něco takového i prakticky realizovatelné, ale u dnešních složitých FPGA je to něco naprosto nereálného.

Základní vývojové prostředky pro programovatelnou logiku musí zajistit transformaci vstupního návrhu nebo popisu funkce do výstupního formátu použitelného pro konfiguraci nebo naprogramování konkrétní součástky. Ve skutečnosti je to pouze jedna z mnoha funkcí dnešních vývojových prostředků používaných pro aplikaci programovatelné logiky. Vývojová prostředí pro FPGA se stávají neustále složitějšími a komplexnějšími. Jsou často podobná velkým vývojovým systémům pro digitální integrované obvody a mnohé používané nástroje jsou totožné. Typické vývojové prostředky pro programovatelnou logiku je možné rozdělit do několika základních skupin podle jejich funkce:

Implementační nástroje slouží pro převod návrhu funkce do výstupního formátu použitelného pro fyzickou konfiguraci programovatelné součástky. Do této skupiny patří nástroje pro syntézu a implementaci.

Verifikační nástroje slouží pro ověření funkce jak samotného návrhu, tak i jednotlivých mezivýsledků implementačního procesu. Do této skupiny patří číslicové nebo smíšené simulátory a různé analytické nástroje. Může se jednat o nástroje pro statickou časovou analýzu (STA) nebo třeba analyzátory výstupů implementačních prostředků.

Hardwarové prostředky slouží především pro verifikaci, ověření funkce výsledného obvodu a pro jeho charakterizaci. Jedná se například o různé vývojové a testovací desky, programátory, programovací adaptéry a JTAG adaptéry pro konfiguraci, měření, testování a ladění. Používají se často pro ověření funkce a charakterizaci před finálním návrhem vlastní desky plošných spojů. Některé z hardwarových prostředků slouží k produkčnímu programování PLD nebo jejich konfiguračních pamětí.

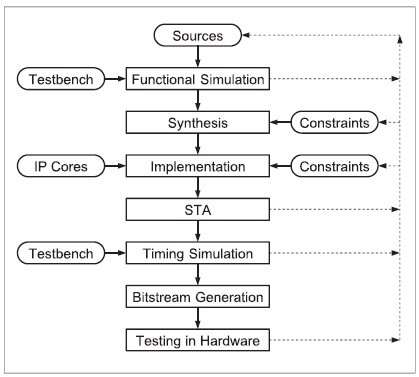

Schéma typického postupu vývoje pro programovatelné logické obvody je znázorněno vývojovým diagramem na obrázku 1. Jedná se o zjednodušení vycházející z postupu vývoje plně zákaznických číslicových integrovaných obvodů.

Obr. 1 Postup vývoje pro FPGA

V diagramu na obrázku 1 jsou použity anglické výrazy, protože některé z nich nemají české ekvivalenty. Význam jednotlivých bloků diagramu je popsán dále.

Do procesu návrhu programovatelných logických obvodů vstupuje mnoho různých dat sloužících pro popis funkce, pomocná data a skripty pro simulace a verifikace, pomocná data a skripty pro implementaci a další.

Požadovaná výsledná funkce programovatelného obvodu může být popsána kombinací několika následujících základních metod:

Nejrozšířenější metodou popisu logických obvodů je v dnešní době použití HDL. Prakticky se pro vstup syntézy používají jazyky VHDL, Verilog a System- Verilog, což jsou specializované jazyky určené pro popis číslicových systémů od velmi nízké úrovně typu netlist až po vysokoúrovňový popis využívající metod objektově orientovaného programování a dalších vlastností převzatých z moderních programovacích jazyků. Výhodou použití HDL je univerzálnost a přenositelnost, protože jazyky jsou standardizovány organizací IEEE a všechny současné nástroje pro syntézu podporují alespoň VHDL a Verilog.

Použití HLL pro návrh číslicových systémů není dosud příliš rozšířené, ale začínají se objevovat použitelné nástroje. Syntéza z HLL obvykle probíhá ve dvou krocích, kdy je zdrojový popis ve vysokoúrovňovém jazyce nejdříve přeložen do některého HDL a ten je následně předán syntéze. HLL pro popis hardware obvykle vycházejí až na výjimky z jazyka C nebo C++. Zvláštní kategorií jsou nástroje určené pro MATLAB, které převádějí M-kód na HDL.

Obvodová i bloková schémata se v dnešní době používají již velmi zřídka. Současné programovatelné logické obvody poskytují takové množství logických prostředků, že typické návrhy jsou velmi rozsáhlé. Doba vývoje, přehlednost a udržovatelnost komplexních digitálních návrhů ve formě schémat jsou mnohem horší ve srovnání s HDL.

Ostatní formy popisu jsou většinou specifické pro konkrétního výrobce nebo určité nástroje. Společnou typickou vlastností je, že se vždy před syntézou vygeneruje syntetizovatelný popis v HDL.

Kromě popisu funkce obvodu potřebuje simulátor ještě další podpůrné soubory. Jde jednak o soubory generující vstupní hodnoty a vyhodnocující výstupy, které tvoří takzvaný testbench, a dále o pomocné skripty řídící vlastní proces simulace, jeho automatizaci a podobně.

Testbenche se v dnešní době realizují buď v HDL, nebo HVL (Hardware Verification Language). Speciální a vysokoúrovňové jazykové konstrukce vhodné pro simulace a verifikace nabízí z HDL především VHDL, SystemVerilog a SystemC. Nejpoužívanější HVL jsou PSL (Property Specification Language), e, OpenVera a opět SytemVerilog a SystemC, což jsou jazyky kombinující vlastnosti HDL a HVL. Důležitými vstupy pro časové simulace jsou soubory SDF (Standard Delay Format), které definují zpoždění jednotlivých prvků.

Simulace funkčního popisu zapsaného v HLL se obvykle provádí ve stejném jazyce. Samozřejmě je ale možné převést popis z HLL do HDL a výsledek poté simulovat v běžném digitálním simulátoru s pomocí HDL/HVL testbenchů.

Součástí vstupních souborů pro simulace a verifikace bývají často skripty pro řízení vlastních simulačních programů. Tyto pomocné soubory obvykle zajistí vytvoření potřebných knihoven, kompilaci funkčního popisu ve správném pořadí do správných knihoven, nastavení simulátoru, zobrazení požadovaných výstupů a spuštění simulace.

Implementační nástroje potřebují kromě popisu funkce ještě další vstupní data, která ovlivňují výsledek implementačního procesu. Jedná se především o definici jednotlivých fyzických omezujících podmínek, tzv. constraints. Je nutné jednotlivým vstupně-výstupním signálům přiřadit konkrétní piny programovatelné součástky a nastavit elektrické parametry vstupních přijímačů a výstupních budičů. Další parametry, které mají vliv na implementaci, jsou časové vlastnosti hodinových signálů, datových vstupů a výstupů, stejně jako některých interních signálů. Důležité je například správně ošetřit přechody mezi asynchronními hodinovými signály nebo delší kombinační logické cesty. Poslední oblastí je možnost ručního umístění některých funkčních bloků na čipu FPGA nebo vymezení oblastí, ve kterých smí být daný blok automaticky umístěn. Jedná se o takzvaný floorplannig.

Další skupinou vstupů pro implementační proces je správné nastavení implementačních nástrojů. To je obvykle možné dělat interaktivně v GUI pomocí konfiguračních souborů nebo implementačních skriptů. Skriptování implementačních nástrojů pro programovatelnou logiku se provádí typicky v jazyce TCL, některé nástroje podporují i Perl.

Implementační nástroje zahrnují syntézu, vlastní implementaci, generování programovacích souborů a další podpůrné nástroje používané pro generování pomocných souborů, konfigurování IP jader, vytváření constraints, generování implementačních skriptů a podobně. Výsledkem implementačního procesu je soubor určený pro konfiguraci programovatelného logického obvodu. Ten by měl po nakonfigurování realizovat funkci definovanou popisem použitým jako vstup pro implementaci.

Nástroje pro implementaci je možné rozdělit na front-end, back-end a ostatní podpůrné nástroje. Mezi front-end nástroje patří především syntéza a pak také různé vysokoúrovňové kompilátory a konvertory. Back-end reprezentují implementační nástroje, které překládají výstup syntézy do výsledného konfiguračního souboru. Podpůrné nástroje slouží pro pomocné úlohy související s implementací.

Pro front-end nástroje je typická poměrně dobrá a dostupná specifikace, takže není problém narazit na nástroje různých výrobců a vývojář nemusí být nezbytně závislý na nástrojích dodavatele programovatelných logických obvodů. Vstupem syntézy je například plně standardizovaný HDL a výstupem je netlist opět ve standardním souborovém formátu. Netlist smí obsahovat pouze komponenty výsledného programovatelného logického obvodu, ale ty jsou na této úrovni velmi dobře specifikovány a zdokumentovány přímo výrobcem. Nástroje pro vysokoúrovňové jazyky mají opět k dispozici přesné specifikace jak vstupního HLL, tak výstupního HDL.

Co se týče back-end nástrojů, je uživatel odkázán na výrobce programovatelné logiky. Specifikace skutečné vnitřní struktury PLD, která je pro vývoj back- -end nástrojů nutná, je přísně střeženým tajemstvím. Situace trochu připomíná back-end nástroje pro návrh integrovaných obvodů. Samotné nástroje jsou sice do jisté míry nezávislé na výrobci konkrétních ASIC, ale ke své funkci potřebují knihovny dodávané právě výrobcem. Kromě interní struktury používané programovatelné součástky musí back- -end nástroje znát i charakterizační data obvodu.

Pomocné nástroje slouží pro podporu implementačního procesu. Velmi důležitou skupinu tvoří nástroje pro tvorbu omezujících podmínek – constraints – pro syntézu a implementaci. Tyto nástroje obvykle umožňují jednoduchou formou vyplňováním formulářů nebo pomocí grafického editoru vytvářet různé typy constraints, které pak ukládají ve formátu použitelném implementačními nástroji, jako například UCF, SDC nebo XDC. Další skupinou pomocných nástrojů bývají konvertory různých souborových formátů, které slouží například pro převod netlistů z formátu EDIF do vnitřního netlistu konkrétního výrobce a podobně. V rámci implementace se často používají různé analytické a vizualizační nástroje, které usnadní analýzu výsledků implementačního procesu. Umožňují třeba grafické zobrazení výsledku syntézy ve formě schématu, generování různých implementačních statistik a logů nebo vizualizaci kompletně implementovaného projektu v programovatelném obvodu. Některé nástroje umožňují i ruční editaci výsledku implementace.

Velmi významnou skupinu implementačních nástrojů tvoří právě nástroje pro práci s IP jádry. Značná část funkce návrhu pro dnešní velká FPGA je často realizována připravenými hotovými funkčními bloky. Pro zjednodušení jejich konfigurace, parametrizace, modifikace, propojení a integrace existují různé specializované nástroje. Samozřejmě existují i nástroje usnadňující vytváření, balení a distribuci vlastních jader.

Základní nástroje pro práci s jádry umožňují konfiguraci parametrů autonomních IP jader. Výsledkem je obvykle zdrojový kód nebo netlist použitelný společně s ostatními zdroji pro syntézu a verifikaci. Tyto nástroje se používají pro přípravu často používaných běžných funkčních bloků, jako jsou například různé typy pamětí, bloky realizující aritmetické operace, různá specializovaná rozhraní a podobně. Pokud chce například vývojář použít v návrhu FIFO, stačí do projektu vložit IP jádro pro FIFO a v jeho konfiguraci vybrat šířku datových sběrnic, hloubku paměti a nakonfigurovat potřebné řídicí signály. Výsledkem je pak obvykle netlist, který se může v návrhu používat jako jakýkoli jiný běžný modul.

S rostoucími možnostmi programovatelné logiky je dnes v FPGA běžné použití procesorů nebo celých procesorových systémů. Specializované nástroje umožňují sestavení a konfiguraci rozsáhlých procesorových systémů, vzájemné propojení jednotlivých bloků pomocí různých sběrnic. Kromě výstupů použitelných pro implementaci a verifikaci umožňují tyto nástroje vygenerovat výstupy pro následný vývoj software. Samozřejmostí bývá možnost společné simulace návrhu hardware a software v době, kdy ještě není k dispozici finální hardware.

Nástroje pro verifikaci návrhu a implementace programovatelné logiky zahrnují jednak klasické digitální simulátory, specifické nástroje svázané s implementačními nástroji konkrétních výrobců, a pak vysoce specializované nástroje používané například pro formální verifikaci. Pro programovatelnou logiku specifickým druhem verifikačních nástrojů jsou pak ještě hardwarové nástroje určené pro ladění ve skutečném obvodu.

Digitální simulátory se používají především pro funkční ověření popisu obvodu. Simulace výsledku syntézy a implementace v případě programovatelné logiky není až na výjimky nutná. Vstupem simulátoru jsou obvykle zdrojové soubory v HDL a vlastní testovací prostředí opět v HDL. Pokud je projekt nebo jeho části vytvářen jinými prostředky, je nutné je do HDL zkonvertovat.

Testovací prostředí zvané testbench obvykle zajišťuje propojení vlastního návrhu programovatelného obvodu do celého simulačního systému, generování vstupních signálů a dat pro buzení testovaného modulu a kontrolu výstupů. Kontrola správné funkce může být zajištěna automaticky přímo testovacím prostředím. Funkci jednodušších obvodů je možné provádět například sledováním vstupních a výstupních časových průběhů a stavů jednotlivých signálů v konkrétních místech obvodu a okamžicích simulace.

Řízení průběhu simulace, kompilace vstupních souborů a podobné pomocné úlohy je možné buď ručně z prostředí simulátoru, nebo pomocí simulačních skriptů. Většina digitálních simulátorů podporuje skriptování v jazyce TCL.

Digitální simulátory většinou podporují jazyky VHDL, Verilog, SystemVerilog a SystemC pro popis hardwaru a testovací prostředí. Složitější kontroly funkce, časování, posloupnosti signálů a podobně je možné realizovat pomocí assertions v některém z jazyků typu PSL, e, Open- Vera, SystemVerilog Assertions. Nejčastěji jsou podporovány assertions v PSL a SystemVerilog.

Do verifikace patří i součásti implementačních nástrojů určené pro analýzu výsledků a mezivýsledků implementačního procesu. Umožňují například vizualizaci či grafické zobrazení výsledných netlistů po jednotlivých implementačních krocích ve formě schémat nebo blokových diagramů. Vývojář si tak může udělat obrázek, jak skutečně vypadá hardware vygenerovaný z jeho vysokoúrovňového popisu.

Součástí integrovaných vývojových prostředí jsou dále obvykle prohlížeče usnadňující procházení a analýzu implementačních logů. Záznamy z průběhu implementace jsou většinou obrovské nepřehledné textové soubory, případně strukturované XML. Prohlížeče poskytují možnost strukturovaného prohlížení podle typu informace, specializované vyhledávání, filtrování různých druhů informací, jako jsou různé chyby a varování a podobně.

Statická časová analýza je velmi významnou součástí verifikačního procesu. Pro ověření skutečné funkčnosti návrhu je na stejné významové úrovni jako například ověření funkce pomocí simulace. Každý návrh programovatelné logiky musí obsahovat kromě vlastního popisu funkce také soubor omezujících podmínek, tzv. constraints, které definují například přiřazení pinů jednotlivým vstupně- -výstupním portům, správné nastavení elektrických parametrů vstupů a výstupů a kromě jiného také definují časové poměry v obvodu. Z časových constraints je nejdůležitější definice frekvencí hodinových signálů a požadavků na časování vstupních a případně i výstupních pinů. Dále je možné a často i nutné definovat relativní časové vztahy mezi různými hodinovými doménami, případně různé speciální nároky na časování v konkrétních místech obvodu, které nejsou ze samotného funkčního popisu zřejmé.

Nástroje pro statickou časovou analýzu použijí výstup implementace, časové constraints a charakterizační data použitého programovatelného obvodu a provedou kompletní analýzu časování všech použitých synchronních elementů v celém programovatelném obvodu. Výstupní netlist obsahuje kromě propojení jednotlivých obvodových prvků i jejich konkrétní umístění na ploše čipu a použité propojovací prostředky, takže časová analýza je schopná určit zpoždění všech spojů. Díky tomu, že programovatelné logické obvody jsou od výrobců plně charakterizovány včetně přesných modelů časování, stačí pro verifikaci návrhu splnit následující tři podmínky:

Na rozdíl od plně zakázkového vývoje ASIC pak odpadají další časově náročné kroky, jako jsou časové simulace po jednotlivých implementačních fázích. Díky plné charakterizaci programovatelných logických obvodů jsou časové simulace plně zastoupeny funkční simulací v kombinaci se statickou časovou analýzou.

Specifická skupina verifikačních nástrojů pro programovatelnou logiku umožňuje ladění a měření návrhu ve skutečném obvodu. Tyto nástroje sestávají ze tří částí. První je IP jádro, které se umístí do návrhu společně s vlastním projektem a zajišťuje přístup z vnějšího světa k jednotlivým signálům v návrhu. Druhou část tvoří hardware pro komunikaci mezi tímto jádrem a PC. Obvykle je tato část realizována pomocí JTAG kabelu. Třetí částí je pak software pro PC, který je schopen komunikovat s jádrem v programovatelném obvodu.

Celý výše popsaný systém se pak chová jako logický analyzátor. Uživatel si může nastavovat různé spouštěcí podmínky a provádět měření interních signálů v programovatelném obvodu. Je tak schopen ověřit výsledky simulace v reálném prostředí nebo odhalit chyby způsobené interakcí se skutečným okolím.