Programovatelné číslicové součástky jsou velmi důležité prvky současné elektroniky. Tyto obvody umožňují implementaci uživatelem definovaných logických funkcí podobně jako třeba zákaznické integrované obvody ASIC, ale s mnohem nižšími náklady na vývoj. Programovatelné logické obvody nejsou žádnou novinkou poslední doby. Za první programovatelné číslicové prvky je možné považovat paměti PROM, které se začaly objevovat na přelomu šedesátých a sedmdesátých let dvacátého století. Během posledních čtyřiceti let prošly programovatelné logické obvody postupným vývojem tak, že dnešní programovatelná hradlová pole jsou často plnohodnotnou náhradou zákaznických integrovaných obvodů a zároveň jsou společně s procesory na špičce vývoje polovodičových technologií.

Zkratka PLD (Programmable Logic Device) se používá pro souhrnné označení všech typů programovatelných logických obvodů. Podle vnitřní struktury je možné číslicové programovatelné součástky rozdělit do tří nebo čtyř hlavních skupin. Tou nejzákladnější a v tomto kontextu často opomíjenou skupinou PLD jsou paměti typu PROM. Ostatní PLD vznikly postupným vývojem a úpravami struktury právě z PROM. První, nejjednodušší a nejstarší skupinou skutečných PLD jsou obvody označované jako klasické PLD.

Rozšířením jejich vlastností vznikly komplexní PLD, obvykle značené CPLD. Zobecněním principů používaných v jednoduchých a komplexních PLD a zavedením nových struktur vznikla poslední skupina tvořená programovatelnými hradlovými poli FPGA.

Když necháme stranou diodová pole, která se používala již od dob elektronek a dala by se považovat za skutečně první programovatelné číslicové obvodové prvky, je první uživatelsky programovatelnou číslicovou součástkou paměť typu PROM (Programmable Read-Only Memory). Paměti tohoto typu realizují po naprogramování sadu kombinačních logických funkcí, kde adresová sběrnice představuje vstupy a datová sběrnice výstupy jednotlivých funkcí.

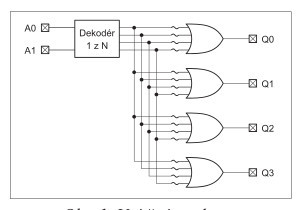

Obr. 1 Vnitřní struktura paměti typu PROM 16b ×4

Zjednodušená vnitřní struktura šestnáctibitové PROM se čtyřbitovým slovem je zobrazena na obrázku 1. Paměť je tvořena adresovým dekodérem následovaným programovatelnou maticí logických součtů. Adresový dekodér je kombinační logická funkce převádějící binární kód reprezentovaný aktuální adresou na kód 1 z N. Pouze jeden výstup dekodéru může být aktivní. Vlnovky na vstupech jednotlivých součtových hradel představují onen programovatelný prvek. Ten může být v závislosti na naprogramování reprezentován buď propojkou, nebo rozpojením.

Realizace vlastních programovatelných propojek záleží na konkrétní technologii. Původní bipolární PROM obsahovaly skutečné kovové propojky, které se při programování nevratně přepálily definovaným proudovým impulsem. V CMOS technologiích je propojka realizována jako přenosové hradlo (typicky N-MOS tranzistor) řízené buď plovoucím hradlem (EPROM, EEPROM), nebo jedním bitem konfigurační paměti (SRAM). Programovatelnost pomocí SRAM se ale týká až obvodů FPGA. V PROM a jednoduchých/ komplexních PLD se nepoužívá.

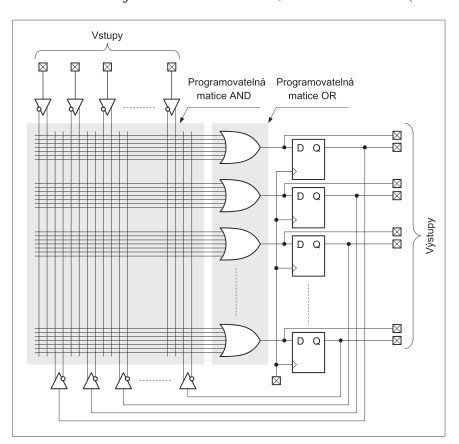

Klasické nebo také jednoduché PLD jsou nejjednodušší programovatelné logické obvody. Typická vnitřní struktura obvodu této kategorie je zobrazena na obrázku 2. Struktura vychází z paměti typu PROM, ale zobecňuje ji a rozšiřuje. Pevný adresový dekodér je nahrazen programovatelnou maticí logických součinů a struktura je rozšířena o sekvenční prvky a zpětné vazby.

Obr. 2 Vnitřní struktura obvodu typu PAL

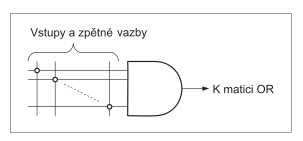

Pro zjednodušení schématu představuje každá vodorovná čára v programovatelné matici logických součinů vždy jedno součinové hradlo. Na vstupy každého hradla lze připojit téměř libovolnou kombinaci vstupních signálů, zpětných vazeb a jejich negací. V závislosti na výrobní technologii konkrétního programovatelného obvodu je ve skutečnosti maximální počet vstupů každého součinového hradla omezen. Principiální zapojení jednoho součinového hradla je znázorněno na obrázku 3.

Obr. 3 Součinové hradlo obvodu PAL

Kružnice na spojích vodičů obrázku 3 představují programovatelné spínače realizované podobně jako v PROM.

Počet vstupů do jednotlivých součtových hradel v matici OR je opět ve skutečnosti omezen a není možné realizovat funkci libovolného počtu vstupů. Programovatelnost matice OR není na schématu 2 vyznačena, ale bude realizována stejně jako u PROM na obrázku 1.

Jednotlivé obvody z kategorie klasických PLD se liší přítomností a programovatelností jednotlivých bloků obecné struktury podle obrázku 2. Obvody typu PLA (Programmable Logic Array) mají programovatelné obě matice. Výstupní registry byly přítomny v některých novějších obvodech. Dnes se obvody tohoto typu již nevyrábí. Obvody typu PAL (Programmable Array Logic) mají programovatelnou pouze matici logických součinů, zatímco matice logických součtů je pevná. Nejstarší typy se vyráběly bez výstupních registrů, poté začali výrobci přidávat výstupní registry JK, které byly postupně nahrazeny registry typu D. Zástupci kategorie PAL jsou součástky řad PAL, GAL, PEEL a PALCE. Některé typy se dosud vyrábějí a používají.

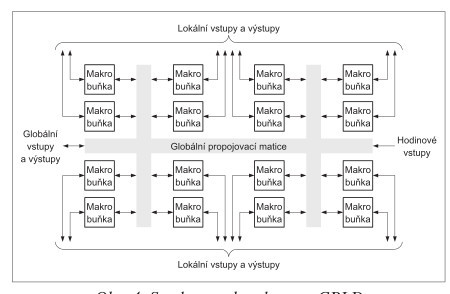

Přestože mohou být klasické PLD velmi univerzální obvodové prvky, složitost implementovatelných funkcí je velmi omezená. Logickým krokem výrobců PLD vedoucím k navýšení množství dostupných prostředků bylo sdružení více jednoduchých PLD struktur na jeden čip spolu s nutnými prostředky pro jejich vzájemné propojení. Takovéto obvody se obvykle označují jako CPLD (Complex Programmable Logic Device). Zjednodušená typická struktura obvodu CPLD je znázorněna na obrázku 4.

Obr. 4 Struktura obvodu typu CPLD

Jednotlivé makrobuňky (macrocells) CPLD jsou realizovány jako struktura PAL nebo PLA. Velikost obvodu CPLD se vyjadřuje počtem makrobuněk a počtem vstupů a výstupů jednotlivých makrobuněk. Konkrétní provedení a velikost jednotlivých makrobuněk se u jednotlivých výrobců obvykle liší, ale základní princip zůstává zachován.

Někteří výrobci programovatelné logiky již klasickou strukturu CPLD opustili a pod označením CPLD prodávají obvody s obecnější vnitřní strukturou blízkou FPGA. Od FPGA se tyto moderní CPLD odlišují obvykle velikostí (jsou výrazně menší), chybějícími speciálními funkčními bloky, menším množstvím globálních prvků a nižší maximální frekvencí hodinových signálů.

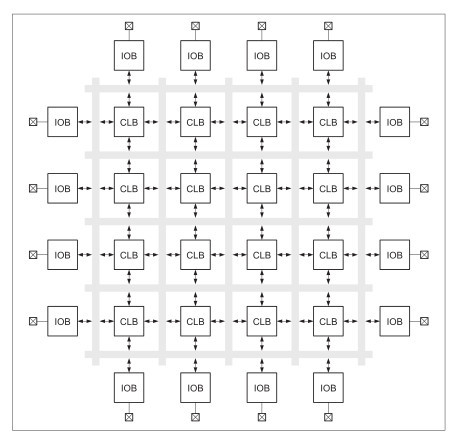

Obvody označované jako FPGA (Field Programmable Gate Array) mají ze všech uživatelem programovatelných obvodů nejobecnější strukturu a zároveň obvykle obsahují největší množství využitelných logických prostředků. Obrázek 5 znázorňuje velmi zjednodušenou typickou strukturu charakteristickou pro obvody typu FPGA.

Obr. 5 Zjednodušená struktura obvodu typu FPGA

Obvod FPGA se skládá z bloků vlastní programovatelné logiky CLB (configurable logic blocks), vstupně- výstupních buněk IOB (input-output blocks), programovatelné propojovací matice a konfiguračních prostředků řídících konkrétní nastavení jednotlivých bloků a jejich vzájemné propojení. Jednotliví výrobci navíc přidávají do FPGA další funkční bloky rozšiřující možnosti jejich obvodů. Dnešní typická programovatelná hradlová pole obsahují synchronní blokové paměti, bloky pro správu hodinových signálů založené na PLL nebo DLL, rychlá sériová vstupně-výstupní rozhraní, bloky pro realizaci aritmetických operací, mikroprocesory, paměťové řadiče a podobně.

Programovatelná hradlová pole jsou nejvýznamnější skupinou programovatelných logických obvodů. Jsou to nejuniverzálnější programovatelné logické obvody s nejobecnější vnitřní strukturou, ale také z hlediska pochopení a použití jsou nejsložitější. Popisu FPGA je věnována celá následující část.

Velice zjednodušená principiální struktura programovatelného hradlového pole na obrázku 5 vystihuje základní a nejdůležitější vlastnost FPGA, která je odlišuje od jejich předchůdců. Programovatelná hradlová pole jsou tvořena velkým množstvím menších konfigurovatelných bloků obecné logiky, které jsou navzájem propojitelné propojovací maticí. Komunikaci s okolním prostředím zajišťují vstupně-výstupní bloky. Kromě logických bloků, vstupně-výstupních bloků a propojovací matice obsahují FPGA ještě další speciální funkční bloky, které se u jednodušších PLD nepoužívaly. Jedná se například o bloky statických pamětí RAM, správy hodinových signálů, speciální vstupně-výstupní bloky a podobně.

Následující text nepopisuje žádné konkrétní FPGA, ale pouze obecné vlastnosti typické pro FPGA různých výrobců. Použité názvosloví je často převzato z terminologie používané firmou Xilinx, ale občas se v textu vyskytnou i výrazy pocházející od firmy Altera. Obvody obou hlavních světových výrobců FPGA sice vycházejí ze stejných obecných principů, ale konkrétní provedení a používaná terminologie se liší. Pro seznámení se se skutečnou realizací programovatelných hradlových polí je třeba prostudovat dokumentaci konkrétních produktů jednotlivých výrobců. Tato kapitola by měla pomoci lepšímu porozumění firemní dokumentaci.

Konfigurovatelné logické bloky jsou základním stavebním prvkem FPGA. Jedná se o bloky umožňující realizaci kombinačních i sekvenčních logických funkcí několika jednotek až desítek binárních vstupů s několika výstupy. Firma Xilinx označuje tyto základní bloky Configurable Logic Blocks (CLB), Altera používá označení Logic Array Blocks (LAB). Vzájemné propojení jednotlivých konfigurovatelných logických bloků zajišťuje programovatelná propojovací matice.

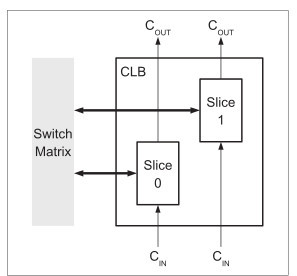

Obr. 6 Konfigurovatelný logický blok

Konfigurovatelné logické bloky jsou obvykle realizovány jako kombinace dvou menších bloků označovaných jako logické řezy, jak je znázorněno na obrázku 6. Název vychází z názvosloví firmy Xilinx – Slices, zatímco Altera nazývá tyto elementární bloky Adaptive Logic Modules (ALM). Zjednodušené obecné schéma jednoho řezu je na obrázku 7. Skutečná realizace elementárního bloku logiky je v dnešních FPGA mnohem složitější a řezy obvykle obsahují dvojnásobné množství základních logických prvků. Zjednodušené schéma je lepší pro pochopení základní struktury.

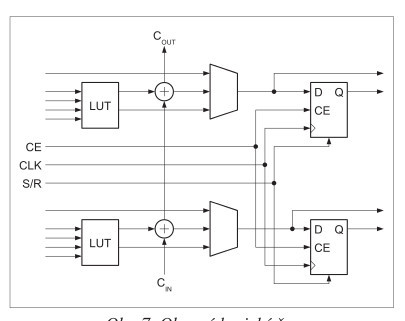

Obr. 7 Obecný logický řez

Typický logický řez se skládá ze čtyř vzájemně se doplňujících částí:

Programovatelná logická tabulka LUT (look-up table) slouží k realizaci libovolné kombinační logické funkce. Jedná se v podstatě o paměť typu RAM, jejíž obsah je při běžném použití pevně dán konfiguračními daty. Realizuje tedy jednu nebo dvě binární funkce několika (typicky čtyř, pěti nebo šesti) vstupních binárních proměnných. Kromě této základní funkce umožňují LUT obvykle realizaci i jiných typů funkčních bloků, jako jsou malé paměti RAM a ROM nebo posuvné registry.

Řetězec rychlého šíření přenosu (carry chain) umožňuje vytvoření různých aritmetických obvodů, jako jsou například sčítačky. Zatímco běžné vstupy a výstupy logických řezů jsou připojeny k pomalé globální propojovací matici, vstup a výstup přenosu CIN a COUT jsou přímo propojeny se sousedními konfigurovatelnými logickými bloky ve stejném sloupci.

Programovatelné multiplexery umožňují realizaci logických funkcí více proměnných, než je šířka jedné LUT. Funkce je pak realizována zkombinováním výstupů několika LUT v jednom logickém řezu pomocí multiplexerů. Obdobné funkcionality je sice možné dosáhnout kombinací několika logických bloků, ale propojení mezi jednotlivými CLB je mnohem pomalejší než přímý spoj mezi LUT a multiplexery. Zjednodušené schéma na obrázku 7 neobsahuje multiplexer umožňující toto využití logického řezu, protože by schéma bylo nepřehledné. Tento přidaný multiplexer by byl umístěn mezi stávajícími dvěma multiplexery na schématu a jeho výstup by byl dále různě kombinován s výstupy druhých dvou.

Registry v logických řezech umožňují realizaci sekvenčních logických funkcí. Při konfiguraci řezu je obvykle možné nastavit vlastnosti jednotlivých registrů, jako třeba využití clock-enable, polarita a typ set/reset vstupu a podobně. Speciální vstupy pro registry na obrázku 7 jsou obvykle sdíleny všemi registry v rámci jednoho konfigurovatelného logického bloku nebo alespoň v rámci řezu. To znamená, že všechny registry musí používat stejný hodinový signál, clock-enable i reset. Ne každý registr však musí clock-enable a reset používat, případně může reset využívat jiným způsobem než ostatní registry.

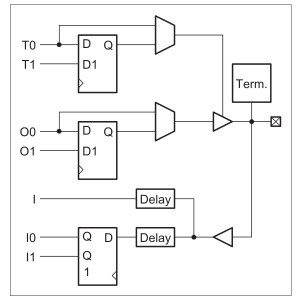

Vstupně-výstupní bloky (IOB) zprostředkovávají spojení mezi FPGA a vnějším prostředím. Každý vnější signál vstupuje do FPGA prostřednictvím IOB a každý výstupní signál opouští FPGA opět přes IOB. Zjednodušené schéma vstupně-výstupního bloku je na obrázku 8.

Obr. 8 Vstupně-výstupní blok

Vstupně-výstupní blok obsahuje vstupní a výstupní registry, budiče a přijímače, zpožďovací linky, obvody impedančního přizpůsobení a ochranné obvody. Vstupní i výstupní registry jsou u všech dnešních FPGA realizovány pomocí kombinace dvou registrů tak, aby umožňovaly vstup a výstup DDR signálů. Samozřejmě mohou být nakonfigurovány do běžného režimu SDR.

Výstup signálu je realizován volitelným výstupním registrem následovaným třístavovým budičem. Výstup budiče je přímo připojen na pin FPGA. Třístavový budič je řízen druhou datovou cestou podobnou datové, která opět obsahuje volitelný DDR/SDR registr.

Vstupní externí signál je přiveden na konfigurovatelný přijímač, ve schématu představovaný pouze jednoduchým budičem. Ve skutečnosti se jedná o různé přijímače pro jednotlivé podporované I/O standardy následované multiplexerem. Výstup přijímače může být přes konfigurovatelnou zpožďovací linku přiveden přímo na propojovací matici FPGA nebo na DDR/SDR vstupní registr a z něho teprve na propojovací matici. Pro vstup diferenciálních signálů obsahuje přijímač ještě druhý vstup připojený do sousedního I/O bloku. Programovatelné zpožďovací linky umožňují realizaci časového posunu vstupního signálu. Tím je možné například korigovat vzájemný fázový posun signálů, případně posun signálu vůči hodinám.

Ochranné obvody, které nejsou na zjednodušeném schématu nakresleny, chrání logiku IOB před poškozením z vnějšího světa v důsledku EMI nebo nesprávného použití či zapojení. Obvody impedančního přizpůsobení umožňují přizpůsobit vnitřní impedanci budiče v FPGA impedanci externího vedení nebo zakončit externí vedení správně přizpůsobenou impedancí. Novější FPGA podporují dynamické řízení zakončovací impedance, což je důležité například pro připojení různých variant DDR a QDR rozhraní nebo třeba PCIe.

Vzájemné propojení jednotlivých funkčních bloků FPGA zajišťují různé programovatelné propojovací matice a spoje. Typické hradlové pole obsahuje tři různé typy propojovacích prostředků:

Globální propojovací prostředky jsou nejuniverzálnější a umožňují vzájemné propojení libovolných funkčních bloků FPGA. Jsou realizovány jako několik vrstev různě organizovaných spojů s propojovacími maticemi pro jednotlivé funkční bloky. Vlastní organizace spojů se liší mezi výrobci i mezi jednotlivými produktovými řadami. Často bývají spoje organizovány jako sada horizontálních a vertikálních vodičů různých délek. Programovatelné propojovací matice umožňují připojení vstupů a výstupů funkčních bloků k jednotlivým propojovacím vodičům. Přestože globální propojovací prostředky poskytují nejvíce stupňů volnosti v propojení jednotlivých bloků, mají zase některé nevýhody. Každý globální spoj je poměrně dlouhý vodič s velkým množstvím programovatelných spínačů, a tedy velkou kapacitou, což se projeví na rychlosti šíření signálů.

Lokální propojovací prostředky umožňují propojení pouze sousedních funkčních bloků. Jedná se například o propojení řetězců šíření přenosu logických řezů, propojení diferenciálních signálů vstupně-výstupních bloků, ale i krátké rychlé spoje mezi sousedními konfigurovatelnými logickými bloky. Lokální spoje jsou mnohem kratší, s méně spínači a nižší kapacitou než spoje globální. Lokální spoje tedy způsobují mnohem nižší zpoždění signálů než globální spoje.

Speciální propojovací prostředky slouží pro spojení mezi vyhrazenými vstupy a výstupy funkčních bloků. Jedná se především o spoje určené k šíření hodinových signálů a dalších globálních signálů typu reset, tristate apod. Tyto speciální propojovací prostředky jsou optimalizovány tak, aby způsobovaly co nejmenší zpoždění procházejících signálů. Samozřejmě nemohu být použity pro běžné signály, ale pouze pro jeden konkrétní typ signálů. Například hodinové spoje mohou být připojeny pouze k vyhrazeným hodinovým vstupům a výstupům jednotlivých funkčních bloků, ale už ne k ostatním běžným portům. Množství speciálních propojovacích prostředků v FPGA je obvykle velmi omezené a často bývají realizovány ve dvou různých provedeních jako globální a lokální podobně jako běžné signálové spoje.

Dnešní programovatelná hradlová pole obsahují další, často jednoúčelové, funkční bloky usnadňující použití FPGA. Typickými zástupci této kategorie jsou blokové paměti, násobičky a jiné aritmetické obvody, obvody pro správu a generování hodinových signálů, sériové transceivery atd.

Blokové paměti jsou obvykle dvouportové statické paměti RAM o kapacitě jednotek až desítek kilobytů a s konfigurovatelnou šířkou adresových a datových sběrnic. Takovýto paměťový blok je vysoce univerzální. Může být použit jako jednoportová i dvouportová paměť typu RAM i ROM. Datové sběrnice mohou být obvykle nastaveny na šířku 1, 2, 4, 8/9, 16/18, 32/36 nebo 64/72 bitů. Čísla za lomítkem představují varianty s paritními bity. Dvouportové blokové paměti usnadňují realizaci různých typů speciálních pamětí, jako jsou FIFO, kruhové buffery, CAM apod.

Aritmetické obvody jsou reprezentovány obvykle celočíselnými násobičkami, případně složitějšími DSP bloky umožňujícími realizaci náročnějších matematických operací v jednom hodinovém cyklu. Typickým příkladem jednodušších, ale nejčastějších operací realizovaných pomocí DSP bloků je MAC (Multiply-and-Accummulate), což je základní operace číslicové filtrace a téměř všech DSP algoritmů.

Bloky pro správu a generování hodinových signálů jsou založeny na PLL (phase-locked loop – fázový závěs) nebo DLL (delay-locked loop). Složitější hodinové bloky ve větších FPGA často obsahují i několik PLL a DLL. Tyto bloky nabízejí funkce, jako je syntéza a dělení hodinových signálů, generování fázově posunutých hodin, kompenzace vnitřních i vnějších zpoždění a fázových posunů a podobně. Vstupy a výstupy těchto bloků jsou obvykle připojeny přímo ke speciálním spojům určeným pro šíření hodinových signálů. Na rozdíl od předchozích dvou typů speciálních funkčních bloků nejdou hodinové obvody jednoduše nahradit běžnou logikou FPGA.

Sériové transceivery umožňují poměrně jednoduchou realizaci velmi rychlých sériových rozhraní. Blok transceiveru obvykle obsahuje diferenciální budič a přijímač, serializer a deserializer, kodér a dekodér, extraktor hodinového signálu a další pomocné obvody. Pomocí transceiverů je možné sériově komunikovat s okolím rychlostmi v řádech jednotek až desítek gigabitů za sekundu. Interní rozhraní v FPGA je pak realizováno synchronními paralelními daty s mnohem nižší hodinovou frekvencí. Sériové transceivery jsou nezbytné pro realizaci mnoha standardních sériových rozhraní, jako jsou například PCIe, XAUI pro 10Gbps Ethernet a mnohá další.

Z ostatních funkčních bloků, které se vyskytují v FPGA si zaslouží zmínku řadiče pamětí a mikroprocesory. Některá hradlová pole obsahují hotový řadič dynamických pamětí, který obvykle podporuje paměti typu SDR, DDR, DDR2 a DDR3 SDRAM. Hotový blok řadiče uspoří mnoho logických prostředků a často významně zvýší datovou propustnost externí dynamické paměti oproti realizaci řadiče pomocí běžné logiky. Zabudovávání mikroprocesorů do FPGA není žádná novinka posledních let. Některé starší high-end FPGA obsahovaly mikroprocesor PowerPC řady 4xx nebo ARM s instrukční sadou verze 2. Po několikaleté přestávce se výrobci k této možnosti začali navracet a na trhu se objevují nová FPGA s vestavěnými vícejádrovými procesory ARM Cortex-A9. Tvoří tak zajímavou alternativu k běžným SoC svou programovatelností, ale i FPGA díky mnohem výkonnějšímu CPU než běžné soft-core procesory.

jp@sensor-to-image.cz