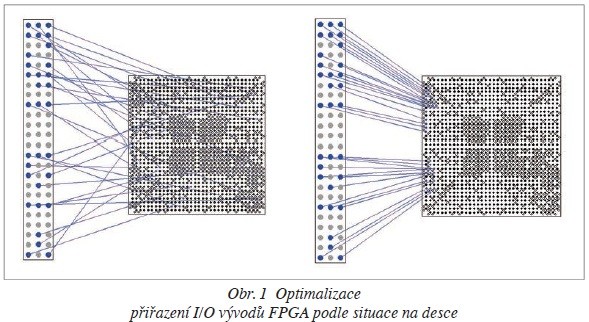

Dnes mohou mít FPGA součástky přes 1 000 vývodů, a tak správné přiřazení jejich I/O vývodů hraje při návrhu desek důležitou roli. Je třeba, aby propojení s ostatními součástkami bylo co nejoptimálnější. Software I/O Designer firmy Mentor Graphics, o kterém jsme se na stránkách tohoto časopisu již zmiňovali [1, 2], je určen právě pro tento typ úloh. Stručně řečeno, I/O Designer umožňuje souběžný návrh FPGA z pohledu přiřazení vývodů s návrhem desky plošných spojů tak, aby spoje mezi FPGA a navazujícími součástkami byly z hlediska provedení co nejjednodušší. I/O Designer podporuje FPGA od společností Actel, Altera, Lattice a Xilinx. Další informace jsou k dispozici na stránkách společnosti Mentor Graphics [3].

Na webových stránkách společnosti Mentor Graphics [4] je uvedeno několik příkladů úspěšného zavedení programu I/O Designer u renomovaných firem, z nichž dále stručně prezentujeme dva – společnost Agilent a Broadcom Corporation.

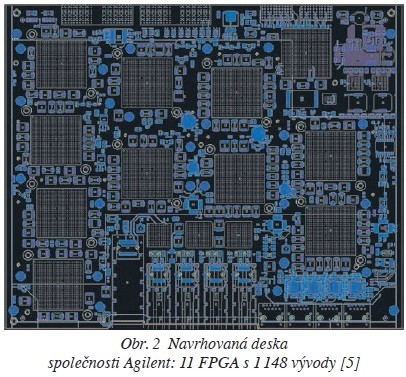

Společnost Agilent byla postavena před úkol umístit a zapojit jedenáct FPGA s 1 148 vývody na desku, přičemž každé FPGA mělo přiřazeno celou řadu omezujících pravidel určených pro návrh desky. Bylo zřejmé, že běžnými postupy, používanými v návrhu FPGA a desek by daný úkol byl řešitelný velmi obtížně a pomalu. Odhad naznačil, že jenom vhodné přiřazení I/O vývodů by u každého z jedenácti FPGA trvalo asi 4–8 týdnů. Použitím programu I/O Designer se potřebná doba snížila na 1–2 týdny a ještě umožnila zrychlit návrh desky díky jednodušším spojům. Celý projekt tak mohl být dokončen za 10 měsíců, podstatně dříve, než bylo původně plánováno.

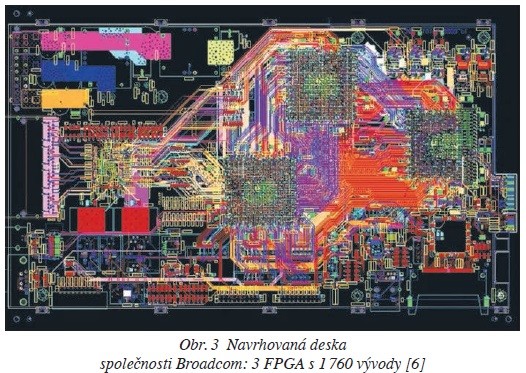

K rozhodnutí o využití programu I/O Designer přispělo zhodnocení náročnosti úkolu a možností jeho splnění: deska pro 12" PCIE kartu se třemi FPGA Virtex 6 Xilinx po 1 760 vývodech a s řadou omezení včetně počtu signálních vrstev na 8 a požadavku na stejně dlouhé spoje v dlouhém seznamu dávala minimální naději na úspěšné dokončení v daném termínu. Zavedení nového, pro ně dosud neznámého programu bylo riskantní záležitostí, která se ovšem vyplatila – projekt byl dokončen za 320 hodin, místo plánovaných 960. Deska měla také podstatně méně průchozích via otvorů, než bylo původně odhadnuto na základě podobných návrhů.

Zájemci o program I/O Designer se mohou na stránkách společnosti Mentor Graphics [4] podívat na několik webinářů, které srozumitelně vysvětlují princip, způsob práce i výhody tohoto programu.

[1] Optimalizace návrhu FPGA s ohledem na návrh DPS (DPS Plošné spoje od A do Z č. 2/2011)

[2] Optimalizace přiřazení vývodů FPGA (DPS Elektronika od A do Z č. 1/2013)

[3] www.mentor.com/pcb/xpedition/fpga-io/?sfm=auto_suggest

[4] www.mentor.com/pcb/xpedition/fpga-io/resources#?filter=&start=1&limit=99