V předchozích příspěvcích [1] a [2] byl čtenář seznámen s obecnými vlastnostmi, výhodami a nevýhodami simulace číslicového obvodu na hradlové úrovni (back-annotated gate level simulation, timing simulation) a technickými detaily modelování obvodu na této úrovni abstrakce. Tento článek sérii o simulacích na hradlové úrovni uzavírá a shrnuje několik doporučení, jejichž důsledné dodržování by mělo provádění takových simulací zjednodušit – pohlédneme zde na přípravu simulací z pohledu pracovních postupů. I nyní je text nezávislý na návrhové platformě a prezentované poznatky jsou aplikovatelné jak při návrhu zákaznických integrovaných obvodů, tak při návrhu číslicových systémů na FPGA obvodech.

Provádění simulace na hradlové úrovni je náročné na čas a nervy návrháře, i když vše funguje, jak má. Aby byla zátěž návrháře spojená s prováděním simulací co nejmenší, doporučujeme před spuštěním simulace udělat některé přípravné práce:

Jak na resynchronizátory

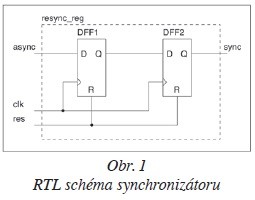

Resynchronizátor (viz obrázek 1) slouží pro synchronizaci asynchronního signálu do lokální hodinové domény, a tak z principu věci na jeho vstupu (klopný obvod DFF1, vstup D, v obrázku 1) běžně dochází k porušení předstihu či přesahu (setup time violation, hold time violation, více viz [4] a [5], kapitola 11). Protože modely klopných obvodů dodržení předstihu a přesahu během simulace kontrolují, byl by výstup Q registru DFF1 nastaven za těchto podmínek do stavu X pro příští hodinový cyklus. To může mít nežádoucí dopad na další běh simulace – může dojít k zaplavení simulovaného návrhu stavem X a způsobit nefunkčnost obvodu v simulaci. Generování stavu X je zde zbytečně pesimistickým opatřením. Proto je běžně kontrola předstihu a přesahu na DFF1 v hradlových simulacích vypínána. Ale pozor: bavíme se pouze o DFF1, na DFF2 k porušení předstihu a přesahu nesmí docházet a není důvod kontroly vypínat.

Dobrou praxí je před spuštěním simulace na hradlové úrovni připravit seznam všech resynchronizátorů v návrhu – to by měla být práce návrhářů RTL kódu. Potom je třeba pro každý resynchronizátor identifikovat registr DFF1 v netlistu a vypnout na něm příslušné kontroly časových parametrů. Tento úkol může být poněkud obtížný, pokud návrháři obvodu nedodržují jednoduché konvence: základním pravidlem je, že resynchronizátor má být implementován jako samostatná entita se jménem obsahujícím např. resync v názvu. Tak je pak možné resynchronizátory jednoduše vyhledat v návrhu například příkazem grep nebo hledáním řetězce v Total Commanderu a současně je sníženo riziko záměny resynchronizátoru s běžným posuvným registrem se vstupem synchronním k hodinám apod.

Vypnutí kontroly předstihu a přesahu na klopném obvodu DFF1 je specifické podle použitého simulátoru, prostudujte si proto dokumentaci k vašemu nástroji. Univerzálním postupem nezávislým na simulátoru je ruční editace záznamu pro předstih a přesah v SDF souboru (více viz [6], kapitola 7.2.4).

Vypínání kontrol dodržení časových parametrů klopných obvodů v návrhu je delikátní operace, která může při nesprávném provedení vést i k přehlédnutí vážných chyb v návrhu. Dobrou praxí je provést review všech vypnutých časových kontrol zkušeným návrhářem, který na projektu nepracuje a má tak „čerstvé oči“ – a vše pečlivě zdokumentovat. A pozor: klopný obvod, na kterém byla vypnuta kontrola předstihu a přesahu při porušení časových parametrů svůj výstup ponechá v předchozím stavu (viz např. [7], strana 36). Ve skutečnosti by ale mohl klopit, simulace tedy nemusí odpovídat reálnému chování návrhu v FPGA obvodu. Částečným řešením může být lepší modelování resynchronizátoru na RTL úrovni, kde tento jev lze podchytit, ale to už je nad rámec tohoto textu – viz například [6], kapitola 7.7.

V [1] jsme se dotkli potřeby správně vybrat sadu testů pro verifikaci obvodu na hradlové úrovni, protože simulace na hradlové úrovni může běžet významně pomaleji než na RTL úrovni a je celkově náročnější na provádění. Obecně je třeba (viz např. shrnutí v [8]) spouštět takovou skupinu testů, aby byly jak vyzkoušeny všechny jeho hlavní funkce, tak i bloky (funkční a strukturní pokrytí). Dále množství spouštěných testů závisí na tom, jak velkou důvěru vkládáme ve výsledky statické časové analýzy a jak moc je navrhovaný systém synchronní. Uveďme tedy základní pravidla pro výběr skupiny testů pro simulaci na hradlové úrovni:

Pro usnadnění výběru testů a minimalizace rizika, že část obvodu zůstane spouštěnými simulacemi nepokrytá, autor z vlastní praxe čtenáři doporučuje vytvořit praktickou tabulku například v Excelu – matici pokrytí obsahující na jedné ose jednotlivé důležité funkce systému, na druhé ose vybrané testy. Ta bude názorně ukazovat, který test pokrývá kterou funkci či aktivuje jaký režim návrhu. Závěrem poznamenejme, že ideální stav je v každém případě dosažení maximálního pokrytí – tedy pokud můžete spouštět všechny testy, které spouštíte na RTL úrovni i na hradlové úrovni, čiňte tak.

Skutečná rychlost obvodových prvků v číslicovém systému je závislá na třech hlavních faktorech: napájecím napětí (V – voltage), teplotě (T – temperature) a výrobním procesu (P – process – tento parametr zohledňuje variace rychlosti způsobené odchylkami ve výrobním procesu). Protože simulace na hradlové úrovni simuluje reálná zpoždění v obvodu, je třeba zvolit několik vhodných trojic PVT podmínek, pro které budou vypočtena zpoždění logických prvků a spojů, jež se nakonec použijí pro simulaci, více viz [2]. Výběr PVT podmínek pro generování časového modelu obvodu pro simulaci na hradlové úrovni je dán zejména extrémy skutečných fyzikálních podmínek, za kterých bude navrhovaný číslicový obvod pracovat v konečném produktu. Rozumné je simulace spouštět alespoň ve dvou rozích:

Všechny testy spouštěné na hradlové úrovni jsou tedy spouštěny alespoň dvakrát – v rychlém i pomalém rohu; Xilinx dokonce ve svých materiálech doporučuje spouštět všechny simulace čtyřikrát; více detailů viz dokument [7], strana 49 a 50.

Provádění simulací na hradlové úrovni často vyžaduje úpravy verifikačního prostředí použitého pro simulace na RTL úrovni. Úpravy mohou být jak strukturní (často na rozhraní pro top level entitu návrhu – tzv. DUT, Design Under Test), tak funkční (nejčastěji kvůli problémům s propagačním časem obvodu).

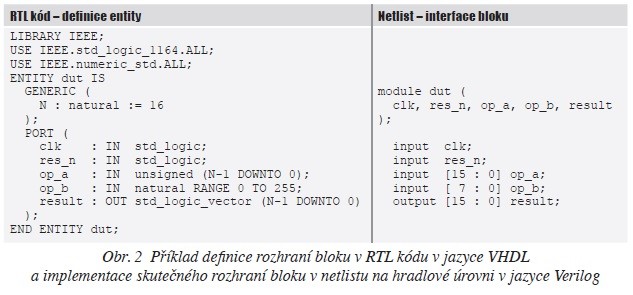

RTL syntéza je proces, při kterém je abstraktní RTL popis převeden do konkrétního schématu užívajícího konkrétní buňky v příslušné technologii. Jeden z výsledků syntézy je také odstranění veškeré abstrakce z rozhraní číslicového systému. Přibližme si to na příkladu kódu v obrázku 2.

V levém sloupci je uveden příklad definice rozhraní bloku na RTL úrovni v jazyce VHDL. Všechny použité konstrukce jsou bez problémů syntetizovatelné. V pravém sloupci je rozhraní bloku po syntéze v netlistu v jazyce Verilog. Všimněte si, že:

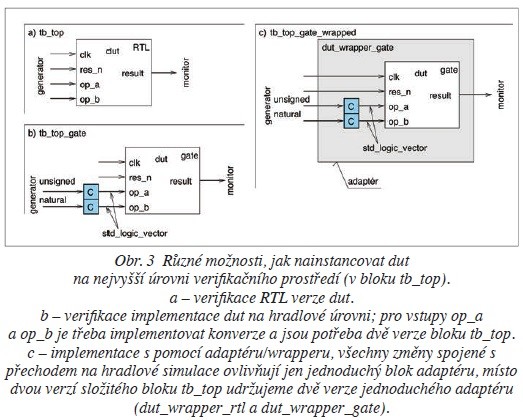

Blok dut je ve verifikačním prostředí instancován, jak je znázorněno na obrázku 3a. Změna rozhraní bloku po syntéze nutí návrháře používat různé verze bloku tb_top (implementace nejvyšší úrovně hierarchie ve verifikačním prostředí) pro simulace na RTL a hradlové úrovni; změna datových typů vstupů a výstupů bloku vede na nutnost konvertovat interní signály na jiné typy a zpátky, viz obrázek 3b. Doporučit lze následující:

..jpg)

Změnám na nejvyšší úrovni verifikačního prostředí se s přechodem od RTL k hradlovým simulacím tedy nevyhneme. To je mrzuté, protože blok tb_top může být dosti složitý a udržovat jeho dvě téměř identické kopie může být jednak časově náročné a dále to zvyšuje riziko zavlečení chyb do návrhu. Lze proto doporučit implementaci znázorněnou na obrázku 3c, kde je mezi dut a tb_top vložena další úroveň hierarchie – blok adaptéru dut_wrapper. Jeho jedinou funkcí je úprava signálů z rozhraní bloku na RTL úrovni na rozhraní netlistu. Dosáhne se tak dobré dekompozice návrhu, vše, co souvisí s přizpůsobením verifikačního prostředí požadavkům rozhraní dut, je lokalizované v adaptéru (wrapper). Ten má dvě verze – jednu pro RTL kód, druhou pro hradlovou implementaci entity. Není pak třeba udržovat dvě kopie bloku tb_top.

Používáte-li prostředí Xilinx Vivado, lze dvě verze bloku pro RTL a hradlovou simulaci dosti snadno udržovat pomocí tzv. simulačních setů (simulations sets, viz [7], strana 15). Podpora v jiných simulátorech bude odlišná, zde odkážeme na dokumentaci k vašemu nástroji; pomoci může také použití VHDL konstrukce CONFIGURATION (viz například [9]).

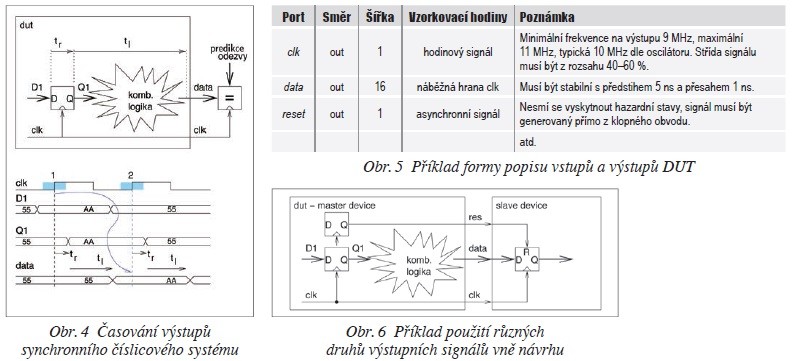

Jednou ze základních funkcí verifikačního prostředí je kontrola správnosti odezev číslicového obvodu na předkládané stimuly. Zatímco na RTL úrovni obvod reaguje okamžitě a vše se děje s „nekonečně rychlou“ odezvou, na hradlové úrovni jsou simulována reálná zpoždění obvodových prvků a obvod tak bude reagovat jako ve skutečnosti, tedy později – viz obrázek 4 s příkladem časování. Dále pokud jsou některé výstupy dut generované přímo z kombinační logiky, můžeme na nich pozorovat přítomnost hazardních stavů (tzv. glitches). Z autorovy zkušenosti lze doporučit před implementací automatické kontroly odezev obvodu rozdělit primární výstupy dut do těchto skupin (například ve formě tabulky, jako je na obrázku 5):

Článek shrnul několik doporučení, jak postupovat během přípravy simulací na hradlové úrovni a při implementaci verifikačního prostředí, která mohou návrháři ušetřit část problémů se simulacemi na hradlové úrovni. Je zřejmé, že příprava těchto simulací může vést až k částečnému přepracování verifikačního prostředí; autor proto doporučuje na potřebu provádění simulací na hradlové úrovni myslet od samého začátku návrhu a vše implementovat tak, aby potřeba pozdějších změn byla minimalizována. Pomoci k tomu může také provádění zkušebních (tzv. pipecleaning) simulací za běhu projektu, kdy RTL kód sice není ani kompletní ani odladěný, ale přesto lze už objevit závažnější problémy a postupně je odladit dříve než ve stresu před koncem projektu. Kromě problémů s verifikačním prostředím také není vyloučeno, že objevíte závažné problémy v RTL kódu, které by se jinak odhalily až při finální implementaci.

Problematika simulací na hradlové úrovni je značně rozsáhlá a bylo třeba ji vzhledem k omezenému rozsahu textu značně zjednodušit. Čtenáři zde proto doporučujeme studium další literatury, jako inspirace může sloužit seznam použité literatury níže.

[1] ŠŤASTNÝ, Jakub. Simulace číslicových obvodů na hradlové úrovni. DPS Elektronika od A do Z, květen/červen 2015, s 8–11.

[2] ŠŤASTNÝ, Jakub. Simulace číslicových obvodů: model návrhu. DPS Elektronika od A do Z, leden/únor 2016, s 6–12.

[3] ŠŤASTNÝ, Jakub. Simulace číslicových obvodů: triky i úskalí simulace. DPS Elektronika od A do Z, březen/duben 2015, s 20–23

[4] GINOSAR, R. Metastability and Synchronizers: A Tutorial. IEEE Design & Test of Computers, Vol. 28, No. 5, pp. 23–35. Dostupné též z: http://webee.technion.ac.il/~ran/papers/Metastability-and-Synchronizers.IEEEDToct2011.pdf

[5] ŠŤASTNÝ, Jakub. FPGA prakticky. Praha : BEN-technická literatura, 2011. 200 s.

[6] CUMMINGS, Clifford. Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog. In: SNUG 2008 Boston. [vid. 13. prosince 2015] Dostupné z http://www.sunburst-design.com/papers/CummingsSNUG2008Boston_CDC.pdf

[7] XILINX. Vivado Design Suite User Guide Logic Simulation,UG900, verze 2014.2 (4. července 2014)

[8] Gate Level Simulations : A Necessary Evil – Part 1,2 and 3 [online] [vid. 13. prosince 2015] Dostupné z http://whatisverification.blogspot.cz/2011/06/gate-level-simulationsnecessary-evil.html

[9] DOULOS [online]. Configurations. [vid. 13. prosince 2015] Dostupné z: https://www.doulos.com/knowhow/vhdl_designers_guide/configurations_part_1/