V dnešním pokračování seriálu o platformě Zynq®-7000 Xilinx® All Programmable SoC dokončíme návrh periferie jednoduchého řadiče displeje v jazyce Verilog. Ukážeme si také, jak syntetizovaný obvod připojit k procesorové části systému Zynq tak, aby jej bylo možné řídit z uživatelské aplikace. Naším cílem je vývoj aplikace, kterou si díky modulu SQM4-ZY7 a prototypové platformě SQM4-EasyBoard můžete s obvodem Zynq XC7020 vyzkoušet sami bez nutnosti investovat čas a peníze do návrhu složitých schémat a desek plošných spojů.

V minulém dílu jsme pro obvod řadiče připravili jednoduchý dekodér sběrnice AXI-Lite, která nám dnes poslouží k napojení na procesorové jádro Zynq. Dále máme připraveny řídicí registry řadiče a schematický návrh stavového stroje pro generování signálů HSYNC a VSYNC.

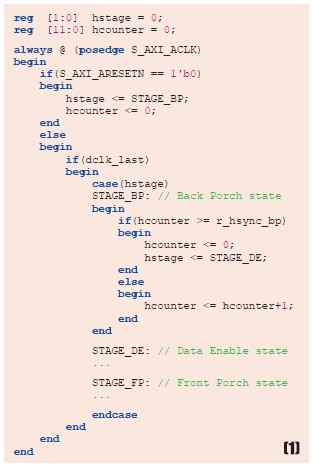

Jak je zřejmé z obrázku 1, který ukazuje zkrácený kód pro generování signálu HSYNC, je přepis logiky stavového stroje do jazyka Verilog velmi jednoduchý. Pomocný registr hstage uchovává číselnou hodnotu stavu – nabývá jedné ze symbolických hodnot STAGE_BP, STAGE_DE a STAGE_FP. Registr hcounter pak hraje roli čítače ,c‘ popsaného v grafické reprezentaci stavového stroje z minulého dílu našeho seriálu. Kód pro zpracování stavů DE a FP je pro zjednodušení z výpisu odstraněn, jelikož je prakticky stejný jako u stavu BP – jen se u každého z těchto stavů použijí jiné registry pro mezní hodnotu čítače. Kompletní kód i všechny další projektové soubory jsou uživatelům modulu SQM4- -ZY7 k dispozici na www.sqm4.com.

Registry stavového stroje použijeme k definici řídicích signálů pro samotný displej. Klíčové rovnice najdete na obrázku 2. Všimněte si, že jsou zde použity už jen signály deklarované jako wire; jedná se totiž o prostou kombinační logiku, bez nutnosti ukládání stavu do dalších registrů. Signály displeje HSYNC a VSYNC mají být dle požadavků displeje aktivní v definovaném intervalu, který je kratší nebo maximálně stejně dlouhý jako „Back porch“ fáze. Signál DE bude aktivní v časových intervalech, kdy se prolínají horizontální a vertikální datové fáze.

K dosažení šachovnicového vzoru zvolené barvy musíme na R, G a B výstupech generovat střídavě požadovanou barvu z uživatelského registru r_bkgnd a černou barvu vyjádřenou číselně jako 0. Díky rovnici signálu chess a kráse bitové operace XOR bude mít každé pole velikost přesně 16 pixelů, přičemž barevná pole se s černými budou střídat v přesném šachovnicovém vzoru. Celý vzor pak lze dodatečně invertovat signálem r_ctrl_inv z řídicího registru.

Kód z obrázku 3 už jen vypočtené signály přiřadí výstupním „pinům“ periferie, takže je bude možné použít v nadřazeném návrhu s procesorovým systémem.

Pro připomenutí zopakujeme, že v předchozích dílech seriálu jsme řadič displeje vyvíjeli ve Vivado projektu nazvaném „sdisp“ odděleně od hlavního projektu, v němž jsme mimo jiné připravili i blokový diagram „ps“ reprezentující procesorový systém a jeho periferie. Nyní je již velmi snadné zapouzdřit modul „sdisp“ do tzv. „IP komponenty“, která je reprezentována XML souborem „component. xml“ ve standardním formátu IP-XACT. Vytvořit komponentu je otázka jen několika kliků myši. Volbou „Create and Package IP...“ spustíme průvodce celým procesem, v jehož úvodu zvolíme nejjednodušší možnost, a to vytvořit IP blok z existujícího adresáře a z našich zdrojových souborů. Průvodce ve zdrojových souborech „sdisp“ detekuje všechny potřebné informace; nalezne tam mimo jiné i definici AXI-Lite Slave sběrnice a definici všech dalších vstupně výstupních pinů periferního modulu.

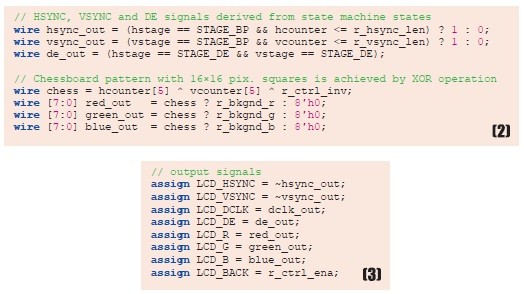

Soubor component.xml pak plně reprezentuje rozhraní modulu a cesty k jeho zdrojovým souborům. Vytvořená komponenta bude k dispozici pro vložení do jiných projektů pod názvem a verzí, které jsme jí přiřadili, a s automaticky vygenerovanou schematickou značkou, jak je vidět na obrázku 4.

Pokud bychom někdy v budoucnu potřebovali zdrojový kód modulu změnit a aktualizovat komponentu v projektech, kde byla použita, není již nutné znovu spouštět průvodce. Postačí, když v nástroji Vivado otevřeme soubor component. xml jako typ „IP-XACT IP Definition File“, zvýšíme verzi a komponentu znovu vygenerujeme. Jakýkoliv projekt, který kdy naši komponentu použil, bude o změně verze informován a při nejbližší příležitosti nabídne její aktualizaci.

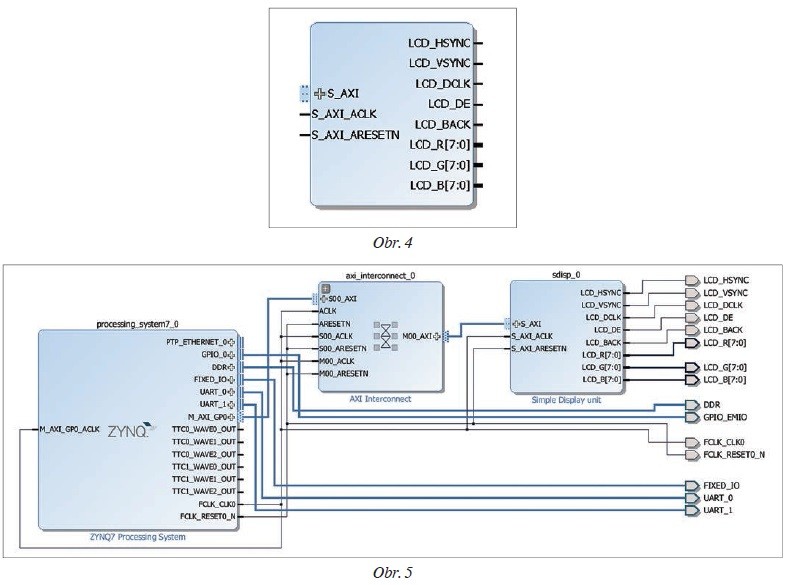

Nyní máme vše připraveno k vložení řadiče displeje do blokového diagramu procesorového systému v našem hlavním projektu. Z minulosti již máme blokový diagram vytvořen a máme zde již správně nakonfigurovaný blok reprezentující procesorová jádra Zynq a jeho vestavěné periferie jako např. UART, GPIO a DDR.

V nastavení projektu v sekci IP Repository Manager zaregistrujeme cestu k souboru component.xml reprezentující řadič displeje „sdisp“. V editoru blokového diagramu pak tuto novou periferii vložíme pomocí příkazu „Add IP“. A pokud jsme vše udělali správně, objeví se na ploše diagramu stejná schematická značka periferie, jakou jsme už viděli na obrázku 4.

Poslední úkol je nyní propojit procesorové jádro s novou periferií. Sběrnice AXI se připojuje vždy „peer-to-peer“ port Master na port Slave. Jelikož máme jen jednu periferii, bylo by teoreticky možné propojit jádro a periferii „napřímo“, ovšem správné je použít speciální modul „AXI Interconnect“, který lze nakonfigurovat na vzájemné propojení několika Master a Slave portů najednou. Blok AXI Interconnect vložíme z knihovny rovněž pomocí příkazu Add IP.

Po propojení všech potřebných signálů by měl blokový diagram vypadat jako na obrázku 5. Opravdu poslední krok nutný pro dokončení procesorového systému je pak přiřazení bázové adresy všem AXI periferiím, které se v návrhu objeví. V našem případě bude v tabulce v nástroji „Address Editor“ jediná položka, kdy modulu „sdisp“ přiřadíme například výchozí adresu 0×43c0_0000.

Příště použijeme dnes ukončený projekt v nástroji Vivado pro založení softwarového projektu a přesuneme naši práci do vývojového prostředí Xilinx SDK. Ukážeme si, jak pro softwarový vývoj vygenerovat tzv. BSP knihovnu s inicializačním kódem a se základními ovladači k periferiím Zynq. Nad tímto BSP pak vystavíme aplikace, nejprve jen základní „Hello World“, kterou později upravíme na terminálovou aplikaci pro nastavování barvy šachovnicového vzoru na displeji.