Moderní řídicí a komunikační systémy vyžadují vyšší datové propustnosti a v obecném směru i vyšší formy zabezpečení a další služby. Typickým, ale ne jediným příkladem jsou kamerové systémy, kterým přenos dat v rychlosti 1 Gbit/s (protokol GigE) přestává stačit. Kamery s rozlišením kolem 5 M obrazových bodů se snímkovou frekvencí 30 Hz vyžadují datovou propustnost alespoň 1,5 Gbit/s. U systémů pořizujících obraz z hyperspektrálních nebo vysokorychlostních snímačů dosahují bitové rychlosti běžně kolem 5 Gbit/s a více.

Za tímto účelem byl na konci roku 2016 schválen standard IEEE 802.3bz, který umožní zařízením pracovat s přenosovou rychlostí 2,5 Gbit/s a 5 Gbit/s na standardních UTP rozvodech do vzdálenosti až 100 m. Díky této změně se stávají přenosy do rychlostí 5 Gbitů/s cenově dostupnější a umožňují využití i jiných metalických vedení než jen standardů USB 3.0 a 3.1 ve zpracování dat v oblasti výpočetní techniky.

Nespornou výhodou ethernetových spojení je relativně jednoduchá instalace kabeláže, velký dosah, možnost využívat standardní infrastrukturu (přepínače, síťové karty), dobrá odolnost vůči rušení a galvanické oddělení připojených jednotek s možností napájení po kabelu PoE. Nevýhodou je oproti USB vyšší cena a spotřeba energie při komunikaci na srovnatelných komunikačních rychlostech.

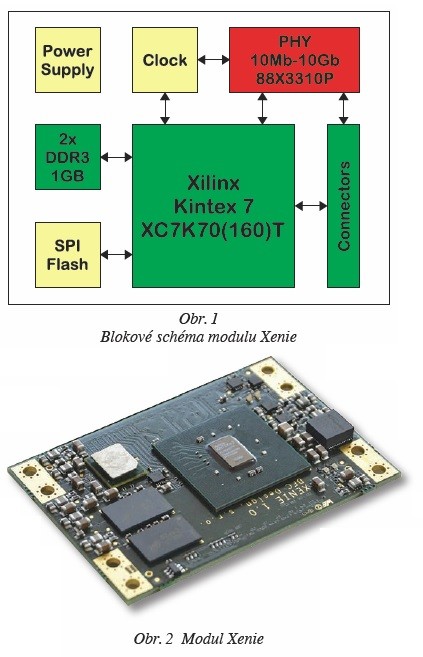

V průběhu roku 2016 byl společností DFC Design vyvinut univerzální jednodeskový FPGA modul Xenie pod licencí OHL (Open Hardware License) slučující výše uvedené funkce a doplněn o plnou podporu standardu 10GBASE-T pro přenos dat rychlostí 10 Gbit/s po metalickém vedení kategorie 6A. Modul pro svoji činnost vyžaduje minimum externích komponentů a jedno napájecí napětí o hodnotě 3,3 V. Ostatní napájecí napětí jsou generována modulem – jedná se celkem o 13 různých zdrojů napětí v rozsahu od 0,8 V do 2,5 V. Modul je osazen cenově dostupnou rodinou FPGA Kintex 7 od společnosti Xilinx. FPGA je voleno tak, aby disponovalo dostatečným počtem komunikačních linek (MGT). Dvě linky jsou využity on-board pro rozhraní RXAUI, které je přivedeno do PHY Marvell Alaska X 88X3310P. Zbývajících 6 linek je k volnému použití mimo modul (PCI Express, SDI, optické spoje, ethernet 10 Gbit, …).

Dosahované přenosové rychlosti se pohybují od 6,5 Gbit/s do 12,5 Gbit/s podle typu a varianty použitého FPGA.

PHY podporuje protokoly 10GBASE-T, 5GBASE-T, 2.5GBASE-T, 1000BASE-T, 100BASE-TX a 10BASE-Te je plně kompatibilní se standardy IEEE 802.3an, IEEE 802.3bz, specifikací NBASE- T™ a podporuje protokoly pro autentizaci a šifrování IEEE802.1ae MACsec. PHY podporuje protokol pro vkládání a dekódování časových značek PTP dle IEEE 1588 v2.

Modul je vybaven pamětí DDR3 o kapacitě 1 GB, která slouží pro ukládání dat a lze ji využít jako paměť programu pro procesor Microblaze. Konfigurace modulu je zajištěna sériovou pamětí Flash QSPI o velikosti 32 MB.

Vzhledem k tomu, že moduly jsou otevřenou platformou, existuje k nim několik zajímavých příkladů pro ověření funkcionalit v oblasti přenosu dat rozhraními 10GBASE-T včetně inicializace a komunikace s PHY, konverzí dat mezi 10GBASE-T a 10GBASE-SR/LR. Další skupinou jsou konverzní a testovací příklady pro příjem a vysílání videa ve formátu SDI. Samozřejmostí jsou schémata a desky plošných spojů v návrhovém systému Allegro.

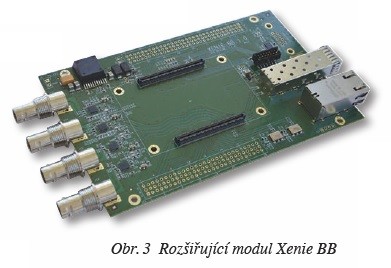

Pro testování a základní aplikace byla připravena vývojová deska obsahující konektory pro 10GBASE-T ethernet, 10GBASE-SR, 10GBASE-LR a SDI (Serial Digital Interface) do rychlosti 12 Gbit/s. Vývojový modul Xenie BB je doplněn dvěma oscilátory pro SDI rozhraní s obrazovou frekvencí 50 a 60Hz. V nejvyšší konfiguraci je schopen přijímat data ve dvou kanálech v rozlišení 4K a obdobně je vysílat rozhraním SDI, popřípadě konvertovat na 10Gbit ethernet a naopak. Vývojová deska je doplněna o rozšiřující konektory, na které je vyvedeno cca 130 obecných vstupů a výstupů.

Modul a jeho příslušenství je možné získat u společnosti DFC Design, a to včetně technické podpory, vývoje modifikovaných modulů nebo jejich osazovacích variant.