Abychom mohli naše pojednání zakončit, připravili jsme praktický příklad, na kterém budeme názorně demonstrovat vliv layoutu na dosahované vlastnosti napájecího zdroje. Pro tyto účely jsme vyrobili a následně otestovali dva napájecí zdroje, vycházející ze stejného schématu zapojení, jen s odlišnými layouty. Specifikaci napájecího zdroje, použitelného např. v rámci průmyslových aplikací, vidíme v tab. 2.

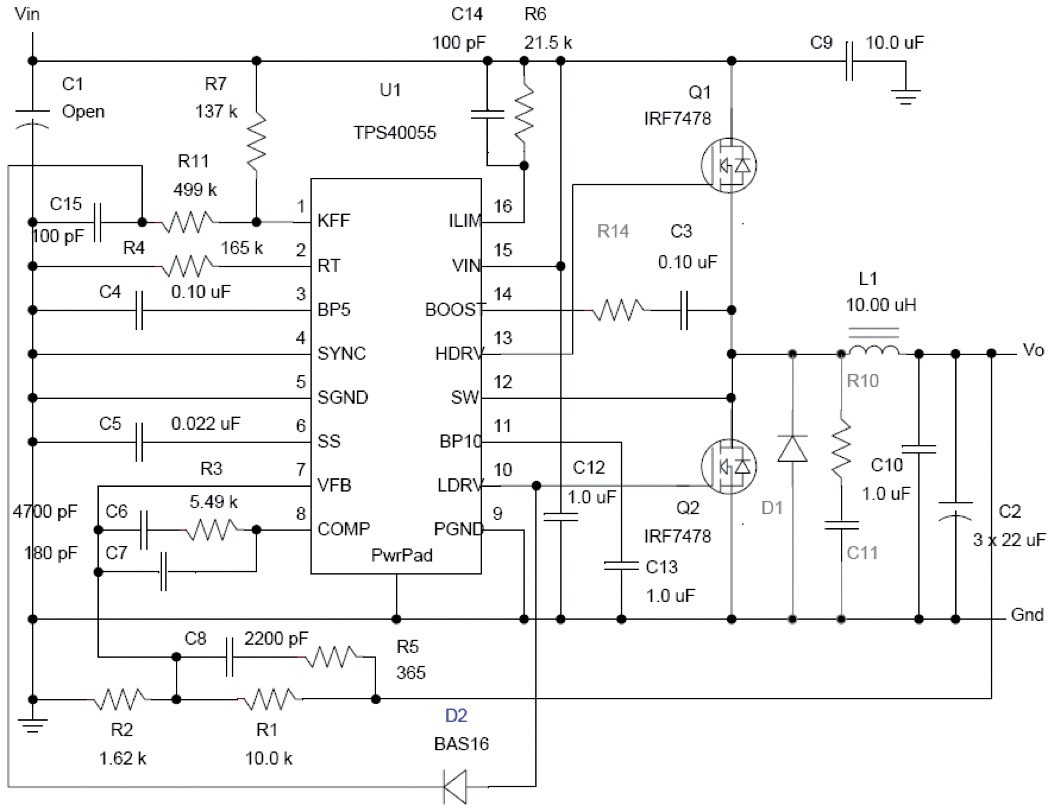

Na pozici regulačního integrovaného obvodu používáme struktury TPS40055 od Texas Instruments. Návrhový software, který lze stáhnout na stránkách výrobce, vygeneroval následující zapojení (MOSFETy včetně výstupní indukčnosti byly nahrazeny součástkami, které jsme právě měli k dispozici).

Obr. 13 Schéma zapojení, vygenerované návrhovým softwarem

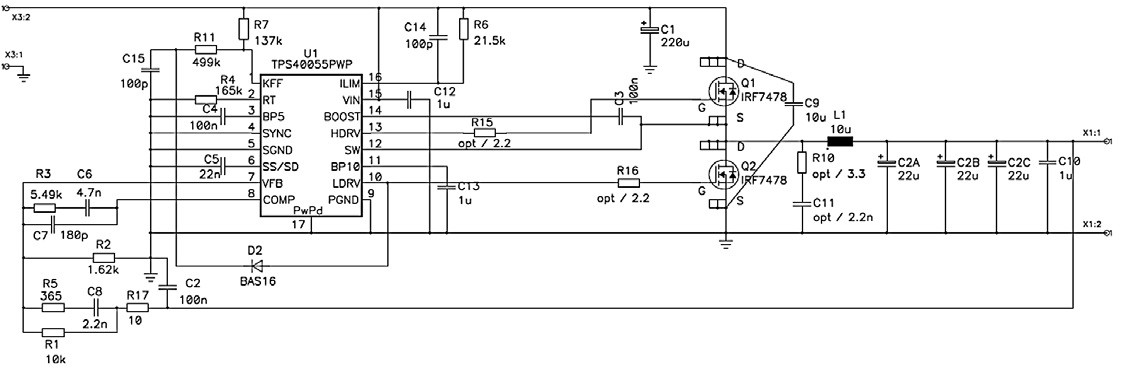

Obr. 14 Konečné schéma napájecího zdroje

.jpg)

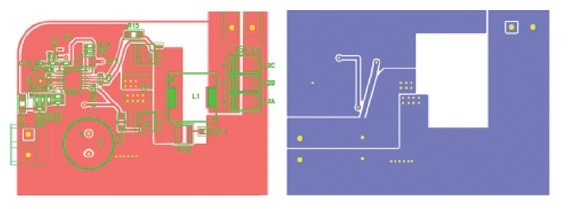

Obr. 15 Layout č. 1 (vlevo strana součástek, vpravo strana spojů)

.jpg)

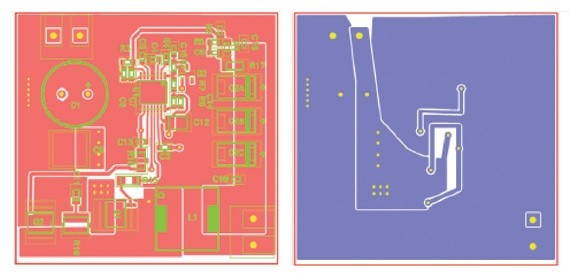

Obr. 16 Layout č. 2 (vlevo strana součástek, vpravo strana spojů)

Z původního schématu, generovaného vývojovým softwarem, jsme tak dostali následující řešení:

V porovnání s výchozím zapojením byl do konečného řešení zapracován rezistor 10 W, sloužící k připojení síťového analyzátoru na snímací linku výstupního napětí. Rovněž jsme v souvislosti s buzením hradla zapracovali volitelné rezistory nebo filtrační kondenzátor hned u děliče výstupního napětí. Návrh následujících dvou layoutů mohl začít.

Společné parametry měřené v obou zapojeních:

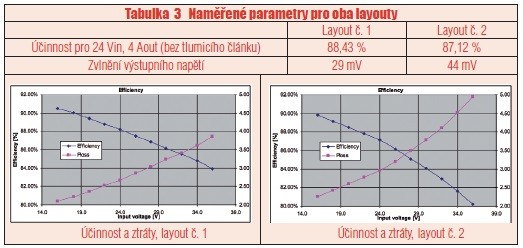

Nižší účinnost, naměřená v souvislosti s layoutem č. 2, byla způsobena ztrátami na vedení.

Ve všech měřeních figurovalo vstupní napětí 24 V (kromě obr. 17, kde bylo Vin rovno 36 V) a jmenovité zatížení 4 A.

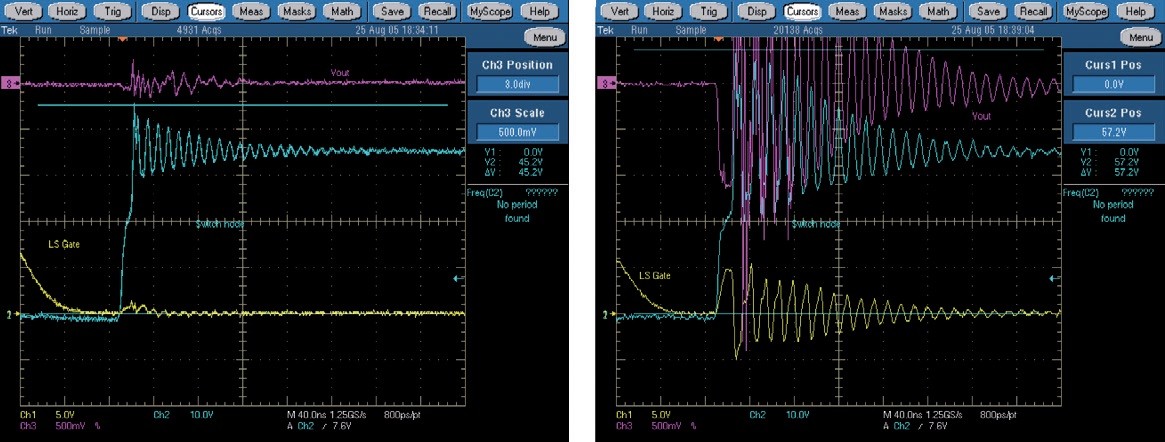

Obr. 17 Vout, spínaný uzel a napětí GS na spodním MOSFETu pro Vin=36 V, bez tlumicího článku a také bez rezistorů v obvodu hradla

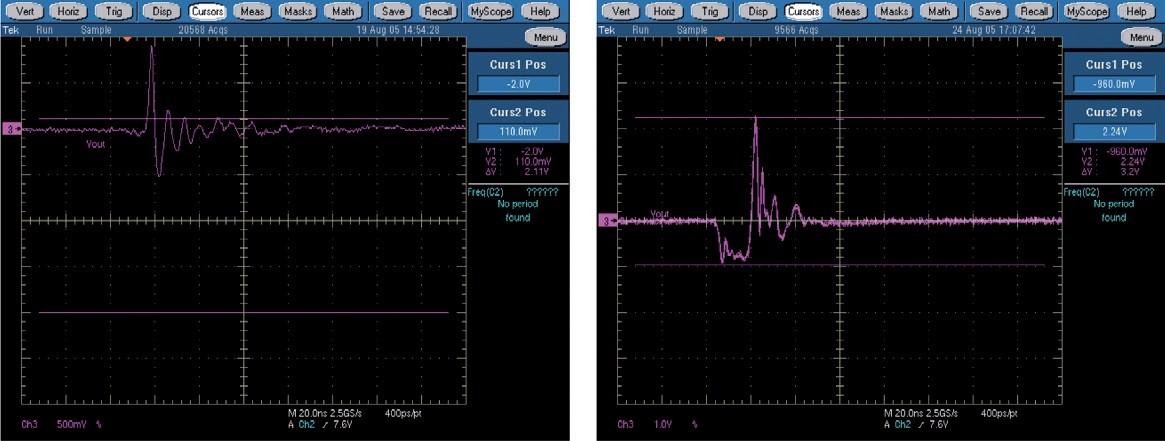

Obr. 18 Vout, spínaný uzel a napětí GS na spodním MOSFETu bez tlumicího článku a s rezistory v obvodu hradla. Různá vertikální měřítka pro Vout.

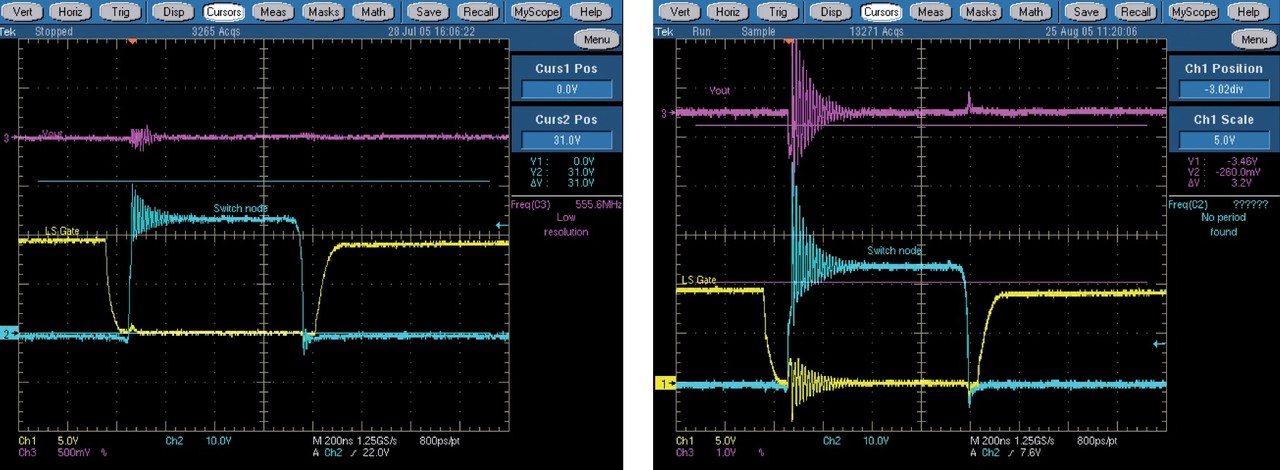

Obr. 19 Vout, spínaný uzel a napětí GS na spodním MOSFETu s tlumicím článkem a také s rezistory v obvodu hradla

Obr. 20 Vout, spínaný uzel a napětí GS na spodním MOSFETu s tlumicím článkem a bez rezistorů v obvodu hradla

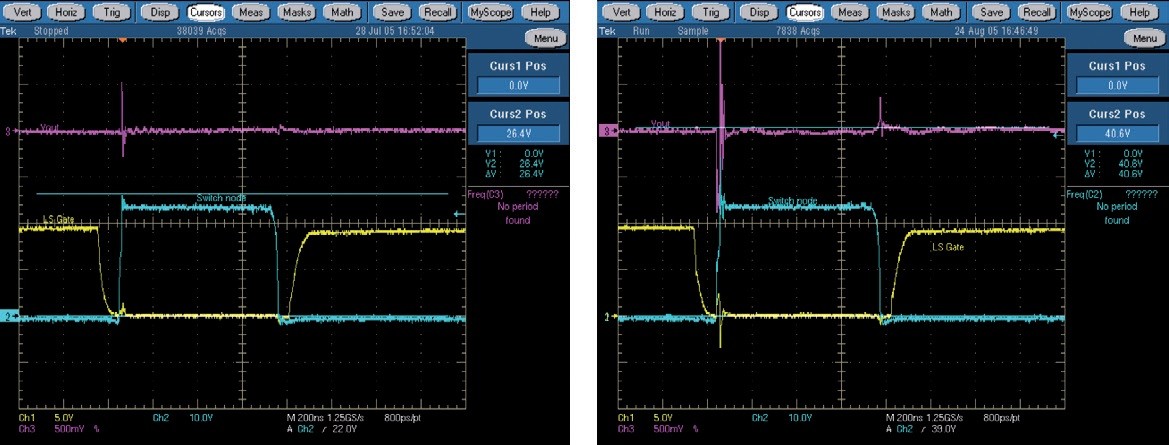

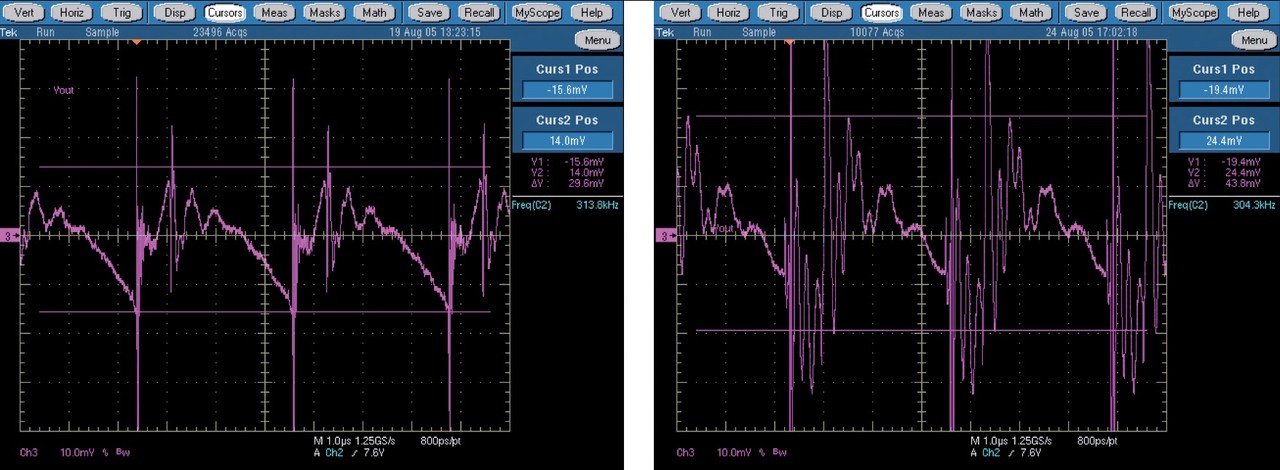

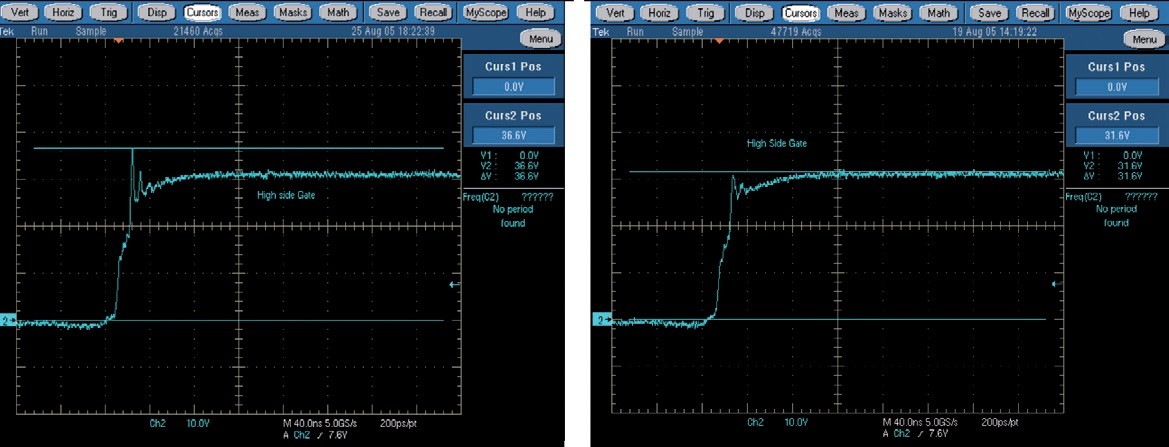

Porovnání naměřených výsledků dvou napájecích zdrojů s různými layouty zdůrazňuje význam správného layoutu. Napájecí zdroj s layoutem č. 1 vykazuje mnohem méně překmitů a také výrazně nižší zvlnění výstupního napětí. Napájecí zdroj č. 2 by zase neměl při vstupním napájecím napětí 36 V pracovat bez tlumicího článku. Integrovaný regulátor ve skutečnosti selhal jen několik vteřin poté, co jsme zachytili průběhy na obr. 17. Důvodem byl obrovský překmit o velikosti více než 57 V, vyskytující se na spínaném uzlu (pin 12). Maximální předepsané napětí 45 V tak bylo na tomto pinu překročeno o 12 V. Za překmity mohou dlouhé budicí trasy v obvodu hradla horního MOSFETu. Na obr. 21 a 22 vidíme výstupní napětí. Obr. 21 přitom znázorňuje výstupní napěťové špičky během spínání high side FETu. Jasně zde můžeme vidět, že výstupní napěťová špička layoutu č. 2 výrazně překročí dvojnásobek velikosti v případě prvního layoutu. Obr. 22 následně zachycuje záznam zvlněného výstupního napětí. Jak jsme již ostatně mohli očekávat, zvlnění způsobené layoutem č. 2 bylo výrazně větší než zvlnění produkované layoutem č. 1. Může za to umístění výstupních kondenzátorů s ohledem na proudovou trasu směřující k zátěži. V případě layoutu č. 1 budou kondenzátory mnohem více ve shodě s proudovou trasou směřující k zátěži, což ovšem nebude platit u layoutu č. 2. V prvním případě nemá proud tekoucí do zátěže žádnou možnost volby a musí, dříve než dosáhne své zátěže, vést přes výstupní kondenzátory. Layout č. 2 však nevynucuje průchod proudu přes výstupní kapacity a my tak dostáváme větší zvlnění výstupního napětí. Obecně vzato, výstupní kondenzátory by měly být rozmístěny takovým způsobem, aby proud tekoucí do zátěže neměl žádnou jinou možnost volby než tu správnou – přes kapacity.

Obr. 21 Vout s tlumicím článkem a bez rezistorů v obvodu hradla. Různé vertikalní rozlišení!

Obr. 22 Zvlnění výstupního napětí s tlumicím článkem a rezistory v obvodu hradla

.jpg)

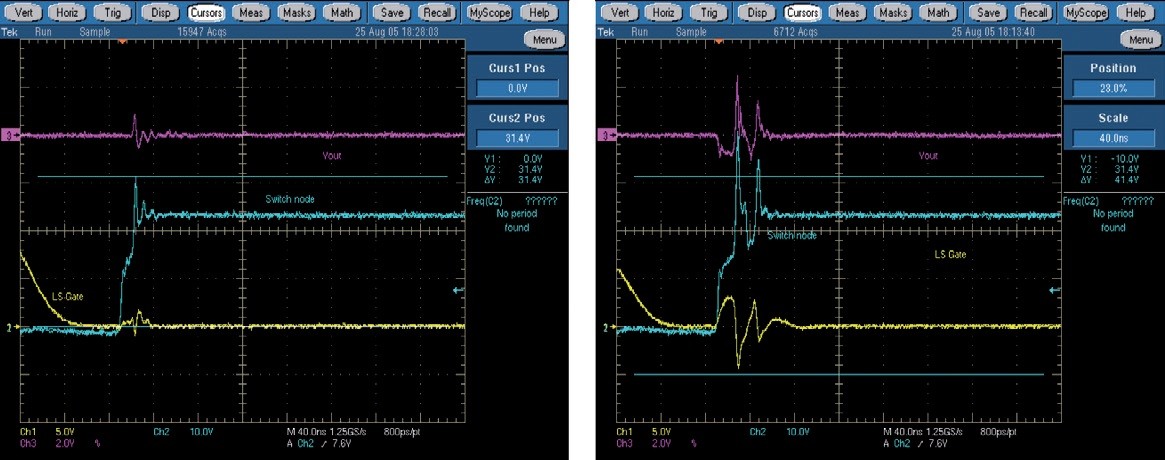

Obr. 23 Vliv rezistoru v obvodu hradla na překmity (měřeno na layoutu č. 1)

Na obr. 23 sledujeme vliv rezistoru v obvodu hradla na překmity. Jasně zde vidíme, jakým způsobem rezistor v obvodu hradla snižuje dI/dt, což má za následek méně energie pro rezonanční obvod, složený z trasy a její indukčnosti spolu s kapacitou hradla připojeného MOSFETu. Takový postup se pak zákonitě odrazí v podobě menších překmitů.

Názorně jsme si ukázali zásadní vliv layoutu na dosahované vlastnosti napájecího zdroje. Je proto důležité navrhnout layout s minimem parazitních indukčností a také odporů. Potřebujeme omezit plochu smyček a důsledně oddělit výkonový stupeň napájecího zdroje od toho řídicího. Pohrdání těmito pravidly pak bude znamenat horší technické parametry včetně menší spolehlivosti samotného zdroje. Naměřené výsledky, zachycené na konci článku, takový závěr zcela jasně potvrzují.

Autor by rád poděkoval Renate Flesch, která nakreslila všechny layouty, schémata a rovněž připravila a odměřila vše potřebné. Bez její spolupráce by tento článek nemohl vzniknout.

[1] Robert Kollman, “Constructing Your Power Supply – Layout Considerations”, Texas Instruments Power Supply Design Seminar SEM1600, Topic 4, TI Literature number SLUP224

http://www.s.ti.com/sc/ techlit/slup230.pdf

[2] Bill Andreycak, Bob Mammano, “Practical Considerations in Troubleshooting and Optimizing Power Supply Control Circuits and PCB”, Texas Instruments Online Seminar

http://training.ti.com/courses/coursedescription. asp?iCSID=1150

[3] Prof. Dr. T. Wolf, „Schaltungstechnik“ Vorlesungsskript der Fachhochschule Landshut

http://www.fh-landshut. de/~wlf/schT/Vorlesung/ST_1.pdf

[4] Phil Rogers, “Board layout boosts power-supply performance”, Seite 175–178, EDN Magazine November 5, 1998

http://www.edn.com/archives/ 1998/110598/pdfs/23ms435.pdf

[5] Marcus Zimnik, „Vést či nevést: otázka layoutu – část 1 – teorie“, DPS Plošné spoje od A do Z, číslo 2 2010, str. 16 – 17

[6] Marcus Zimnik, „Vést či nevést: část 2 – Pokyny pro správný návrh layoutu“, DPS Plošné spoje od A do Z, číslo 1 2011, str. 4 – 7