Každý návrh systému sběru dat vykazuje mnoho společných rysů a také postupů, které se znovu a stále dokola opakují. Práce jako na běžícím pásu to sice není, ale chyby se dělají i tady. Aby jich bylo co nejméně a dílo šlo hezky od ruky, nebudeme trhat partu. Zvláště, když celou sestavu vyberou ti nejpovolanější.

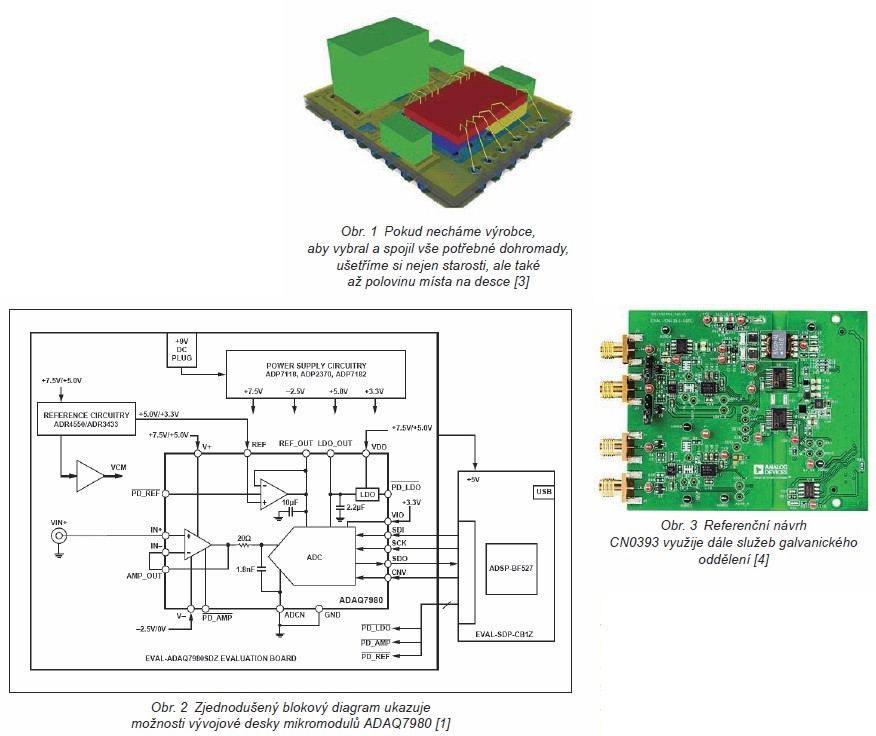

Pokud se ve společnosti Analog Devices řeknou mikromoduly (μModule®) ADAQ7980 [1] nebo ADAQ7988 [2], rozumí se tím relativně nové a stejně tak i do nových návrhů doporučované 16bitové systémy sběru dat, které v základním náhledu 3D modelu z obr. 1 od sebe odlišíme propustností 1 MSPS (ADAQ7980), resp. jen 500 kSPS. Tomu pak také odpovídá typická ztráta při maximálním výkonu 21 mW nebo 16,5 mW. Jediné SiP (System in Package) tak může hostit čtyři naprosto běžné stavební kameny drtivé většiny návrhů tohoto druhu spolu se stěžejními pasivními součástkami okolo, které dostaly za úkol ulehčit vývoj signálového řetězce s A/D převodníky typu SAR (Successive Approximation Register). Možná to tak nevypadá, ale o dosažení parametrů stanovených v dokumentaci zvenčí rozhoduje i ta nejmenší pasivní „záležitost“.

Vnitřní zapojení pozorujeme na obr. 2, který výslednou kombinaci aktivních i pasivních součástí zasazuje přímo do vývojové desky EVAL-ADAQ7980SDZ. V malém pouzdru typu LGA s 24 vývody a rozměry 5 × 4 mm bude dostatek místa jak pro precizní, nízkopříkonový 16bitový A/D převodník s postupnou aproximací, jeho širokopásmový budič s vysokou vstupní impedancí a oddělovací zesilovač pro napěťovou referenci, tzv. buffer, tak ze čtvrté pozice rovněž účinně pracující blok řízení napájení – ve zkratce tedy LDO. Očividně se tak vyhýbáme hned několika kritickým místům v návrhu a stále přitom dokážeme svobodně řídit dění, např. s přístupnou smyčkou zpětné vazby budiče ADC (zisk, souhlasná nastavení) nebo několika vývody pro napájení, kdy se s minimálním dopadem na výsledné charakteristiky pouštíme třeba i do jednoduchého zdroje oproti zemi. Odpovědnost za volbu, optimalizaci a třeba i layout v zásadě ponecháme na výrobci, který se dokáže odvděčit kupříkladu širokým provozním rozsahem od –55 °C až do +125 °C. Kdo by nechtěl zvýšit hustotu kanálů, zvláště když vlastní převodník může mít každý z nich?

Když v Analogu nové subsystémy vyvíjeli, položili si otázku: v čem přesně vývojáři nejčastěji chybují? A pro případ ADC typu SAR se dobrali ke dvěma oblastem – vlastnímu analogovému a také napěťové referenci vyhrazenému vstupu [3]. Špatně prý volíme budiče, šířku pásma filtru a třeba i materiál dielektrika u kondenzátoru.

U reference zase dokáže pozlobit layout, nedostatečná zatížitelnost zdroje, šum a také velikost kapacity. Kondenzátor 10 μF proto máme pevně daný a navíc v naprosté blízkosti převodníku. A pokud jde o reference, těch si nyní dle svého výběru klidně osadíme ještě více.

[1] Obvody ADAQ7980, http://www.analog.com/en/products/analog-to-digitalconverters/standard-adc/precision-adc-20msps/single-channel-ad-converters/ADAQ7980.html

[2] Obvody ADAQ7988, http://www.analog.com/en/products/analog-to-digitalconverters/standard-adc/precision-adc-20msps/single-channel-ad-converters/ADAQ7988.html

[3] Improving Precision Data Acquisition Signal Chain Density Using SiP Technology, http://www.analog.com/en/analog-dialogue/articles/improvingprecision-data-acquisition-signal-chaindensity-using-sip-technology.html

[4] Referenční návrh CN0393, http://www.analog.com/en/design-center/referencedesigns/hardware-reference-design/circuits-from-the-lab/CN0393.html