Manu Venkategowda, aplikační inženýr z firmy Microchip Technology Inc., vysvětluje, jak může konfigurovatelná logická buňka v rámci mikrokontroléru zjednodušit implementaci složitějších funkcí.

V některých případech mohou velký užitek přinášet i docela jednoduché věci. Většina vývojářů pracujících na vestavných systémech se kupříkladu neobejde bez různých druhů signálů či logických obvodů, se kterými pak řeší požadavky koncové aplikace. Zároveň se přitom uchylují k návrhu komplikovaných logických struktur přímo na desce plošného spoje. Co když ale něco složitějšího dokážeme navrhnout jednoduchým způsobem? Některé mikrokontroléry totiž nabídnou flexibilní periférie, s nimiž vyřešíme i funkce potřebné v náročnějších aplikacích.

A to je přesně prostor pro konfigurovatelné logické buňky CLC (Configurable Logic Cell). Prvky CLC rozšířily sadu periférií mikrokontrolérů (MCU) PIC® od společnosti Microchip a umožňují tak navrhnout jednoduchou funkci přímo ve vztahu k MCU. Periférie CLC nechají definici signálů a jejich kombinací coby vstupů logické funkce přímo na vývojáři. Z výstupu logického obvodu pak řídíme další periférie nebo i vstupně-výstupní piny a flexibilně přitom reagujeme na požadavky konkrétních funkcí.

Aby vše zůstalo jednoduché, budou buňky CLC podporovány ze strany MCC (MPLAB® Code Configurator) od Microchipu. Vývojáři tak mohou myší snadno přetáhnout logická hradla s cílem propojit v prostředí GUI vstupy i výstupy, generovat kliknutím na tlačítko kód (C) a výrazně si přitom zjednodušit implementaci modulů CLC.

Periférie CIP nezávislé na jádru (Core Independent Peripherals) své úlohy zpracovávají bez potřeby jakéhokoli dalšího kódu či dohledu ze strany CPU, jen aby byla zachována jejich činnost. Jedním z příkladů periférií CIP se stávají právě buňky CLC. Zjednodušíme s nimi realizaci složitých řídicích systémů, vývojářům zároveň zajistíme tolik potřebnou flexibilitu a ještě přitom odlehčíme jednotce CPU, takže bude možné pozvednout výkon celého mikrokontroléru. Pokračujte dál a dozvíte se, jak lze v dané aplikaci využít buňky CLC k detekci fáze signálu, výrobě doplňkových průběhů či sledování většího počtu parametrů. Díky celé řadě vstupů, způsobů spouštění a také výstupů dostáváme s buňkami CLC prakticky neomezené možnosti.

Pod pojmem CLC rozumíme uživatelsky konfigurovatelnou periférii podobnou PLD (Programmable Logic Device), nicméně integrovanou přímo do mikrokontroléru. Na pozici vstupů buňky CLC můžeme volit vnitřní a také vnější vstupy. CLC přitom počítá se vstupy z dalších periférií nebo i vstupního pinu. Následně dochází k vykonávání zamýšlené logické operace spolu s výstupem, který lze využít k řízení dalších periférií či jiného vstupně- výstupního vývodu.

Buňka CLC zpracuje signály na způsob interního taktu, výstupu jiné periférie nebo související události (vstup časovače). Zvolené vstupní signály lze k požadované logické funkci nasměrovat prostřednictvím stupně zajišťujícího hradlování, přičemž buňka CLC podpoří různé operace, jako jsou např. AND, OR, NOT, XOR, NAND, NOR nebo XNOR. Výstupy stupně pro hradlování dat budou v rámci CLC zároveň vstupy bloku výběru logické funkce. V poslední fázi pak ještě dochází k volbě požadované polarity výstupu buňky CLC.

Při realizaci sekvenčních obvodů a také kombinačních logických funkcí lze buňky CLC využívat jako samostatné periférie a zjednodušit přitom rychlé spouštění událostí a také příslušné odezvy. Stejně tak je bude možné provozovat ve spojení s ostatními perifériemi, kdy rozšiřují jejich pole působnosti, takže ve výsledku řešíme i složitější funkce jednoduchou hardwarovou cestou.

Protože máme co do činění s perifériemi nezávislými na jádru, buňky CLC v podstatě snižují požadavky aplikace kladené na šířku pásma CPU. Řadu reakcí na jednoduché logické události totiž místo CPU zpracují periférie. Zároveň přitom zjednodušíme požadavky související s pamětí typu Flash či RAM, protože se již obejdeme bez softwarových algoritmů. Logické funkce řešené hardwarově budou mít kromě toho ve srovnání se stejnými operacemi prováděnými softwarově rychlejší výsledky. A co víc, buňky CLC bez účasti jakýchkoli vnějších součástek podpoří vyšší úroveň integrace, což se příznivě projeví též na výsledné velikosti desky plošného spoje.

Univerzálním řešením a také jednoduchostí buněk CLC rozšiřujeme možnosti mikrokontrolérů PIC. Ukažme si to názorně na příkladu detektoru posunu (fáze), který bude užitečný v celé řadě aplikací, a to včetně měření vzdálenosti. Systém pracuje na principu vf vlny vysílané směrem k cíli, kdy vzdálenost od překážky zůstává úměrná fázovému posunu mezi vysílaným a odraženým signálem. Ke stanovení fázového rozdílu mezi dvěma signály stejného kmitočtu poslouží právě buňka CLC. Vstupy zde přitom tvoří vysílané a přijímané průběhy, zatímco fázový rozdíl mezi těmito dvěma signály na výstupu buňky CLC umožňuje vypočítat vzdálenost mezi zdrojem a příslušným cílem.

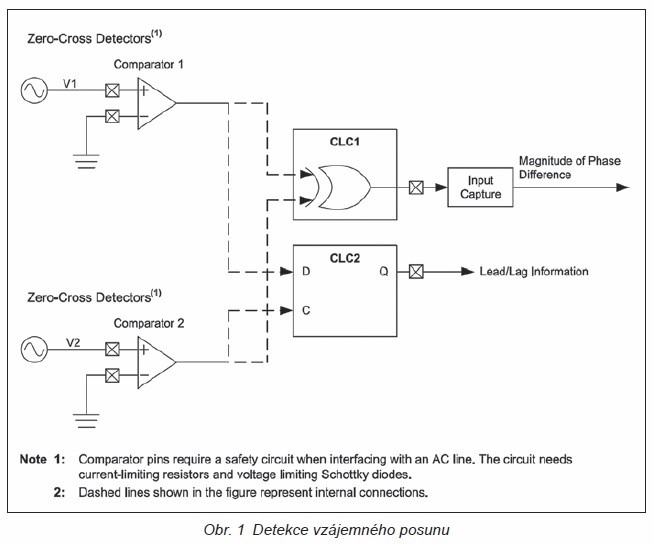

V návrhu detektoru s využitím buňky CLC bude logická funkce AND-OR použita k realizaci možností XOR pro měření velikosti fázového rozdílu, zatímco klopný obvod typu D (D-FF) pomůže vytěžit informaci o předstihu či zpoždění signálu (tj. Lead/Lag). Kromě obdélníkového průběhu lze posun stanovit rovněž mezi dalšími typy analogových signálů, třeba sinusovými. Konkrétní řešení detektoru s buňkami CLC zachycuje obr. 1.

Zdrojové signály, jejichž fázový posun zkoumáme, přivádíme na vstupy dvou komparátorů konfigurovaných jako detektory průchodu nulou ZCD. Detektory ZCD pak převádí vstupní analogové signály na obdélníkové průběhy o stejném kmitočtu. Pokud však na pozici zdrojového signálu uvažujeme rovnou obdélník, můžeme detektory ZCD vypustit. Obdélníkové průběhy poté interně vedeme na vstupy několika modulů CLC.

Ke stanovení velikosti fázového rozdílu nám tedy poslouží první buňka CLC spolu s blokem IC (Input Capture). CLC1 staví na logické funkci AND-OR, ze které odvozujeme schopnosti XOR. Takto vznikající výstup CLC1 externě přivádíme jako zdrojový signál pro IC. Šířka pulzu „XORovaného“ výstupu představuje velikost fázového rozdílu mezi dvěma signály a měřena bude prostřednictvím bloku IC. Pokud tedy buňka CLC1 nemá na svém výstupu žádný signál, budou zdrojové průběhy ve fázi.

Abychom dokázali podchytit předstih nebo také zpoždění dvou vstupních průběhů, nakonfigurujeme další CLC v režimu klopného obvodu D-FF s jedním obdélníkovým signálem provázaným se vstupem D a zbývajícím pak pro hodiny. Na základě vysoké nebo také nízké úrovně výstupu CLC2 konečně určíme, zda vstup D s ohledem na hodinový vstup vede nebo zůstává pozadu. Takové operace se dvěma signály stejného kmitočtu budou žádané v celé řadě aplikací, např. v měřidlech, systémech číslicově řešeného napájení, ve sdělovací technice a také přístrojích používaných v medicíně.

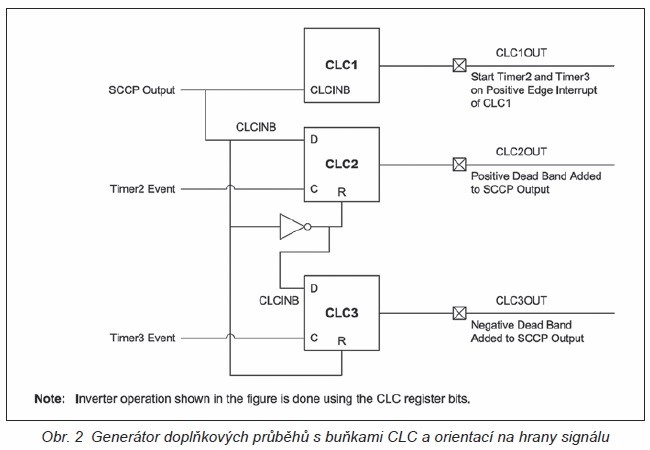

Další možnosti nasazení buněk CLC nabídnou generátory CWG (Complementary Waveform Generator). CWG zde na základě svého vstupu vyrábí doplňkové průběhy společně s řízením prodlevy. Časový úsek označovaný jako „dead band“ bude v nejrůznějších návrzích zdrojů napájení vkládán mezi dvojici signálů s cílem zamezit proudovým nárazům. Taková aplikace v kontextu CLC názorně ukazuje využití možností detekce hrany a také přerušení při generování doplňkových signálů společně s modulem SCCP (single capture/compare/ PWM) na pozici vstupního zdroje.

Za účelem ovládání svého chodu budou aplikace, jako je např. řízení motorů, často vyžadovat hned několik generátorů doplňkových signálů. Modul MCCP (multiple capture/compare/PWM) sice může na základě řízení prodlevy svého výstupu zajistit takové průběhy se vzájemně se nepřekrývajícími signály, nicméně bude-li aplikace vyžadovat větší počet modulů MCCP, než může konkrétní součástka nabídnout, využijeme právě SCCP v kombinaci s buňkami CLC.

Periférie CLC lze tedy ve spojení s moduly SCCP použít k výrobě doplňkových signálů s požadovanou prodlevou (dead band), zvláště když SCCP samy o sobě vzájemně se nepřekrývající signály generovat nemohou. Zpoždění budeme uvažovat jak pro výstupy SCCP vztažené k hraně, tak též provázané se středem. Na obr. 2 vidíme zapojení buněk CLC1, CLC2 a také CLC3 za účelem řízení prodlevy výstupu modulu SCCP, kdy vstupují do hry právě hrany signálu.

Zapojení budiče motoru s plným můstkem můžeme kupříkladu ovládat a využívat přitom periférie MCCP s výstupem zajišťujícím doplňkové signály. Pokud však budeme muset spravovat hned několik takových budičů a počet periférií MCCP dostupných pro danou součástku již nebude postačovat, využijeme opět modulu SCCP spolu s buňkami CLC.

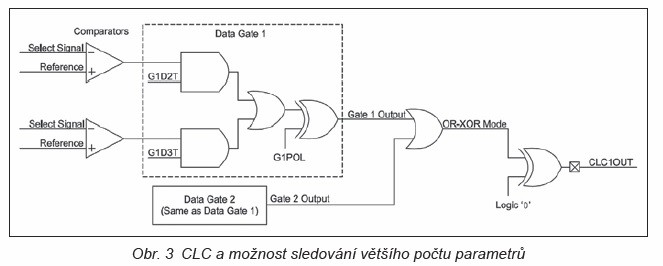

Naše aplikace mnohdy vyžadují souběžné monitorování různých parametrů, např. teploty, tlaku či vlhkosti. Začnou-li pak takové proměnné překračovat vysoké nebo zase nízké prahové úrovně, může být pro odvrácení katastrofického scénáře nutné provést určitou akci.

Na pozici vstupů buněk CLC máme k dispozici několik komparátorů. V mikrokontroléru lze sice komparátor využít pouze ke sledování jednoho parametru, nicméně výstupy většího počtu komparátorů dokážeme slučovat, využívat přitom buněk CLC a monitorovat tak i více proměnných. Potřebnou akci pak bude možné spustit, pokud kterákoli nebo snad i všechny sledované veličiny překročí určitý limit. Způsob zapojení CLC za účelem dozorování dvou různých parametrů zachycuje obr. 3.

V praxi vše využijeme třeba při sledování teploty a tlaku v průmyslových provozech, kde po překročení přednastavené hodnoty kteréhokoli z parametrů odstavíme příslušnou část. Stejně tak bude možné vyhodnocovat napěťové úrovně v zálohovaných zdrojích napájení.

Zapracování konfigurovatelných logických buněk do souboru periférií umožňuje uživateli snadno řešit logické návrhy přímo v rámci mikrokontrolérů PIC. Slučováním výstupů různých periférií rozšiřujeme možnosti stávajících struktur a také předpoklady pro realizaci nových aplikací. Vzhledem k tomu, že logické funkce řešené hardwarově budou mít rychlejší odezvu než stejné operace prováděné softwarovou cestou, pomáhají nám buňky CLC s navýšením rychlosti celého systému. Zároveň tak poskytují vyšší úroveň integrace bez potřeby vnějších logických hradel zajišťujících nezbytné funkce, takže omezíme nejen počet nutných součástek, ale také celkové rozměry desky plošného spoje. Buňky CLC se nebrání ani slučování nejrůznějších vstupních zdrojů signálu za přispění různých typů logických hradel, s nimiž bude možné vyrábět zcela odlišné průběhy. Veškeré zmiňované flexibilní vstupy a výstupy nebo i logické funkce lze kromě toho jednoduše zapracovat s přispěním nástroje založeného na GUI a nazvaného MPLAB® Code Configurator (MCC), který pro vaši aplikaci vygeneruje snadno čitelný kód (C).

[1] Aplikační poznámka Extending PIC MCU Capabilities Using CLC, http://ww1.microchip.com/downloads/en/AppNotes/00002133a.pdf