V polovině června 2010 proběhl v hotelu Annahof u Brna seminář, jehož cílem bylo seznámit účastníky se specifickými postupy při návrhu FPGA. Na programu byla prezentace verifikačních postupů s využitím „assertions“ (Assertion-BasedVerification), přehled základních informací o SystemVeriloga PSL pro tvorbu projektů se simulátorem ModelSim a také předvedení programu I/O Designer pro optimalizaci návrhu desky s obvody FPGA. Seminář byl pořádán společně firmami CADware s. r. o., ASICentrum s. r. o. a Mentor Graphics.

Neil Rattray (Mentor Graphics) nastínil možnost řešení návrhu FPGA pomocí programu ModelSim Deluxe Edition, který je dnes v podstatě průmyslovým standardem mezi simulátory HDL. Spolu s Jakubem Šťastným (ASICentrum s. r. o.) pak výborným způsobem prezentovali význam verifikace návrhu založeného na „assertions”.

Zde je stručné shrnutí jejich příspěvků: S rostoucí komplexitou návrhu číslicových systémů a zejména s koncepcí „systém on chip“ roste také náročnost verifikace a fáze „ladění“ vlastního číslicového návrhu, která tak zabírá stále větší část celkové délky projektu. Jednou z příčin tohoto trendu je běžný postup při verifikaci: chyba v návrhu je identifikována na základě detekce chybného chování na rozhraní obvodu s vnějším světem, což dále vyžaduje zdlouhavé hledání příčiny a „trasování“ problému do vnitřních bloků číslicového systému. Verifikace s využitím „assertions“ tento problém částečně řeší a umožňuje snížit čas potřebný pro ladění simulací až na polovinu, a to zejména z důvodu lepší pozorovatelnosti signálů. „Assertions“ mají dvě hlavní funkce: jednak sledují funkci kódu a zajišťují, aby byl důkladně otestován (funkční pokrytí – Functional Coverage) a zároveň sledují vnitřní integritu simulovaného systému a identifikují a informují o nežádoucím chování monitorované části obvodu v blízkosti zdroje problému.

Steve Gascoigne (Mentor Graphics) svým příspěvkem na téma „Integrace návrhu FPGA s návrhem desky“ představil program I/O Designer. Implementace pouzder BGAse stovkami pinů na desce s plošnými spoji bývá často vnímána jako bolestivý a časově náročný proces. Program I/O Designer nabízí metodiku i nástroje pro souběžný a obousměrný návrh a úpravu dat mezi návrhovými prostředky pro obvody FPGA a moduly pro tvorbu schémata topologie plošného spoje. Šetří tak čas a eliminuje chyby při ruční práci.

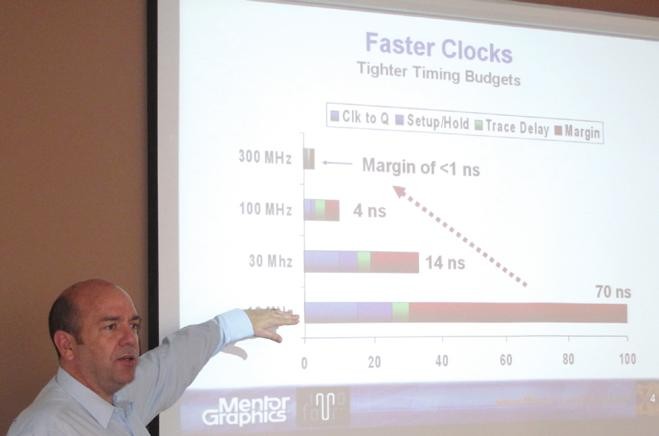

Začátkem září 2010 proběhl v hotelu Akademie – Naháč další seminář, který se týkal návrhu desky se součástkami DDRx. Seminář byl opět pořádán firmou CADware s. r. o. ve spolupráci s firmou Mentor Graphics. Přednášejícím byl Steve Gascoigne, expert firmy Mentor Graphics na Signal Integrity analýzy. Cílem semináře bylo seznámit účastníky s analýzou přenosu signálu plošnými spoji již při návrhu zapojení s DDRx, protože je nezbytná pro zajištění správné funkce obvodů. Analýzy a potřebné postupy byly prakticky ukázány na programu HyperLynx LineSim a BoardSim od firmy Mentor Graphics. Všechny prezentace z obou seminářů jsou dostupné u firmy CADware na vyžádání.