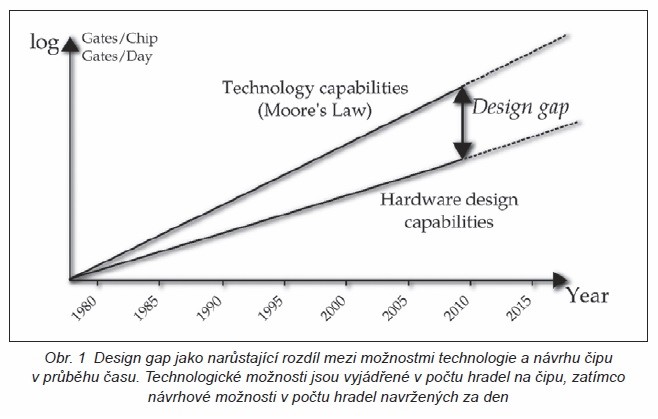

Mnohdy nemáme vhodné české výrazy pro vžité anglické, takže je lepší je ani nepřekládat. To se týká i tématu tohoto článku, kde pojem „design gap“ představuje vzrůstající rozdíl mezi možnostmi v technologii výroby a návrhu čipu. Nejedná se o nový výraz − byl použit v souvislosti s návrhem čipů již kolem roku 2000 a diskutován zejména v souvislosti s uvedením 90nm technologie [1] – již tenkrát bylo možné vyrobit čipy se 100 miliony hradel, ale žádné takové nebyly realizovány, protože nemohly být navrženy. Design gap byl několikrát zmíněn i na letošní konferenci DAC (Design Automation Conference) [2] konané v San Franciscu, a tak jistě nebude na škodu připomenout si, o co se jedná.

Problém by se dal zjednodušeně popsat asi takto: vyrobit čipy se stále větším počtem tranzistorů není tak náročné, jako je navrhnout. Vývojář má sice k dispozici miliony volných tranzistorů, nemá ale možnost je efektivně využít. Už před lety se za hlavní příčinu pokládaly chybějící nástroje používané k návrhu čipů a návrhové možnosti. To byla situace kolem roku 2000, ale ani dnes to není lepší – svědčí o tom výroky na již zmíněné konferenci DAC:

Jak je vidět, situace se opakuje a opět to je hlavně návrhový software, který nestačí držet krok. Jedno z doporučení říká: „EDA software potřebuje výrazný pokrok každých 10 až 12 let, aby mohl držet krok s vývojem výroby“. Panuje všeobecná shoda, že je čas na další větší změnu v EDA prostředí pro návrh čipů.

Dost možná je současný design gap jiné povahy, než byl před lety. Návrhy jsou velmi komplexní a zdá se, že problém může být způsoben i nepředvídatelným chováním návrhu, kdy i malá změna ve vstupních parametrech způsobí velkou změnu v ploše čipu. Jako příklad je uváděno zvýšení frekvence o 10 MHz v rámci 1GHz návrhu jistého čipu, které vedlo k nárůstu plochy o 6 %.

Problém s design gap trápí i americkou vládní agenturu DARPA (Defense Advanced Research Projects Agency), protože pomalé návrhy zdržují její projekty pro vojenské účely [3]. Navrhuje proto řešení v podobě využití umělé inteligence (deep learning a data mining) a spolupráce více společností. To by nabízelo efektivnější modely, které se přizpůsobí realitě rychleji. O využití umělé inteligence v EDA softwaru a návrhu se také mluvilo na DAC konferenci jako o možném řešení některých, zejména časově náročných úloh [4], ale je zřejmé, že se jedná o běh na dlouhou trať.

Již dříve se objevily snahy design gap objasnit. V práci „Confirming the Design Gap“ [5] se zkoumají struktury čipu a jejich vliv na design gap. Dochází se k závěru, že design negativně ovlivňují nepravidelné struktury, které nelze jednoduše kopírovat a opakovat. Tak například paměti sestávají z bloků, které lze kopírovat a tím výrazně snížit dobu potřebnou k návrhu. Na druhé straně procesory obsahují většinou různorodé bloky, které nelze kopírovat.

Zajímavé je, že Gordon Moore, který předpověděl neustálé zvyšování počtu tranzistorů na čipu v průběhu doby, si byl zřejmě vědom možného problému s návrhem čipu. Zmínil se o tom v článku v časopisu Electronics z roku 1965, v odstavci nazvaném „Day of reckoning“ (Den zúčtování), kde připustil zvyšující se tlak na vlastní návrh čipu.

[1] www.techdesignforums.com/blog/2018/06/27/dac-design-gapautomation/

[2] www.dac.com

[4] www.techdesignforums.com/blog/2018/06/26/dac-eda-machinelearning/

[5] www.uni-ulm.de/fileadmin/website_uni_ulm/iui.inst.050/publications/MenhornS2013_2.pdf