Cílem tohoto článku je přiblížit čtenáři vysokorychlostní rozhraní LVPECL, upozornit na jeho vlastnosti a možná úskalí při jeho použití v praxi.

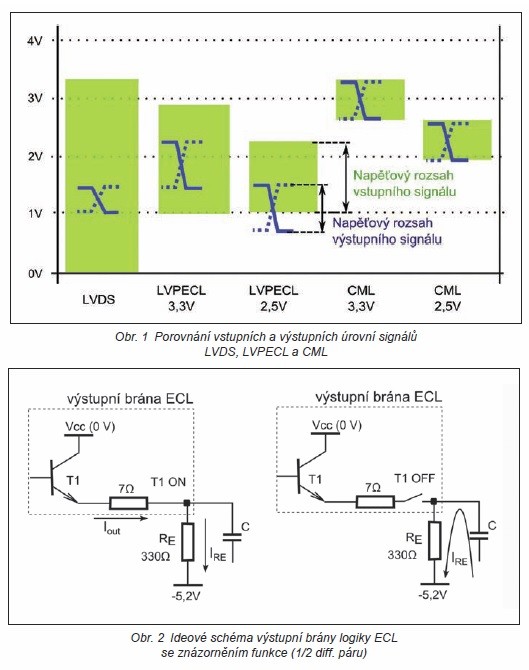

LVPECL můžeme zařadit spolu s LVDS nebo CML do rodiny vysokorychlostních diferenciálních digitálních rozhraní s maximálními datovými toky 3–10 Gbit/s. Zatímco rozhraní LVDS se zaměřuje na nízkou spotřebu a optimalizuje EMI z pohledu vyzařování, LVPECL naproti tomu dosahuje vysokých hodnot strmosti hran signálu, například až 30 ps pro datový tok 1 Gbit/s. Toho se s výhodou používá pro rozvod hodinového signálu, případně pro vysokorychlostní optické rozhraní ETHERNET, kde je důležité dosáhnout nízké úrovně jitteru. Na obr. 1 je přehled pracovních rozsahů pro vstupní a výstupní signály výše zmiňovaných rozhraní.

Porovnáme-li rozsah použití jednotlivých rozhraní, LVPECL je možné používat pro datový tok až 8 Gbit/s, v extrémním případě až 10 Gbit/s. Naproti tomu pro rozhraní LVDS je hraniční datový tok přibližně 3 Gbit/s. Vysoká datová propustnost rozhraní LVPECL je vykoupena více než dvojnásobnou výkonovou ztrátou oproti LVDS. Pro nízké datové toky je spotřeba LVDS dokonce čtvrtinová. Rozhraní CML je využitelné pro vyšší datové toky stejně jako LVPECL, výkonová ztráta je někde mezi ztrátou LVPECL a LVDS.

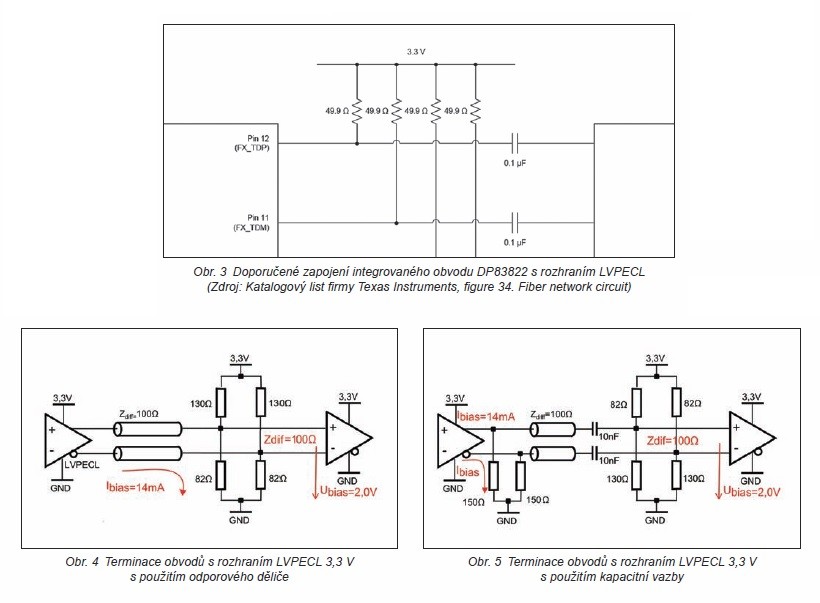

Nejprve trocha historického pozadí. Logické obvody LVPECL vývojově pocházejí z obvodů ECL Emiter Coupled Logic. Tyto obvody jsou v podstatě vývojově starší než logika TTL (1961). Poprvé jich bylo použito firmou IBM na konci 50. let v tranzistorovém počítači IBM 7090. Velkou předností je lineární průběh převodní charakteristiky, tedy absence proudových špiček při přechodu logického stavu a spínání tranzistorů mimo oblast saturace. ECL pracuje v lineární pracovní oblasti v zapojení emitorového sledovače, viz obr. 2. Vylepšení dynamických vlastností s sebou přináší nevýhodu v podobě statického odběru proudu.

Logika ECL pracuje se záporným napájecím napětím –5,2 V. Pro stav logické jedničky na výstupu (VOH) je výstupní úroveň napětí –0,9 V. Pro stav logické nuly na výstupu (VOL) –1,7 V. Pro záporné napájení –5,2 V se používala hodnota terminačního odporu v rozsahu 330–680 Ω proti zemi, což ne zcela vyhovuje typicky používaným impedancím na DPS, tj. 50–100 Ω. Řešením bylo použití pomocného napětí –2 V pro terminační odpor [3].

Kvůli možnosti propojení s logikou TTL a později CMOS se začalo pro ECL používat kladné napájecí napětí +5 V namísto záporného –5,2 V. Napěťové úrovně „pozitivní ECL“ PECL byly nadále definovány jako VOH = Vcc – 0,9 V a VOL = Vcc – 1,7 V. To s sebou přináší nevýhodu oproti ECL, logické úrovně se mění se změnou napájecího napětí.

V současné době je více než ECL používána logika LVPECL, tedy Low-Voltage PECL napájená napětím nejčastěji 3,3 V. Struktura obvodů LVPECL nemá s původními ECL obvody mnoho společného, bývá realizována CMOS technologií výroby. Jako příklad odlišné realizace výstupní brány můžu uvést doporučené zapojení obvodu DP83822 (integrovaný obvod fyzické vrstvy pro ethernet), viz obr. 3, kde je pro zajištění pracovního bodu výstupní brány použit „kolektorový“ rezistor.

Ve své praxi jsem se dokonce setkal s CMOS výstupem prezentovaným jako rozhraní LVPECL, kdy výrobce doporučoval pro dosažení kompatibilních úrovní zařadit sériový odpor 150 Ω. Rád bych zde upozornil na fakt, že LVPECL není definován standardem, jako je tomu například u rozhraní LVDS (TIA/EIA-644). Výrobcům součástek tak LVPECL poskytuje volnost, ovšem designérům elektrických obvodů může tato skutečnost působit potíže. Výše uvedené hodnoty jako VOH = Vcc – 0,9 V a VOL = Vcc – 1,7 V jsou sice obecně známé, nikoliv však závazné.

Výrobci nejčastěji uváděným doporučeným zapojením je použití odporového děliče z kombinace odporů 130 Ω & 82 Ω, viz obr. 4.

Toto zapojení v sobě kombinuje několik funkcí:

Vzhledem k „nestandardní“ definici vstupních a výstupních parametrů LVPEC může nastat situace, kdy výše uvedeným zapojením není možné splnit požadavky deklarované výrobcem „vysílače“ a výrobcem „přijímače“. Nejvhodnějším řešením kompatibility je použití kapacitní vazby. Funkce obvodu je poté možné rozdělit a přizpůsobit zvlášť pro pracovní bod vstupní a výstupní brány rozhraní LVPECL. Příklad takového zapojení je na obr. 5.

Častou chybou v návrhu je kombinace kapacitní vazby a děliče s rezistory 130 Ω a 82 Ω, kdy dojde k posunu pracovního bodu vstupní brány. Správnou hodnotou děliče pro zachování polohy pracovního bodu je kombinace odporů 130 Ω a 82 Ω, kde rezistor 130 Ω je zapojen proti zemi a rezistor 82 Ω proti napájecímu napětí 3,3 V, tak jak je tomu na obr. 5.

Pro redukci ztrátového výkonu je možné například kombinovat přímo zapojený diferenční odpor 100 Ω s děličem 2,7 kΩ a 4,3 kΩ [2].

V případech, kde má designér možnost volby, je lepší sáhnout po rozhraní, které se opírá o standard, jako je tomu například u LVDS. Řešení potenciálních problémů integrity signálů se tak omezí na porovnání se standardem a dobře definovanými limity. Pokud je z nějakého důvodu nutné využít rozhraní LVPECL, doporučuji použít zapojení s kapacitní vazbou. Často bývá nevyhnutelná i diskuze s výrobcem součástky, ne vždy lze nalézt v katalogovém listu kompletní výčet všech potřebných parametrů.

[1] LWDS Owner’s Manual; Texas Instruments, 2008

[2] Aplikační poznámka: HFAN-1.0 Introduction to LVDS, PECL, and CML, Maxim Integrated, 2000

[3] High-speed digital design a handbook of Black Magic, H.W. Johnson, M.Graham, 1993