Od vývojářů se dnes často žádají návrhy stále složitějších zařízení, které navíc musí být dokončeny v kratším čase. K jednoduchosti a hladkému postupu zde nepřidají ani požadavky související s dodatečnými bezpečnostními prvky daného produktu či jeho komplikovanější komunikací. Jindy se zase potýkáme s dostupností vývojářů pracujících na konkrétním projektu, kteří budou rozptýleni na mnoha různých místech. Projektový tým navrhující moderní DC/DC měnič do automobilového prostředí se tak může např. skládat z osob odpovědných za firmware napájecího zdroje žijících na jednom konci země a vývojářů stejně tak řešících komunikaci (stack), kteří ovšem pracují zase někde jinde. Zapracování kódu napsaného na různých místech do jednoho a téhož mikrokontroléru pak může zvyšovat riziko narušení časového plánu spojené se složitými vazbami mezi samostatně navrženým firmwarem.

Vývojáři navrhující špičkové řídicí vestavné aplikace s větším počtem softwarových týmů mohou nyní těžit z nové rodiny dvoujádrových kontrolérů DSC (Digital Signal Controller) v rámci jediného čipu umožňujícího snadnější začlenění softwaru. dsPIC33CH od společnosti Microchip Technology má jedno jádro navržené tak, aby sloužilo jako Master, a další pak na pozici Slave. V takto vznikající architektuře Master – Slave lze jádro Slave použít ve spojení s kódem řešícím speciální řízení s velkým důrazem kladeným na čas, zatímco jádro Master vytížíme funkcemi na systémové úrovni, včetně uživatelského rozhraní (UI), monitorování a komunikace, přesně s ohledem na koncovou aplikaci.

dsPIC33CH je navržen tak, aby pro každé jádro usnadnil nezávislý vývoj kódu samostatnými týmy, přičemž později, až se vše dostane na jeden společný čip, umožňuje bezproblémovou integraci. Duální nezávislá jádra zjednodušují vývoj firmwaru a podporují vývoj softwaru s větším počtem týmů, zatímco paralelně pracujeme na dvou úkolech. Řídicí smyčky náročné na čas mohou být odděleny od standardních funkcí typu UI, monitorování a diagnostiky či komunikace. Zrychlíme tak celý vývojový proces a umožníme každému jádru spolu s jeho kódem individuální a ještě efektivnější optimalizaci. To vše s minimální vzájemnou interakcí mezi oběma jádry, což dále usnadňuje ladění.

Rodina dsPIC33CH byla optimalizována s ohledem na vysoce výkonné aplikace z oblasti číslicově řešeného napájení, řízení motorů a také vestavných systémů, které se neobejdou bez sofistikovaných algoritmů. Typické oblasti ze světa napájení pro tyto dvoujádrové kontroléry zahrnují bezdrátové nabíjení, napájecí zdroje pro servery, DC/DC měniče, nabíječky nebo invertory. Rodina obvodů se bude rovněž hodit pro řízení motorů v čerpadlech, ventilátorech, dronech, robotických systémech, elektrickém nářadí a také dalších spotřebičích. Z pozice výkonného DSC obvody vynikají mezi čidly v elektronických systémech automobilů, v průmyslové automatizaci a řízení nebo u diagnostických systémů používaných v medicíně. Díky dvěma jádrům mikrokontroléru přítomným na stejném čipu struktury rovněž zajistí dostatek výkonu pro brány a hlavní procesory v aplikacích internetu věcí.

Uveďme si příklad číslicově řízeného zdroje napájení. Jádro Slave zde bude řešit matematicky náročné postupy, kdy řídicí smyčku na základě kompenzačních algoritmů s požadavkem na odpovídající rychlost uzavíráme v rámci firmwaru. Jádro Master pak nezávisle zvládá PMBus™ protocol stack a pro systém zajišťuje monitorovací funkce. Ve výsledku tak zlepšujeme vlastnosti celého návrhu, včetně jeho pohotových reakcí.

V případě ventilátorů, čerpadel nebo dalších aplikací pro ovládání motorů v automobilovém průmyslu lze jádro Slave vyhradit k řízení rychlosti a krouticího momentu s důrazem na čas, zatímco jádro Master ošetří otázku bezpečnostních postupů spolu se stackem pro CAN-FD (Controller Area Network Flexible Data rate) pro zajištění robustní komunikace, stejně jako ostatní funkce na systémové úrovni, včetně monitorování a diagnostiky.

A pokud jde o další výkonné vestavné aplikace spojené s elektronickými čidly v automobilech či systémech IoT, dokáže jádro Slave zrychlit provádění matematicky náročných funkcí, např. DSP filtrace vstupů senzoru, přičemž jádro Master napomůže v otázkách spolehlivosti a odolnosti vůči chybám v zapojeních se stěžejním požadavkem na bezpečnost.

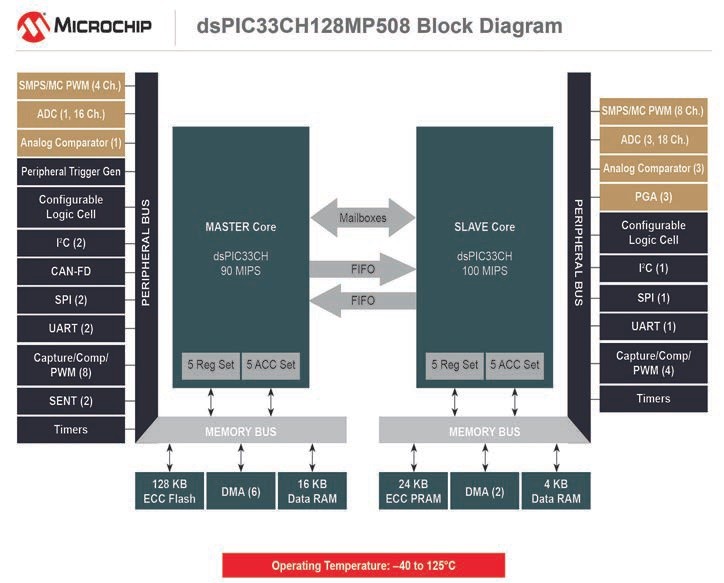

Jádro Master má k dispozici 64 až 128 kB Flash (program) spolu s ECC a také 16 kB RAM, zatímco Slave bude hospodařit s 24 kB RAM (program) s ECC a 4 kB RAM (data). S jednotkou Master se na 180 MHz pojí 90 MIPS a se systémem Slave pak na 200 MHz celých 100 MIPS. Oba procesorové subsystémy kromě toho nabízí vlastní řadiče přerušení, generátory hodin, logiku, I/O MUXy a PPS. Součástka se v podstatě stává ekvivalentem dvou kompletních DSC dsPIC® na jediném čipu.

Dvě jádra společně pracují bez problémů a pokročilým algoritmům napomáhají při zvyšování účinnosti a také s pohotovými reakcemi. A nejen to. Každé z nových jader v obvodech dsPIC33CH bylo navrženo tak, aby zajistilo větší výkony, než mohou nabídnout současná jádra DSC dsPIC. Stojí za tím více kontextově volených registrů zlepšujících reakce na přerušení, dále pak nové instrukce znamenající zrychlení činnosti DSP (Digital Signal Processor) a také svižnější provádění instrukcí. Uvážíme- -li výkonově náročné výpočty používané v řadě napájecích zdrojů, dosahují nové kontroléry spolu se svými jádry oproti předchozí generaci téměř dvojnásobné rychlosti popsané prodlevou 280 ns v porovnání s 543 ns.

Další klíčová výhoda rozdělování zátěže při zpracování mezi dvěma jádry DSC spočívá v rámci jediného prvku ve schopnosti dosahovat vyšší hustoty výkonu poplatně vyšším spínacím kmitočtům (více než 2 MHz oproti zhruba 1 MHz pro kontrolér s jedním jádrem), což může rovněž znamenat menší součástky. Aktualizace funkčního systému navíc umožňují upgradovat firmware bez nutnosti odstávky. To je obzvláště důležité v návrzích s požadavky na vysokou dostupnost, např. u napájecích zdrojů pro servery. Architektura dsPIC33CH také nahrává programování dvou jader s cílem vzájemného sledování z bezpečnostních důvodů a napomáhá tak robustnímu řešení systému.

Abychom dokázali snížit náklady a také rozměry desky, dostáváme pro každé jádro typické periférie zahrnující vysokorychlostní A/D převodníky (ADC), D/A převodníky (DAC) s možností generování průběhů, analogové komparátory, stejně tak i zesilovače s nastavitelným ziskem nebo podporu PWM (Pulse Width Modulation) spolu s vysokým rozlišením 250 ps. Uvážíme-li až 12 kanálů PWM, budou kontroléry vhodnou volbou pro záložní zdroje napájení (UPS), DC/DC měniče nebo AC/DC zdroje.

Obvody rodiny dsPIC33CH se stávají prvními dvoujádrovými, 16bitovými kontroléry DSC od společnosti Microchip, zatímco v pouzdrech o rozměrech jen 5 × 5 mm zajišťují nebývalou míru integrace. Jsou zároveň prvními dsPIC33 se schopností řídit spolu s posílenou šířkou pásma CAN-FD za účelem zajištění robustní komunikace. Dostaneme je v osmi variantách pouzder a podporovány budou ze strany vývojového ekosystému MPLAB® od Microchipu, včetně jejich volně dostupného, stažitelného a také oceňovaného IDE (Integrated Development Environment) MPLAB X a MPLAB Code Configurator.

Obvody dsPIC33CH od firmy Microchip výrobce optimalizoval pro účely vysoce výkonných vestavných řídicích aplikací pracujících v reálných podmínkách a s požadavkem na rychlou odezvu. Rodina dsPIC33CH podporuje oddělený vývoj kódu spolu s následnou hladkou integrací, přičemž dále snižuje náklady a také rozměry celého systému.