Test dosiek plošných spojov (DPS) môže predstavovať až štvrtinu celkových výrobných nákladov elektronického zariadenia. Vďaka včasnému plánovaniu v procese vývoja môžu byť tieto náklady zminimalizované. Pritom musia byť v testovacích konceptoch zohľadnené aj vodiče, ktoré sú umiestnené len na vnútorných vrstvách.

V elektronike naďalej platia dva podstatné trendy a majú vplyv na testovaciu stratégiu dosiek plošných spojov. Prvý z tých trendov je neustála miniaturizácia koncových produktov so stále menšími doskami plošných spojov, menšími súčiastkami a menšími predlohami dispozičného priestoru. Toto spôsobuje väčšiu hustotu v elektronických zariadeniach a vyžaduje uplatnenie nových technológií v dizajne.

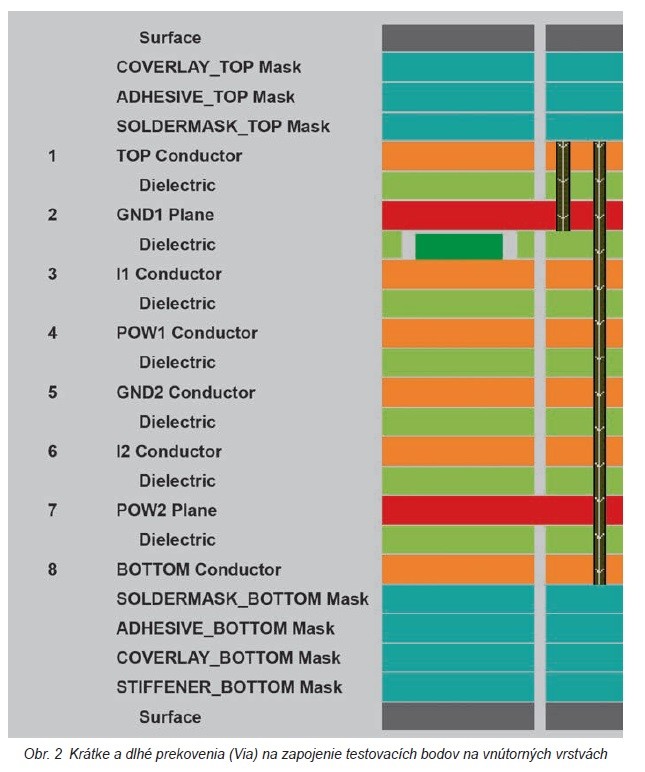

Prekovenia, ktoré vedú cez celú dosku plošných spojov, sa momentálne realizujú ako slepé a skryté (blind and burried) laserové prekovenia s omnoho menším priemerom dier. Konektory a káblové prepojenia sú nahrádzané pevno-flexibilnými zostavami. Súčiastky ako Embedded Components bývajú pevne vsadené na vnútorných vrstvách dosky plošných spojov. Vďaka nízkej hodnote napätia a modernej techniky prenosu signálu pri cca 1 V a precíznej leptacej technológie pri výrobe dosky plošných spojov sa naďalej zmenšujú štruktúry hrúbky a odstupu vodičov.

Druhým trendom je stúpajúca rýchlosť prenosu dát. So stúpajúcimi množstvami dát sa stávajú predpisy pre požadovanú kvalitu signálu komplikovanejšie a prísnejšie.

Hodnoty napätia, ale aj absolútne hodnoty tolerancie napätí klesajú. Pri vkladaní signálnych vodičov musia byť viac zohľadnené pravidlá návrhu. Aby sme predišli impedančným výkyvom, ktoré by mohli byť zdrojom problémov signálovej integrity, musia mať vodiče iba konštantnú šírku a pri diferenciálnych signáloch musia mať navyše aj pevný rozstup.

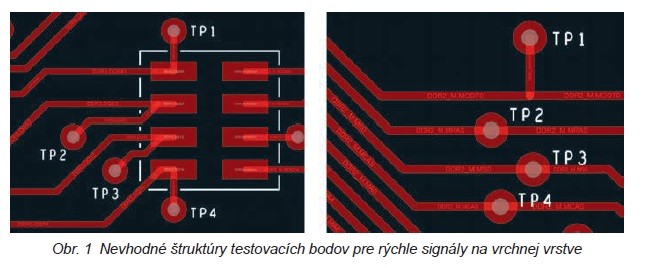

Všetko toto vedie k tomu, že sa na oboch vonkajších stranách dosky plošných spojov nenachádza miesto pre testovacie body, prípadne použitie testovacích bodov nie je povolené. Niektorí návrhári sa pokúšali presunúť za pomoci „Stubs“ (výčnelkov) testovacie body vedľa súčiastok tak, aby ich nezakrývalo puzdro súčiastky. Iní sa pokúšali testovacie body umiestňovať priamo na vodiče alebo pomocou tzv. „Stubu“ odbočiť testovací bod od vedenia signálu. Ale všetky tieto pokusy mali pri strmších krivkách stúpania signálov, prípadne vyšších frekvenciách značný negatívny dopad na kvalitu signálu. Vedú k impendančným výkyvom, a tým k reflexiám na vedeniach, alebo sa takýto „Stub“ správa ako anténa pre tento signál. Aj pole testovacích bodov na adresovej a dátovej zbernici má negatívny dopad na impedanciu vedení zberníc.

Dosky plošných spojov (ďalej len DPS) s pevne flexibilnou konštrukciou majú množstvo výhod, ale nevýhodou pri týchto druhoch PCB je zhoršená možnosť testovania. Jednou z hlavných výhod je aj redukcia konektorov, ale na druhej strane sa tým znižujú možnosti pripojenia na testovanie. V ohybnej časti DPS sú vodiče prekryté ochrannou vrstvou a tým pádom je vylúčené v tejto časti umiestniť testovacie body. Navyše aj v prechodnej časti medzi pevnou a flexibilnou zónou sú oblasti, kde je zakázané umiestniť testovacie body.

S vyššími hustotami integrácie súčiastok stúpa aj počet pinov na týchto súčiastkach. Mnoho signálov, ktoré prichádzajú z BGA, sú prepojené ihneď pod BGA do vnútornej vrstvy dosky, sú na tejto vrstve vedené k ďalšiemu BGA a vychádzajú na vonkajšiu vrstvu priamo pod týmto BGA. V osadenom stave dosky nie je tento signál prístupný z vonkajšej strany.

Vzhľadom na množstvo signálov pod BGA nie je možné pre každý signál vyviesť vodič mimo puzdra súčiastky BGA aj preto, lebo takýmto spôsobom by každý takýto vodič vytváral tzv. „Stub“ (výčnelok) predstavujúci pre signál anténu. Pre testovanie s hrotovými adaptérmi zostane teda len jedna možnosť a tou je otestovať dosku v neosadenom stave.

Testovacie body pre testovacie hroty môžu byť umiestnené buď na extra testovacích bodoch, alebo prekoveniach (Via) bez ochranného laku. Toto však platí len pri DPS s pomalými signálmi.

Pri rýchlych Gbit signáloch aj samotné prekovenie vplýva na kvalitu signálu, keďže prebytočný úsek prekovenia taktiež predstavuje „Stub“, ktorý sa správa ako anténa, a preto sú tieto nepoužiteľné ako testovacie body. V niektorých prípadoch je možné využiť mikrovia, ktoré vedú z vonkajšej vrstvy na niektorú z vnútorných vrstiev, ale aj táto možnosť ani zďaleka nepokryje potreby pre testovanie. Ďalej je tu aj riziko, že napriek takémuto riešeniu, ktoré na prvý pohľad vyzerá veľmi zaujímavo, je nutné zabezpečiť, aby taktiež na niektorom mieste nevznikol anténny efekt vďaka presahujúcej časti prekovenia, pričom kontrola je možná len manuálne.

Problém s testovaním už výrobcovia súčiastok identifikovali. Najskôr to boli výrobcovia BGA, kde je problém s testovaním najvypuklejší, keďže signály z neho sú obvykle ihneď vnorené do vnútornej vrstvy a tým pádom zvonka nedostupné. Preto bolo vyvinuté JTAG rozhranie, pomocou ktorého je možné vstavaným systémom otestovať funkčnosť samotného BGA. Tento malý testovací obvod je zakomponovaný v kremíkovom substráte čipu a je schopný sa pripojiť na ľubovoľný pin a taktiež ovládať jednotlivé funkcie čipu. Cez toto JTAG rozhranie môžu dva integrované obvody vzájomne komunikovať a spustiť testovací program. Na to sa vytvorí elektrické testovacie spojenie BGA. To isté sa stáva aj na druhom BGA tak, aby bol vytvorený elektricky uzavretý okruh. Táto technika pomocou JTAG rozhrania umožňuje nielen preveriť elektrické spojenie, ale dokonca aj otestovať funkcie súčiastok, ktoré sú zapojené medzi BGA, napríklad aj zmerať hodnotu sériového elektrického odporu.

V závislosti od zapojenia je možné pomocou technológie Boundary Scan dosiahnuť vysoké testovacie pokrytie. JTAG zbernice taktiež potrebujú miesto, ale môžu byť umiestnené aj na vnútorných vrstvách, a tak nie sú prekážkou v požadovanej miniaturizácii. Nezvyšujú prakticky ani počet súčiastok či potrebných spojov na DPS, pretože sú už nutnou časťou zapojenia, keďže sú potrebné aj na programovanie týchto súčiastok. Ďalšou výhodou je, že vďaka integrácii riadiacej časti priamo v súčiastke (BGA) nevytvárajú žiadne výčnelky (Stubs) pre signály.

So správnou stratégiou testovania je možné včasne a cielene rozhodnúť, ako a ktoré siete majú byť testované a ktoré podľa potreby nemusia byť testované. Toto rozhodnutie sú schopní urobiť vývojári včasne pri zostavovaní Layoutu a výrobe. Keď sa už v čase plánovania elektrického zapojenia sietí stanoví, na ktorých sieťach je nutné testovať, môže byť vypracovaná spoločná stratégia testovateľnosti. Pritom je nutné zohľadniť testovacie predpisy, ako napríklad špecifikovať počet testovacích bodov (0, 1 alebo 2) na jednej sieti a aké maximálne odstupy smú mať testovacie body od pripojených pinov. Také pravidlá môžu byť obvykle zadefinované v správcovi pravidiel (tzv. Constraint Manager) a rýchlo pridelené nejakej skupine sietí.

Ak je jasné, že táto elektronická zostava obsahuje signály, ktoré nie je možné dosiahnuť testovacími hrotmi, je nutné zmeniť stratégiu. Ak sa použije Boundary Scan, odporúča sa pokúsiť sa zredukovať čo najviac testovacích bodov a signály preskúšať týmto testovacím procesom aj kvôli zlepšeniu signálovej kvality zariadenia.

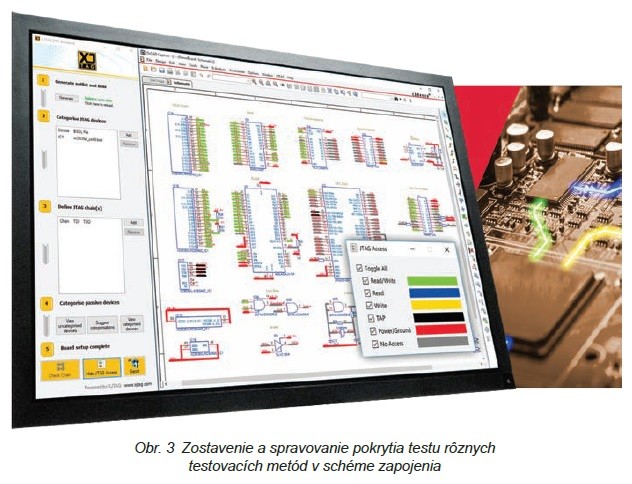

Ako sa zmysluplne rozhodnúť medzi rôznymi testovacími procesmi? XJTAG ponúka bezplatný softvér, ktorý spolupracuje s rozšírenými EDA nástrojmi, ako sú napr. OrCAD a Allegro od Cadence a taktiež aj nástrojmi od Mentor, Altium a Zuken. S XJTAG DFT Assistant sa dá automaticky pomocou celkového plánu zapojenia rozpoznať, ktoré signály sú prístupné pre JTAG-test. Výsledky sú zobrazené ako farebne vyznačené siete v schéme zapojenia. Používateľ si môže podľa potreby zvoliť v schéme zapojenia medzi nasledujúcimi Boundary Scan kategóriami sietí: čítanie, zápis, napájanie/ uzemnenie a siete bez JTAG-prístupu.

Pokrytie testu Test-Coverage je napr. v OrCAD Capture prehľadne zobrazené a je možné ho jednoducho zadokumentovať pomocou zaradenia a vyradenia v schéme zapojenia.

Pre siete, ktoré nie sú dosiahnuteľné s JTAG, je nutné zvoliť iné testovacie stratégie alebo zmeniť schému ich zapojenia. Je nutné premyslieť si procesy, kroky a časy pre test, ako aj dostupné miesto na doske plošných spojov a ich dopad na kvalitu signálu. Preto sa odporúča už vo fáze navrhovania zapojenia naplánovať testovateľnosť spolu s PCB návrhármi a výrobcami tak, aby bolo možné nájsť optimum pre dané elektronické zariadenie.

Viac informácií: FlowCAD EDA-Software Vertriebs GmbH, www.FlowCAD.de, www.FlowCAD.cz