Zatímco Signal Integrity (SI) analýzy jsou již v podvědomí mnohých návrhářů desek plošných spojů, o analýze Power Integrity se toho zatím moc neví. O co se jedná? Tak jako SI analýza umožňuje získat přehled o kvalitě přenosu signálu plošným spojem, PI analýza zjišťuje kvalitu rozvodu napájení na DPS.

Cílem analýzy je zajistit konstantní napájecí napětí s velmi malým (nebo ideálně s žádným) poklesem napětí u obvodů, které velmi rychle spínají. Zvyšující se počet různých napájecích napětí na desce, ale zejména nízkých napětí s úzkým rozsahem tolerovaných odchylek při podstatně vyšších odběrech proudu, výrazně komplikují správný návrh rozvodné napájecí sítě na desce. Nestabilní napájecí poměry na vývodech rychlých IO způsobují částečné nebo i úplné selhání správné funkce logických obvodů. Power Integrity analýzy se tak nutně stávají součástí komplexního návrhu desky plošných spojů.

Jedním z nástrojů pro PI analýzy na DPS je program Hyperlynx PI firmy Mentor Graphics [1, 2]. Podívejme se stručně na některé jeho funkce. PI analýzy jsou dosti široký pojem, a proto je tento program provádí ve 3 dílčích typech analýz:

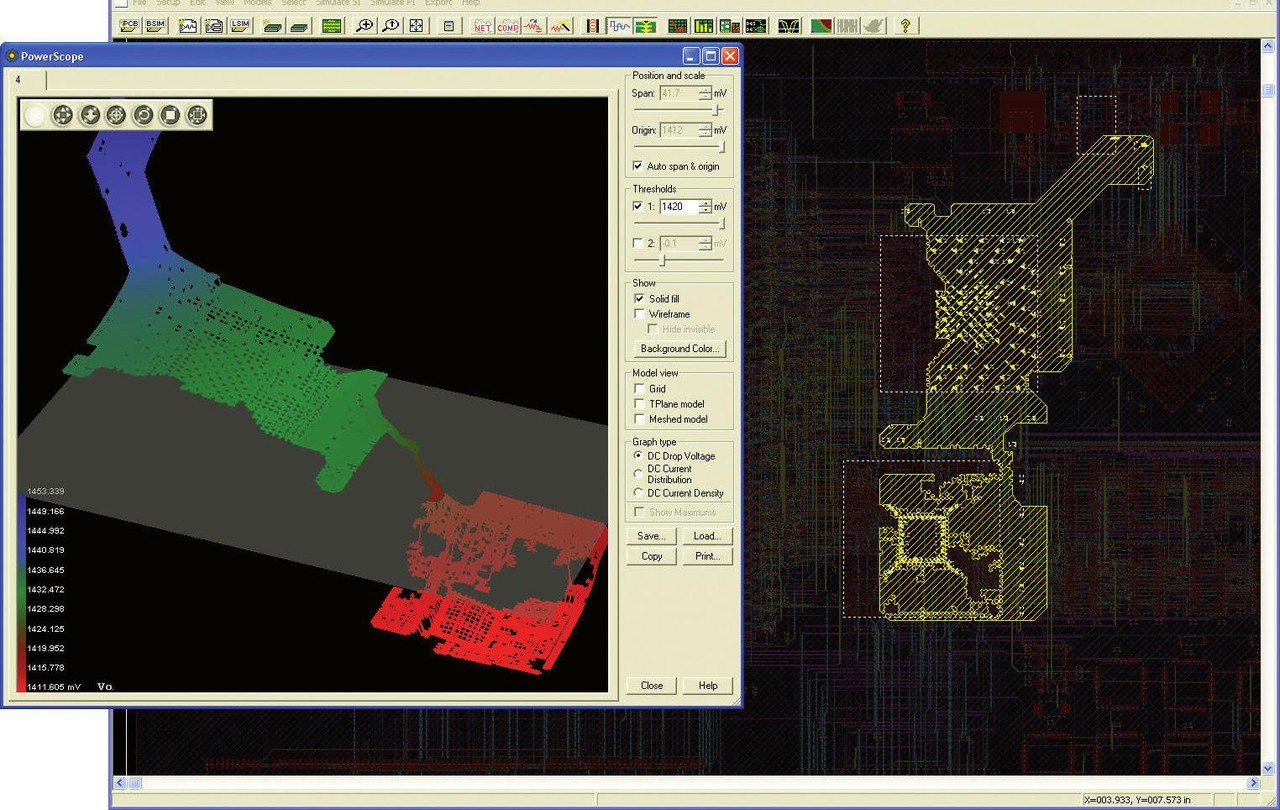

Tato simulace hlásí jak pokles napětí, tak také proudové hustoty v různých místech napájecích sítí. Tato simulace umožňuje získat přehled o důsledku zvýšeného odběru proudu na některých vývodech integrovaných obvodů a konektorů v DC módu (obr. 1).

na DPS 1.jpg)

Obr. 1 Analýza poklesu DC napětí

Přílišný pokles napětí, který je znám pod názvem „rail collapse” může způsobit, že napětí na napájecích vývodech IO klesne pod minimální doporučenou hodnotu. To může způsobit špatnou funkci IO, přičemž jeho vlastnosti se stanou nekontrolovatelné.

Přílišné proudové zatížení v zúžených místech napájecího rozvodu může způsobit nadměrné oteplení v měděných plochách napájecího rozvodu, které povede k poruše na desce v podobě odlepení mědi s případným zkratem na desce. Nadměrné proudy v prokovech mohou také vést k přerušení vodivého spojení.

Simulace poklesu stejnosměrného napětí nepřevádí proudové hustoty na teplotu, protože nemodeluje situaci, jak se teplo šíří z místa s nadměrným proudovým zatížením dále. Upozorňuje ale na oblasti s koncentrací toku proudu, které může vést k přílišnému oteplení.

Pokles napětí na desce lze simulovat ještě před vlastním návrhem DPS (prelayout), nebo až na již navržené desce (post-layout). Pre-layout návrh umožňuje provést analýzy v podobě „What-If“.

Napájecí sítě lze analyzovat jak jednotlivě, tak také všechny najednou. Přitom je možné definovat mezní hodnoty pro přílišný pokles napětí, proudové hustoty a proudy prokovu (via).

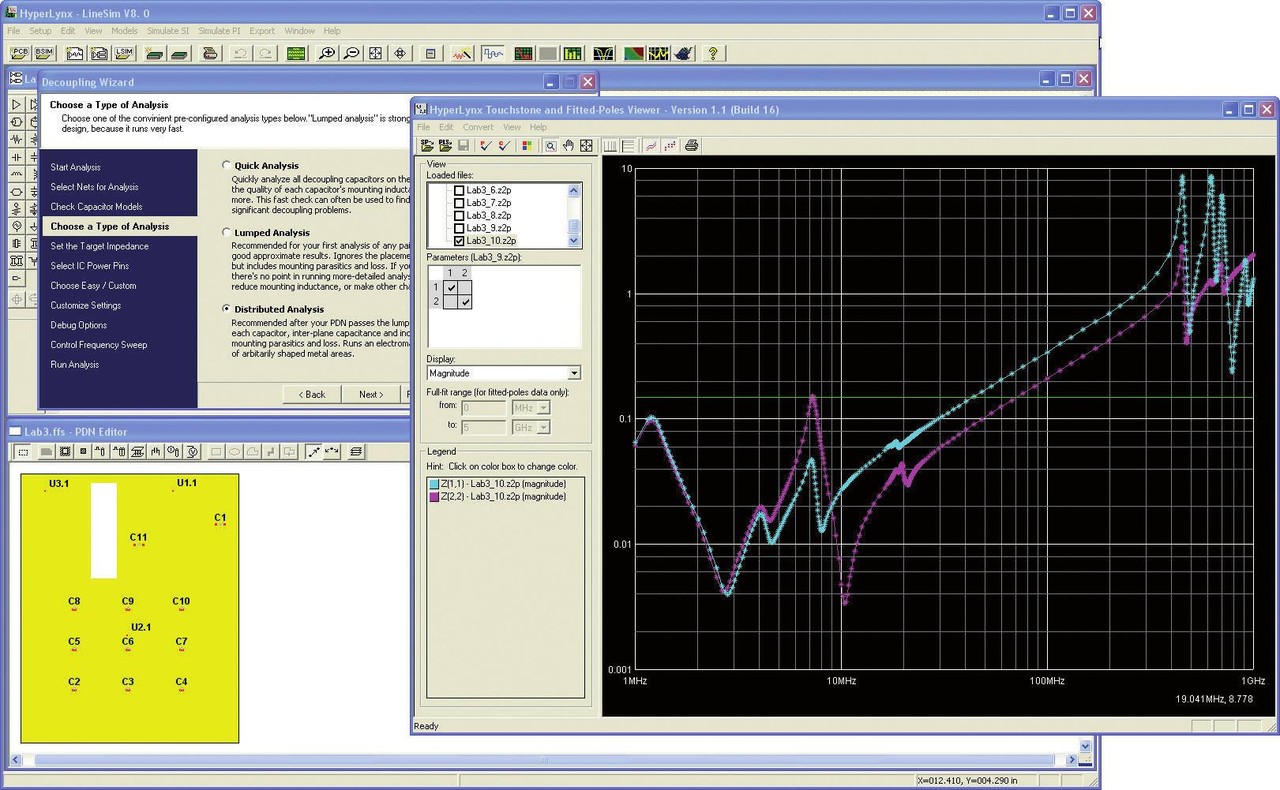

Tato analýza pomáhá vyhodnotit schopnost napájecího rozvodu zajistit přívod s nízkou impedancí k IO, přičemž typicky pokrývá široký rozsah frekvencí (obr. 2). Analýza zajišťuje následující úkoly:

na DPS 2.jpg)

Obr. 2 Analýza blokování napájení

Analýzu blokování napájení na desce lze také simulovat jak ve stavu ještě před vlastním návrhem DPS (pre-layout), tak i na již navržené DPS (post-layout).

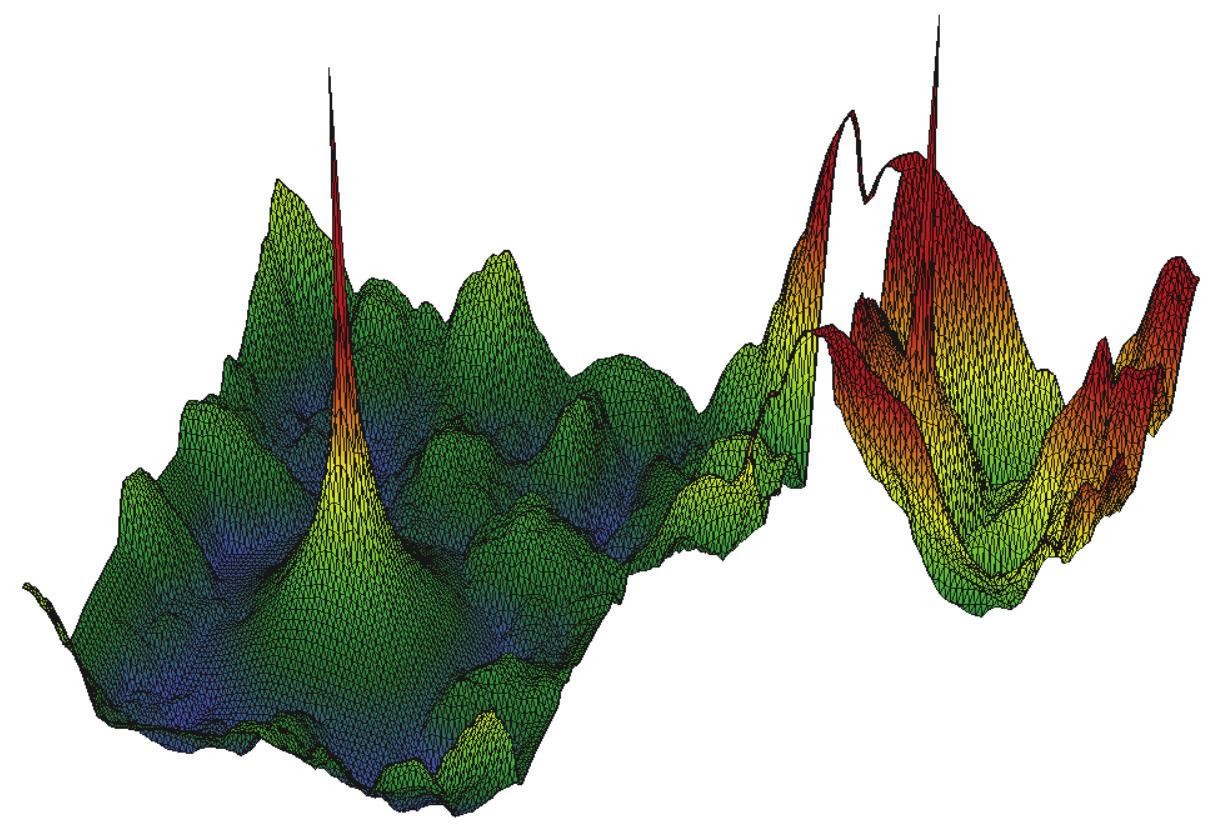

Simulace zvlnění napětí na napájecích plochách desky ukáže, jak se toto zvlnění šíří přes oblasti plochy, když napájecí vývody IO začnou přechodně odebírat podstatně větší proud během rychlého spínání. Simulace spočívá v použití proudového pulsu na jednom nebo několika napájecích vývodech IO, který napodobuje situaci, při které IO odebírá výrazně vyšší proud během změny logických stavů.

Výsledkem je hlášení o rozdílech napětí na napájecích plochách v různých souřadnicích X, Y. Tzv. PowerScope, který je zabudovaný v programu Hyperlynx PI, zobrazí potom výsledné zvlnění napětí ve 3D. V průběhu simulace je vidět, jak se v čase naměřené zvlnění v různých místech mění. Na závěr simulace zobrazí Power- Scope maximální hodnoty zvlnění přes celou napájecí plochu. 3D zobrazení umožňuje snadnou identifikaci míst na napájecí ploše, které vyžadují více blokovacích kondenzátorů (nebo také nahrazení stávajících kondenzátorů jinými s nižší indukčností připojení [3]). 3D zobrazení lze uložit pro pozdější analýzu (obr. 3).

na DPS 3.jpg)

Obr. 3 Vizualizace zvlnění napětí na ploše

Pro účely dalšího zpracování lze výsledky analýzy uložit také v textové podobě.

Zvlnění napětí na napájecích plochách desky lze rovněž simulovat jak ve stavu ještě před vlastním návrhem DPS (pre-layout), tak i na již navržené desce (post-layout).

V prováděných simulacích se pracuje s napájecí sítí PDN (Power Distribution Network), která zajišťuje napájení IO a pasivních součástek a současně i návrat proudu od napájecích vývodů. PDN zahrnuje měděné plochy desky, IO součástky, prokovy (vias), filtrační a blokovací kondenzátory (a jejich způsob uložení na desce), plošné spoje atd.

Program Hyperlynx PI získal v roce 2010 cenu v soutěži 2010 DesignVision Award for System Modeling and Simulation [4].

Hyperlynx PI načítá informace o navržené desce přímo z návrhového systému přes zabudovaný konvertor dat. Tak je možné převést desku z programů:

[1] Mentor Graphics: Hyperlynx PI Help

[2] http://www.mentor.com/products/pcb-system-design/

[3] Vít Záhlava: Návrh a konstrukce DPS

[4] www.mentor.com/products/pcb-system-design/news/pcb-hyperlynx-pidesignvision-award