V minulé části článku jsme se zaměřili na obecný popis platformy Altera SoC, která kombinuje procesor ARM Cortex A9 (HPS) a hradlové pole (FPGA). Dnešní pokračování se zaměří na konfiguraci a inicializaci obvodu SoC rodiny Cyclone V.

Proces konfigurace u obvodů SoC lze rozdělit na několik variant, kdy se každá varianta skládá z jednotlivých navazujících částí. Inicializaci lze vyvolat v zabezpečeném nebo nezabezpečeném režimu, kdy se využívá mechanizmus šifrování pomocí šifrovacích klíčů uložených v obvodu SoC, a to buď v interní paměti RAM zálohované baterií, nebo paměti Flash OTP – jednou programovatelná paměť.

Maximální flexibilitu konfigurace obvodu Altera SoC zajišťují tři základní režimy inicializace:

Primární je nastavení parametrů, ze kterého rozhraní se má systém inicializovat.

Typ konfiguračního režimu je volen pomocí vyhrazených konfiguračních pinů rozdělených zvlášť pro FPGA a HPS. Piny označené MSEL (4:0) slouží k výběru inicializačního rozhraní FPGA, a to jak v aktivním, tak pasivním režimu konfigurace.

Pasivní režim, kdy je FPGA konfigurováno externím zařízením (procesor, embedded systém, CPLD nebo jiné komunikační rozhraní), a aktivní režim, kdy si FPGA zajišťuje „aktivně“ generování všech potřebných signálů nutných pro čtení z konfiguračního obvodu (např. paměť SPI). Dále jsou rozhraní rozdělena dle bitové šířky na 1, 2, 4, 8 a 16 bitů. Větší bitová šířka vede ke kratším konfiguračním časům, ale na druhé straně negativně ovlivňuje spotřebu pinů daného FPGA.

Paralelní konfigurace v šířce osm nebo šestnáct bitů je nutná v případě připojení zařízení na sběrnici PCI Express, kdy zařízení musí být schopno provádět negociaci linky do 100 ms od vygenerování systémového resetu.

Sériový režim je vhodný u aplikací, kde předpokládáme co nejvyšší míru využití pinů FPGA v cílové aplikaci. Ve většině případů se jedná o připojení sériových pamětí typu SPI nebo QSPI. Doba inicializace při sériové konfiguraci obvodů SoC se pohybuje v rozsahu desítek milisekund až jednotek sekund v závislosti na velikosti FPGA, hodinové frekvenci konfiguračního rozhraní a kompresním poměru dané konfigurace (pokud je komprese aplikována).

Specifické postavení při konfiguraci obvodu SoC má rozhraní JTAG, které se využívá při ladění obvodu a zavádění uživatelské konfigurace a je obvykle aktivní a přístupné bez ohledu na nastavenou konfiguraci pinů MSEL.

Posledním konfiguračním režimem je konfigurace přes sběrnici PCI Express s protokolem CvP. Zde je třeba upozornit na fakt, že nejde o přirozený konfigurační režim nastavovaný pomocí pinů MSEL, ale o kombinaci standardní konfigurace a dynamické rekonfigurace FPGA.

Při návrhu designu je třeba mít na paměti, že nevhodná volba nastavení konfiguračních pinů MSEL může mít za následek blokování konfigurace FPGA ze strany HPS přes FPGA Manager.

Piny označené BOOTSEL (2:0) slouží k výběru rozhraní, ze kterého bude inicializován procesor. K dispozici jsou následující rozhraní:

Signály CLKSEL (1:0) upřesňují pracovní frekvenci pro jednotlivá konfigurační rozhraní. Frekvence je limitována v rozsahu 10–50 MHz.

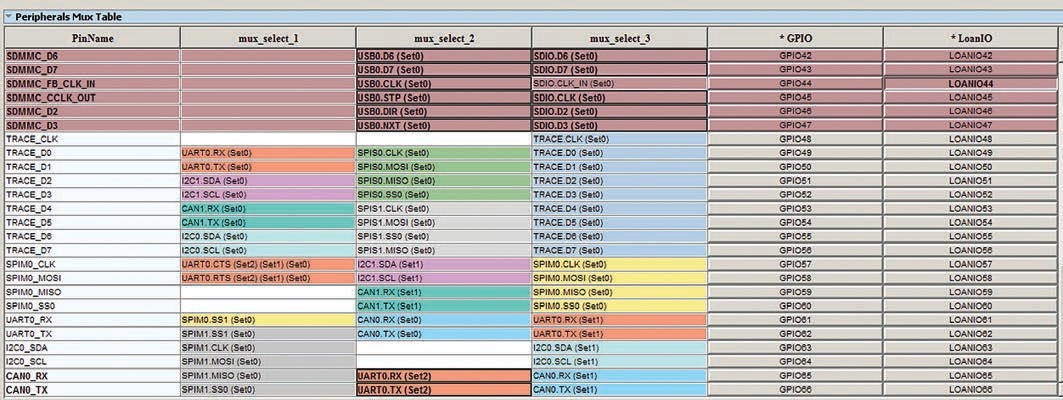

Definice vlastností a parametrů procesorového systému se obvykle provádí pomocí aplikace v nástroji Altera Qsys. Aplikace nastavuje mapování skupin pinů k jednotlivým periferním zařízením. Standardně jsou k dispozici tři skupiny umožňující mapování funkce na odpovídající vstup-výstupní pin. V případě, že na pin není mapována žádná periferie, je pin použit jako obecný vstup-výstup (GPIO). Poslední variantou mapování periferních zařízení je přemapování periferie na piny patřící FPGA. Typickým příkladem přemapování jsou rozhraní pomalejších sběrnic s jednosměrnými signály, např. CAN, UART, SPI. Příklad nastavení je vidět na obrázku 1. Dále je nutné pro HPS nastavit parametry generátorů hodinových signálů a paměťových rozhraní. Takto vzniklá konfigurace je zaváděna do procesoru při inicializaci systému softwarovým zavaděčem, který nastaví příslušné registry propojovacích a mapovacích komponent.

Obr. 1 Mapování periferních zařízení na piny HPS, popř. FPGA

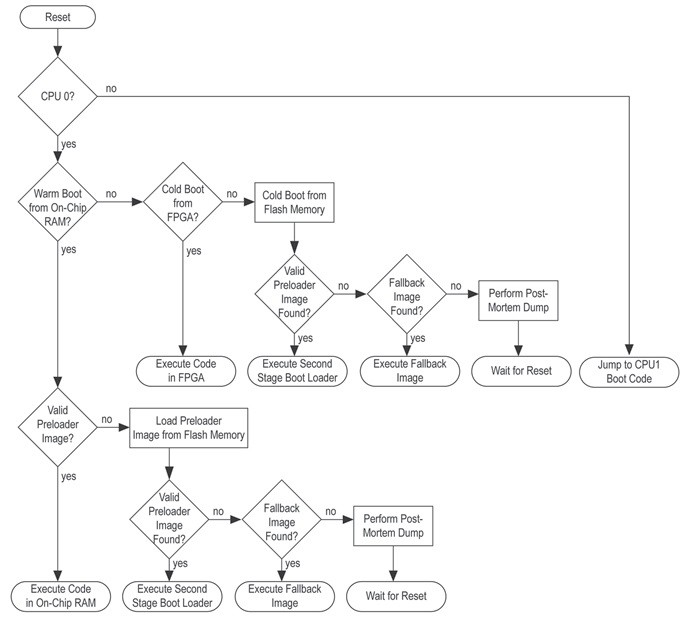

Po resetu HPS probíhá vícestupňová inicializace dle vývojového diagramu uvedeného na obrázku 2. Kód realizující základní operace konfigurace je uložen ve vnitřní paměti zvané BOOT ROM. Softwarový modul podporuje nepřímé a přímé spouštění Preloaderu. Nepřímé spouštění se používá u paměťově orientovaných zařízení, kdy je kód Preloaderu z paměti okopírován do interní paměti SoC. Přímé spouštění se využívá v případě spuštění kódu z oblasti FPGA, kde se využívá mapování na interní paměti FPGA.

Obr. 2 Postup inicializace HPS programem v BOOT ROM

Součástí Preloaderu je nastavení konfigurace vzniklé při generování designu. Běh Preloaderu není závislý na externích pamětech DDR, ale využívá pro svoji činnost interní paměť RAM o velikosti 64 kB. Preloader je vytvořen na základě modifikovaného zavaděče u-boot pomocí nástroje Qsys. Je zcela logické, že si uživatel může vytvořit vlastní Preloader dle potřeb cílové aplikace.

Po ukončení inicializace bude předáno řízení dalšímu softwaru. Obvykle následuje spuštění plné verze zavaděče u-boot, který pro svoji činnost využívá již externí paměť DDR.

Dále následuje spuštění uživatelské aplikace nebo spuštění operačního systému Linux, Windows Embedded, ...

Struktura hradlového pole může byt inicializována softwarem již od okamžiku předání řízení programu do Preloaderu. Následné změny konfigurace FPGA lze provádět softwarově v zavaděči u-boot nebo v operačním systému Linux.

V popisu byly velmi stručně uvedeny metody konfigurace a inicializace platformy Altera SoC Cyclone V. Problematika konfigurace obvodů SoC je ve skutečnosti mnohem komplikovanější, kdy zahrnuje mechanizmy inicializace více obvodů, částečnou dynamickou rekonfiguraci, mechanizmy řešení selhání inicializace a zabezpečení proti zneužití a odcizení vytvořeného kódu.

V příštích pokračováních seriálu se zaměříme interní propojení HPS a FPGA sběrnicí AMBA-AXI a mechanizmy přímého přístupu do paměti.