Pokud potřebujete kompletní vývojové prostředí pro návrh FPGA a ASIC obvodů, které vás dovede k cíli od konceptu až po implementaci, a to rychle a správně i v případě složitých projektů, potom software od firmy Mentor Graphics je pro vás tou správnou volbou. Podívejme se na nejvýznamnější nástroje, které jsou k dispozici:

HDL Designer Series [1]

HDL Designer kombinuje schopnosti provádět detailní analýzu, pokročilé editace a management celého projektu; to vše vytváří výkonné návrhové prostředí HDL, které zvyšuje produktivitu jednotlivých návrhářů i návrhových týmů (lokálních i vzdáleně propojených) a umožňuje opakovatelný a předvídatelný návrhový proces.

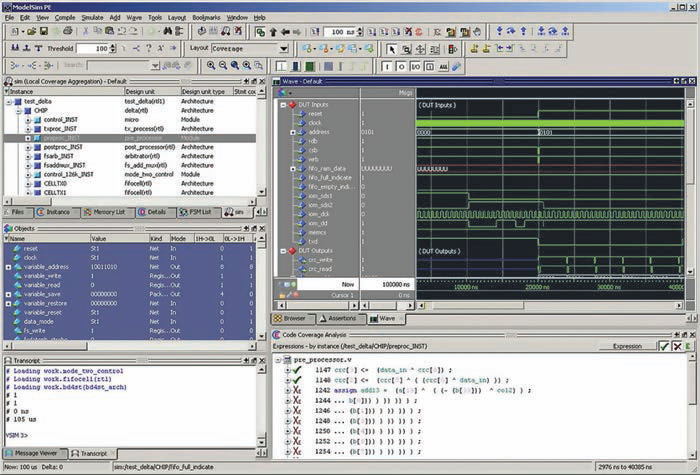

ModelSim [2]

ModelSim je nejrozšířenější SW nástroj pro simulaci a verifikaci FPGA, zejména díky výkonu a optimálně integrovanému prostředí pro ladění a analýzu. Jeho architektura podporuje všechny standardní jazyky, tj. VHDL, Verilog a SystemVerilog. Lze použít i PSL a SystemC.

Precision RTL Plus [3]

Precision RTL Plus je vlajková loď firmy Mentor Graphics pro syntézu FPGA, která disponuje mnoha jedinečnými funkcemi zejména pro aplikace komerční, letecké, vojenské a aplikace s extrémními požadavky na bezpečnost. Nejnovější verze zahrnuje podporu pro Actel, Altera, Lattice a Xilinx a rovněž OEM podporu pro Abound Logic, Achronix, Atmel, QuickLogic a TierLogic. Precision RTL dále podporuje optimalizaci aplikací s nízkým příkonem, bezpečnostní mód pro vojenské a letecké aplikace a aplikace s vysokými nároky na bezpečnost, integraci s nástrojem ReqTracer a šifrování IP.

Tyto SW nástroje slouží pro:

– modelování systémů

– pokročilou funkční verifikaci

– pokročilý návrh a verifikace FPGA (ASIC)

– návrh a verifikaci v jazyce C

– automatizace tvorby stimulů a testbenchů

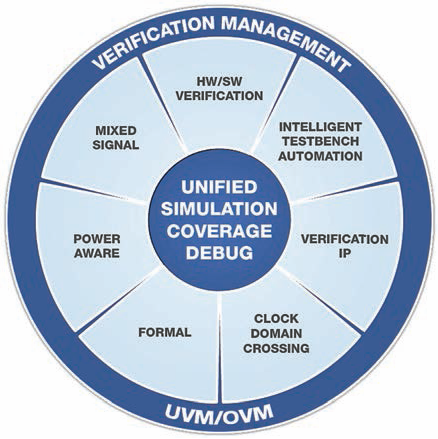

Questa [4]

Questa je mocná platforma pro funkční verifikaci zahrnující verifikaci založenou na assertions, verifikaci řízenou sledováním pokrytí, automatizaci vytváření stimulů a testbenchů, přecházení mezi hodinovými signály a verifikaci IP jader. Simulátor nativně podporuje všechny standardní jazyky, VHDL, Verilog, System Verilog, C, C++, SystemC (SCV a TLM) a PSL.

ReqTracer [5]

ReqTracer řídí požadavky v návrhových procesech pro FPGA a ASIC. ReqTracer zjednodušuje, automatizuje a umožňuje trasování požadavků od specifikace hardware přes kódování HDL až po implementaci a validaci výsledku. Podporuje práci s požadavky pro certifikaci DO-254.

FormalPro [6]

FormalPro je řešení vhodné pro výkonnou kontrolu ekvivalence pro regresní testování obvodů ASIC (FPGA) a IC se 100 000 a více hradly. FormalPro ověřuje s využitím techniky formální verifikace, zda je návrh ekvivalentní s referenčním („zlatým“) modelem.

Certe Testbench Studio [7]

Certe Testbench Studio nabízí výkonné a také přehledné prostředí umožňující pohodlnou tvorbu testbenchů založených na UVM/OVM a SystemVerilog pro složité návrhy ASIC/FPGA.

Visual Elite [8]

Visual Elite je nástroj postavený na silné infrastruktuře pro implementaci HDL umožňující vytvářet nejpokročilejší mechanismy a koncepty pro modelování na systémové úrovni (electronic systém level – ESL) a modelování na úrovni přechodů (transaction level modeling – TLM).

Obr. 1 ModelSim- uživatelské rozhraní

Vista [9]

Vista je nástroj na tvorbu virtuálních prototypů. Je založený na TLM 2.0 a umožňuje i analýzy a verifikace. Systémovým architektům a návrhářům SoC Vista usnadňuje rozhodování o architektuře. Hardwarovým a softwarovým inženýrům umožňuje ověřovat hardware a software.

Obr. 2 Questa – verifikační platforma

Odkazy:

[1] www.mentor.com/products/fv/hdl_designer/

[2] www.mentor.com/products/fv/modelsim/

[3] www.mentor.com/products/fpga/synthesis/precision_rtl_plus/

[4] www.mentor.com/products/fv/questa-verification-platform

[5] www.mentor.com/products/fpga/req_tracking/reqtracer/

[6] www.mentor.com/products/fv/formalpro/

[7] www.mentor.com/products/fv/certe/

[8] www.mentor.com/products/fpga/hdl_design/visual-elite-hdl/

[9] http://www.mentor.com/products/fv/vista

Pro více informací kontaktujte společnost ASICentrum spol. s r. o. (telefon: 226 772 222, mentor@asicentrum.cz).