Návrh vysokofrekvenčních DC/DC měničů s vysokým vstupním napětím

Ve snaze zmenšit velikost indukčností a výstupních kondenzátorů DC/DC měničů, jsou dnes v obvodech používány stále vyšší a vyšší spínací frekvence. Na trhu jsou k tomu rovněž stále více dostupné DC/DC měniče pro vysoké vstupní napětí, které zároveň obsahují ochranu před přechodovými jevy na vedení, ovšem při nízkém výstupním napětí jsou nucené pracovat s velmi nízkým pracovním cyklem. Řada výrobců se však tento fakt snaží zamlčet a cestou agresivního marketingu integrovaných řídicích obvodů vysokofrekvenční DC/DC konvertorů tvrdí, že jejich produkty snižují velikost zařízení a tím i výrobní cenu. Na první pohled se DC/DC měnič s provozní frekvencí 1 nebo 2 MHz může zdát jako skvělý nápad, ovšem v praxi vysoká rychlost spínání vstupního napětí ovlivňuje mnohem více faktorů, než jen velikosti a výstupní výkon zdroje. Tento článek má za cíl ukázat několik příkladů návrhu podobných měničů, včetně jejich výhod i problémů, plynoucích právě z vyšší spínací frekvence.

Volba aplikace

Abychom mohli tyto faktory snáze ukázat v praxi, byly navrženy a zkonstruovány tři různé napájecí zdroje s příslušnými provozními frekvencemi 100, 300 a 750 kHz. U všech tří návrhů bylo použito vstupní napětí 48 V, výstupní napětí 5 V a výstupní proud 1 A. Tyto požadavky jsou typické pro většinu aplikací s 5V USB portem nebo obecně mikroprocesorové systémy s 5V napájením z DC/DC měniče a případně dalšími LDO regulátory. Jako konstrukční omezení bylo určeno maximální povolené zvlnění výstupního napětí v hodnotě 50 mV, což je zhruba 1 % z výstupního napětí a špičkový indukovaný proud byl stanoven na 0,5 A. Ve všech třech případech byl použit obvod TPS54160 od společnosti Texas Instruments, což je 2,5 MHz, 60 V, 1,5 A stepdown DC/DC regulátor s integrovaným spínačem MOSFET. Výhodou obvodů TPS54160 je možnost externí kompenzace, snadné nastavení spínací frekvence a také skutečnost, že obvody jsou přímo určené pro použití v průmyslových aplikacích s vysokým vstupním napětím.

Výběr indukčnosti a kondenzátoru

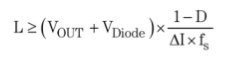

Ve všech třech případech byly indukčnosti a kondenzátory určeny podle následujících čtyř zjednodušených vzorců:

Pro indukčnost platí (1a):

V = L×di/dt

Což může být upraveno na (1b):

kde D (pracovní cyklus) = 5 V/48 V = 0,104 a DI = 0,5 A špička-špička.

Pro kondenzátor platí (2a):

I = C×dv/dt

což může být upraveno na (2b):

kde DI = 0,5 A špička-špička a DV = 50 mV.

V případě rovnice 2b se předpokládá, že zvolený kondenzátor má zanedbatelnou hodnotu ekvivalentního sériového odporu (ESR), což je případ keramických kondenzátorů. Keramické kondenzátory byly tedy z důvodu jejich nízkého vnitřního odporu a malých rozměrů použity ve všech uvedených návrzích. Násobek 2 v čitateli rovnice 2b představuje pokles kapacity vlivem stejnosměrného napětí, neboť s tímto účinkem není v katalogových listech většiny keramických kondenzátorů počítáno.

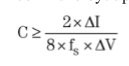

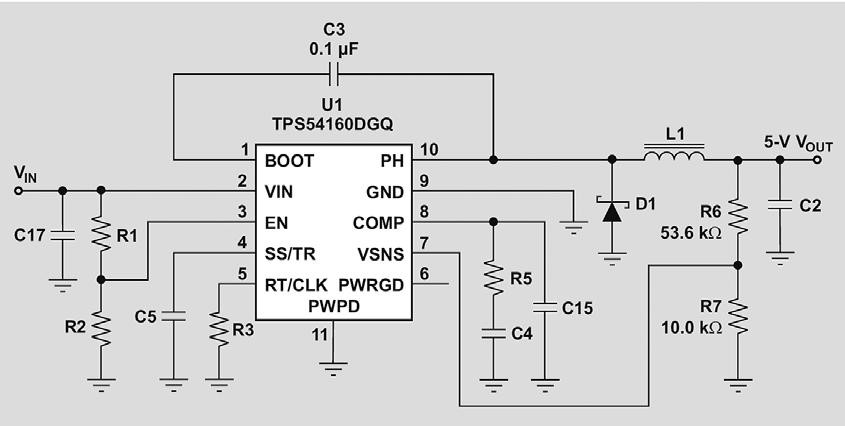

Obr. 1 Referenční zapojení s obvodem TPS54160

Obvod na obr. 1 byl použit pro srovnání výkonu všech tří aplikací. Součástky, které nemají ve schématu uvedenu svoji hodnotu, byly v každé aplikaci jiné. Výstupní LC filtr představují součástky L1 a C2. Hodnoty těchto součástek jsou pro všechny tři návrhy uvedeny v tabulce 1 a byly určeny na základě výsledků rovnic 1A až 2B. Všimněte si, že stejnosměrná hodnota odporu každé indukčnosti se vzrůstající frekvencí adekvátně klesá. To je způsobeno menším počtem závitů a kratším měděným vodičem cívky. Hodnoty kompenzačních prvků u chybového zesilovače byly navrženy nezávisle, zvlášť pro každou použitou spínací frekvenci. Rozbor jejich výpočtu však značně přesahuje rozsah tohoto článku.

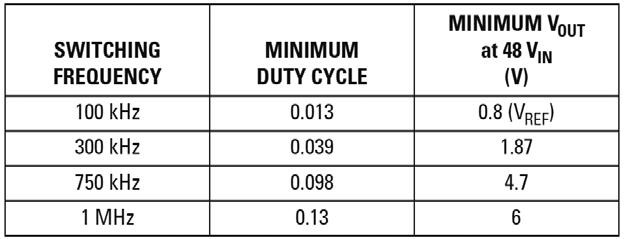

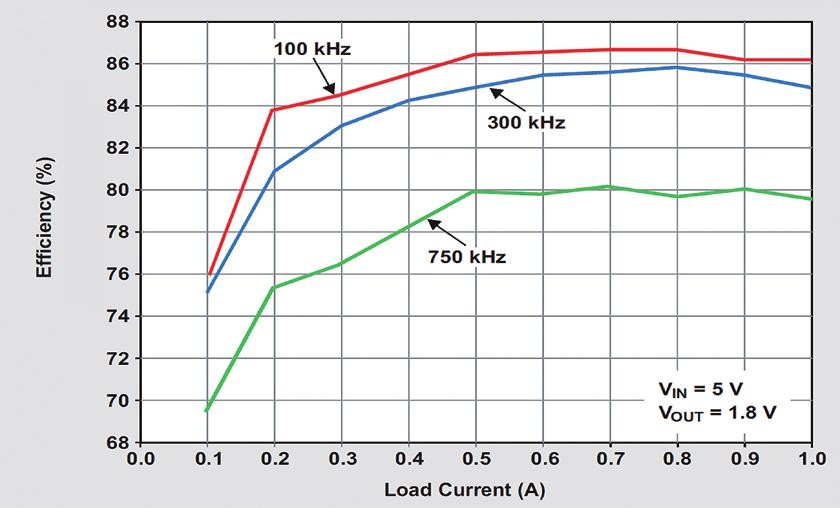

Tabulka 1 Hodnoty kondenzátorů a cívek pro tři testovací varianty napájecího zdroje

Minimální čas sepnutí

Řídicí obvody DC/DC převodníků se vyznačují omezením v podobě minimální délky sepnutého času (ON Time), který představuje nejnižší dosažitelnou šířku pulzu v pulzně- šířkové modulaci (PWM). Ve snižujícím převodníku pak tento čas představuje poměr doby sepnutého výkonového spínače MOSFET s názvem pracovní cyklus a jeho hodnota je rovna poměru výstupního napětí ku vstupnímu. V případě našeho obvodu převodníku s TPS54160 je hodnota pracovního cyklu 0,104 (5 V/48 V) a minimální doba sepnutí, jak je uvedeno v příslušném manuálu, vychází na 130 ns. Limit pro řízení šířky pulsu představuje maximální rozlišení a minimální dosažitelnou střídu lze snadno spočítat vynásobením nejkratší doby sepnutí a spínací frekvence. Jakmile známe požadovaný minimální pracovní cyklus, můžeme snadno spočítat nejnižší dostupné výstupní napětí, což lze provést jednoduchým vynásobením VIN a nejmenší hodnotou pracovního cyklu. Nejnižší výstupní napětí omezuje rovněž také hodnota referenčního napětí, která má v případě obvodu TPS54160 hodnotu 0,8 V.

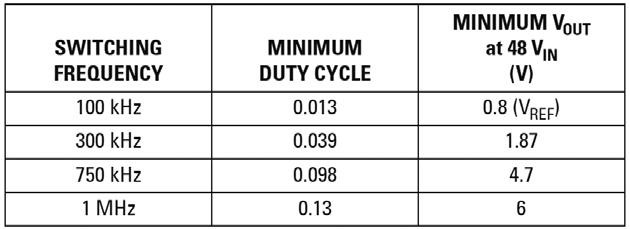

Tabulka 2 Minimální výstupní napětí při 130 ns – nejnižší hodnotě ON Time

V našem případě je výstupní napětí 5 V generované při spínací frekvenci max. 750 kHz (viz tabulka 2). Nicméně, pokud je spínací frekvence 1 MHz, je nejnižší možné výstupní napětí omezené na cca 6 V, v opačném případě začne DC/DC měnič vynechávat některé impulsy Alternativou je v tom případě buď snížení vstupního napětí, nebo pracovní frekvence. Konstruktér by si měl v datovém listu DC/DC převodníku ověřit garantovanou minimální hodnotu střídy a to nejlépe ještě před určením provozní frekvence.

Přeskakování pulzů

K přeskočení pulzů dochází ve chvíli, kdy DC/DC převodník není schopen vypnout výkonový spínač dostatečně rychle na to, aby byl zachován požadovaný pracovní cyklus/hodnota střídy. Jedná se tak o další způsob, kterým se obvod snaží regulovat hodnotu výstupního napětí, ovšem za cenu nárůstu zvlnění, způsobeného větší vzájemnou vzdáleností jednotlivých impulzů od sebe. Přeskočením pulzů vznikají v obvodu také další subharmonické frekvence, které mohou na výstupních prvcích představovat problémy v podobě nežádoucího rušení. V tuto chvíli se může dokonce stát, že obvod pro omezení výstupního proudu nebude pracovat korektně, neboť řídicí obvod nemusí být schopen reagovat na značné proudové rázy. Tento stav se může projevit špatnou funkcí regulačního obvodu a provoz celého napájecího zdroje může v tu chvíli vykazovat známky nestability.

Účinnost a ztrátový výkon

Účinnost DC/DC konvertoru je jedním z nejdůležitějších faktorů, které je třeba při každém návrhu zvážit. Nízká účinnost zdroje se negativně promítá do vyšší spotřeby energie a vyššího ztrátového tepla, které musí být odvedeno větším chladičem nebo další měděnou plochou na desce s plošnými spoji. Rovněž ztrátový výkon klade vyšší nároky na vedení napájecího proudu a obsahuje typicky několik složek, které jsou uvedeny v tabulce 3.

Tabulka 3 Prvky pro rozptýlení výkonu

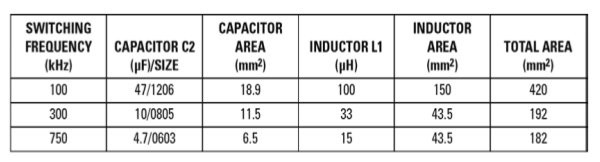

Mezi hlavní ztrátové prvky tří našich testovacích zdrojů patří především budicí ztráty FET, spínací ztráty a ztráty na indukčnosti. Odpor FET i ztráty řídicího IO jsou konzistentní, neboť ve všech třech případech se v obvodu používají stejné součástky. Stejně tak vzhledem k tomu, že ve všech případech byly použity keramické kondenzátory s nízkým ESR, jsou i ztráty u kondenzátorů zanedbatelné. Výsledný vliv vysoké spínací frekvence na účinnost napájecích zdrojů je dobře vidět v grafu na obr. 2. Z obrázku je patrné, že účinnost při klesající spínací frekvenci stoupá. Pro další zvýšení účinnosti zdroje při libovolné spínací frekvenci, by bylo nutné použít DC/DC regulátory s nízkým vnitřním Source-Drain odporem, nízkou kapacitou řídicí elektrody nebo nízkým vlastním proudem, specifikovaným při plné zátěži. Mezi další možnosti zvýšení účinnosti lze zařadit také kondenzátory a indukčnosti s velmi nízkou hodnotou ekvivalentního odporu.

Velikost prvků

Tabulka 4 Konstrukční rozměry a celková plocha zdroje

V tab. 4 jsou uvedeny celkové rozměry desky napájecího zdroje, včetně plochy pro kondenzátory a cívky. Jejich doporučená plocha je o něco větší, než je hodnota uvedená v tabulce, která byla získána z každého ze tří jednotlivých návrhů. Celková plocha desky byla následně odvozena rozšířením o příslušnou plochu každého jednotlivého prvku na desce, jako je řídicí obvod, filtr a všechny ostatní malé rezistory a kondenzátory. Získaná hodnota byla pro zajištění určitého rozestupu jednotlivých komponent následně ještě vynásobena číslem 2. Úspora celkové plochy zdroje ve výši 250 mm2 při přechodu ze 100 kHz na 750 kHz znamená již nezanedbatelný skok, získaný především o 50 % menší velikostí filtru. Dosažená úspora plochy desky tvoří hodnotu 55 %, nicméně i zde platí zákon klesající účinnosti, protože hodnotu kapacit a indukčností nelze snižovat libovolně! Jinými slovy, pokud budeme dále navrhovat zdroj s ještě vyšší frekvencí, nebude již možné velikost desky dále zmenšit o stejnou plochu, protože zde budeme narážet na omezení dostupnosti přiměřeně velkých, sériově vyráběných cívek a kondenzátorů. Všimněte si například, že 33μH a 15μH tlumivky zabírají na desce naprosto stejnou plochu. To proto, že tlumivka 33 μH je vysoká 3,5 mm, kdežto tlumivka 15 μH je vysoká pouze 2,4 mm. Tyto dvě tlumivky byly vybrány také proto, aby názorně ukázaly poměr indukčnosti k objemu.

Obr. 2 Účinnost obvodu TPS54160 v daných kmitočtech

Přechodová odezva

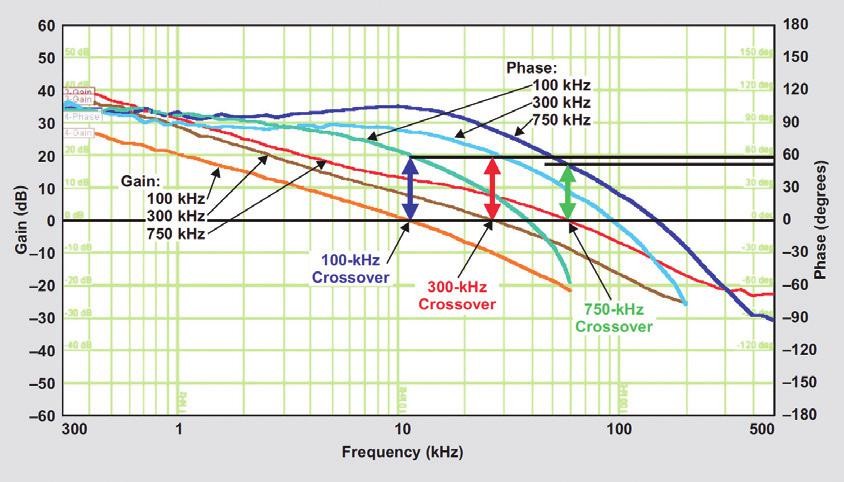

Obr. 3 Výsledek v Bode grafu pro 100, 300 a 750 kHz

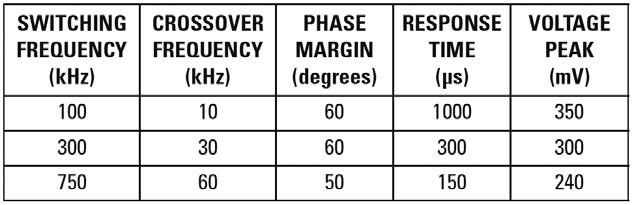

Přechodová odezva je dobrým ukazatelem úrovně výkonu napájecího zdroje. Bodové zakreslení každého napájecího zdroje bylo pro srovnání vyšších spínacích frekvencí uvedeno na obr. 3. Jak je z obrázku patrné, fázové rozpětí jednotlivých napájecích zdrojů se pohybuje mezi hodnotou 45 a 55°, což svědčí o dobře tlumené přechodové odezvě. Dělicí kmitočet se pohybuje přibližně kolem jedné osminy spínací frekvence. Při použití DC/DC regulátoru s vysokou spínací frekvencí by měl každý konstruktér rovněž ověřit dostatečnou šířku pásma chybového zesilovače. Jednotkového zisku chybového zesilovače pro TPS54160 by se mělo dosahovat kolem 2,7 MHz. Skutečné přechodové odezvy jsou, spolu se souvisejícími maximálními hodnotami napětí, uvedeny v tab. 5. Hodnoty mimo nám pak jasně definují nejnižší a nejvyšší spínací frekvenci, vztaženou vzhledem k velikosti šířky pásma.

Tabulka 5 Přechodová odezva

Pohled na jitter

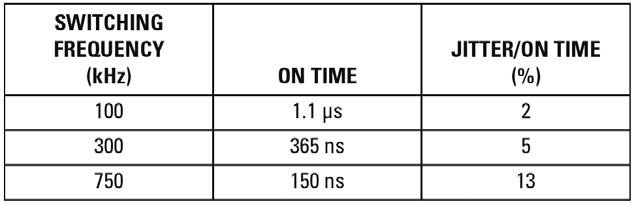

Vysoký konverzní poměr a vysoké spínací frekvence mohou být také zdrojem zvýšené úrovně rušení a produkovaného šumu. Při definici vysoké spínací frekvence by měl návrhář zvážit mimo jiné také hodnotu jitteru a minimálního času sepnutí výkonového prvku DC/DC převodníku. Šumový jitter roste s větším procentem spínacích impulzů při současně malém spínacím cyklu. Tabulka 6 ukazuje poměr jitteru a hodnoty ON Time v případě převodu 48 V na 5 V. Uvažujeme zde 0,5 V úbytek napětí na diodě a 20 ns fázový jitter.

Tabulka 6 Srovnání jitteru a hodnoty „ON Time“ při malých provozních cyklech

Závěr

To jsou základní kompromisy, které platí v případě vysokofrekvenčních spínaných napájecích regulátorů. Mezi hlavní výhody patří menší rozměry, rychlejší přechodová odezva a menší rozptyl napětí. Hlavními nevýhodami jsou pak nižší účinnost a větší rozptyl tepla. Tím však problémy ani zdaleka nekončí. Mezi další potenciální úskalí návrhu patří problémy plynoucí z vynechání impulzů a vyšší šum. Konstruktér by v technické dokumentaci, ještě před samotným návrhem vysokofrekvenčního zdroje, měl ověřit všechny důležité vlastnosti, jako např. minimální čas sepnutí, zisk chybového zesilovače v daném pásmu, odpor spínače FET a také z toho plynoucí spínací ztráty. Pokud se vše povede správně skloubit, lze z použití obvodu pro napájecí zdroje s vyšší spínací frekvencí vytěžit opravdu hodně a to i za nižší výrobní cenu či mnohem jednodušší konstrukci. V opačném případě může být konstruktér z výsledku velmi nemile překvapen.