Úspěch daného layoutu se odvíjí od dobře navrženého a také nakresleného schématu. Často se stává, že vývojáři, pracující na layoutu, umisťují součástky na desku plošného spoje podle jejich umístění ve schématu. Z tohoto důvodu je důležité kreslit integrované obvody ve schématech i s jejich skutečným, fyzickým přiřazením pinů a ne jinak, jen abychom zlepšili srozumitelnost daného zápisu.

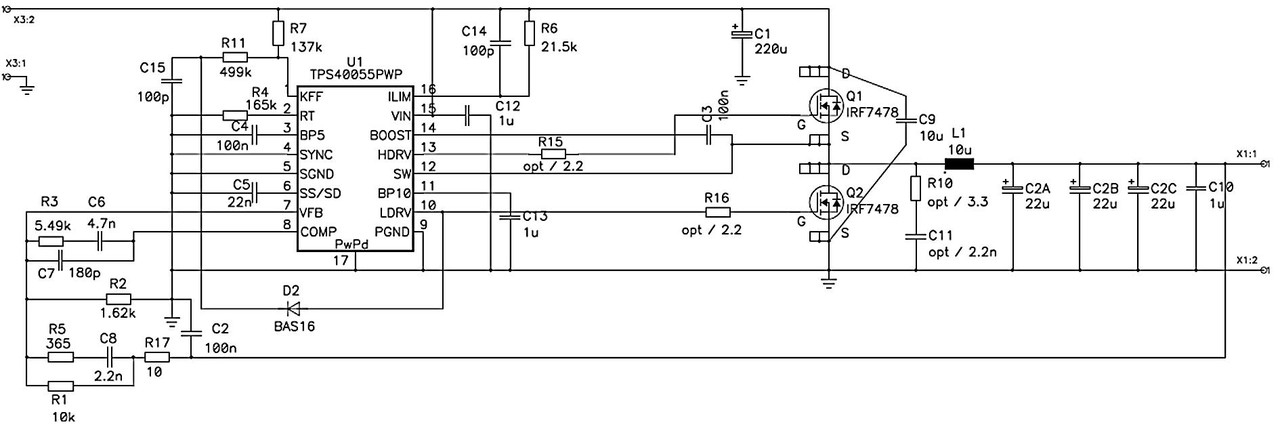

Blokovací kondenzátory by se měly kreslit těsně u příslušného integrovaného obvodu. Používá-li integrovaný obvod dvě země, signálovou (SGND) a výkonovou (PGND), měly by být nastavovací prvky (např. RT v souvislosti se spínacím kmitočtem nebo kondenzátor, určený pro soft start) již ve schématu připojeny k signálové zemi SGND.V případě blokovacích kondenzátorů, určených pro budiče hradel a jejich zpětné trasy, by však mělo být ze schématu na první pohled jasné jejich propojení s výkonovou zemí PGND. Krátké propojení mezi signálovou zemí SGND a výkonovou zemí PGND zase zdůrazňuje význam velmi malého odporu v místě styku obou zemí.

V případě výkonového stupně bude platit to samé. Vysokofrekvenční blokovací kondenzátory pro Vin by rovněž měly být zakresleny hned vedle spínacích MOSFETů, protože i na layoutu budeme muset dodržet stejnou podmínku tak těsného umístění, jak jen to konkrétní situace dovolí.

Obr. 6 Příklad náležitého schématu zapojení

Výstupní napěťový dělič bude zakreslen těsně vedle příslušného integrovaného obvodu – regulátoru. Výstup napájecího zdroje představuje uzel s nízkou impedancí, zatímco v případě středu výstupního napěťového děliče hovoříme o uzlu s vysokou impedancí, náchylném k navázání nežádoucího rušení. Natažení delší trasy z výstupu napájecího zdroje k děliči výstupního napětí se proto jeví jako výhodnější než umístění výstupního napěťového děliče na samotném výstupu napájecího zdroje a následné tažení dlouhé cesty až k uzlu FB daného regulačního obvodu. Konečně zde máme také přednostní připojení rezistorů a kondenzátorů v rámci kompenzační struktury, tak jak ji zachytil obr. 6. Jako nejlepší se přitom jeví propojení pinu FB s rezistory, které tak mohou určitou měrou potlačit nežádoucí signály. Prohodíme- li např.R5 a C8 a bude-li se na jejich společný vývod zároveň superponovat vysokofrekvenční signál, můžeme se s jeho minimálně potlačeným průběhem setkat až na pinu FB. Při náležitém propojení pracuje R5 proti zbylým rezistorům kompenzačního obvodu. Ve spojení se vstupní impedancí zesilovače odchylky tak zajistíme určitou míru zeslabení a tudíž i o něco méně zarušený napájecí zdroj. Výše zmíněné zásady podtrhuje schéma zapojení na obr. 6.

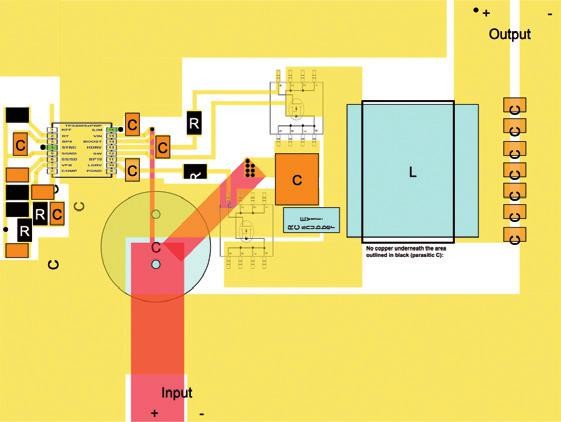

Chceme-li dosáhnout bezvadné činnosti spínaného napájecího zdroje, bude nezbytné vhodně zemnit. Pokaždé, kdy to jen bude možné, bychom měli použít jedinou zemní plochu (GND). Rovněž je vhodné zachovat měděnou vrstvu na straně součástek desky plošného spoje. Zemní plochy omezují prostor pro smyčky a také jejich indukčnost [1].

Řídicí signály integrovaného obvodu by se měly vztáhnout k oddělenému zemnímu ostrůvku. Takový samostatný GND ostrůvek se pak propojuje se zemní plochou prostřednictvím jediné trasy, vedoucí přímo k integrovanému regulátoru a jeho pinu GND. Zamezíme tak nechtěným průtokům proudu, který by jinak mohl způsobovat napěťové úbytky včetně interferencí. Takové interference by se totiž mohly navázat do signálové části integrovaného obvodu a způsobit jeho selhání. Bude-li mít integrovaný regulátor oddělené zemní vývody pro SGND a PGND, připojíme zemní ostrůvek, vyhrazený pro řídicí signály, nejprve k SGND a odtud pak k PGND, přičemž využijeme nejkratší možnou trasu. Předejdeme tak nežádoucím napěťovým rozdílům mezi piny SGND a PGND, které by mohly vést až k zablokování a následnému zabránění činnosti integrovaného obvodu.

Obr. 7 Správné zemnění

Horní vrstva GND je na desce plošného spoje vedena rovnou k pinu PGND příslušného integrovaného obvodu a odtud pak přímo k velkému vstupnímu kondenzátoru. Budeme-li předpokládat SMD součástky, propojíme přímo s horní vrstvou GND velkou vstupní kapacitu spolu s výkonovým MOSFETem (LowSide). I zbývající zemní plochy na desce plošného spoje by také měly být s touto kapacitou propojeny. Obr. 7 zachycuje příklad layoutu, ve kterém jsme výše zmíněné body již zapracovali.

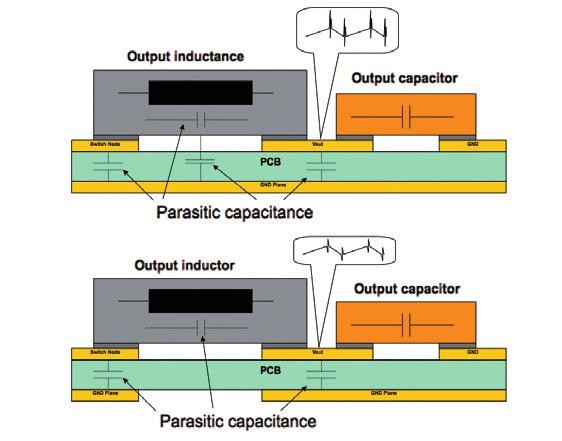

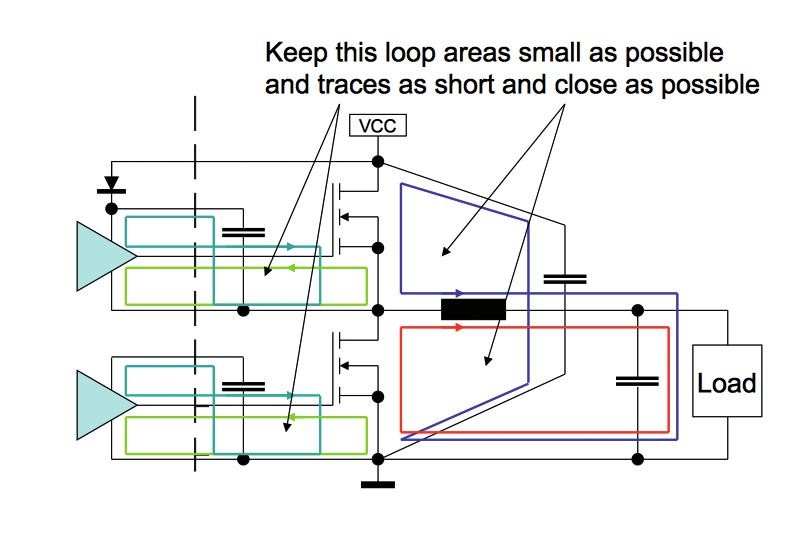

Jelikož výkonovým stupněm budou protékat velké proudy, je nesmírně důležité udržet proudové smyčky tak malé, jak to jen okolnosti dovolí. Malá plocha uzavřené smyčky snižuje indukčnost a minimalizuje rušivé emise. Požadavek na naprosté minimum platí také v případě parazitních kapacit, zejména pak v souvislosti se spínaným uzlem, který v případě snižujících měničů reprezentuje místo s největší změnou dV/dt. Jakákoli parazitní kapacita mezi tímto uzlem a zbývajícími trasami zvyšuje riziko rušivé vazby do dalších částí napájecího zdroje. Všechny vysokoimpedanční trasy bychom z tohoto důvodu měli směrovat co nejdál od tohoto spínaného bodu. Žádné cesty nesmí vést ani pod výstupní indukčností nebo spínaným uzlem. V praxi se rovněž osvědčilo vyloučit zemní plochu z místa pod výstupní indukčností, protože přechodové jevy se zásadními změnami dV/dt se mohou přes parazitní kapacity navázat na zemní plochu a odtud pak rovnou na výstupní napětí, kde vystoupí jako napěťové špičky. Jinými slovy, odstraněním země z místa pod výstupní indukčností snížíme parazitní kapacity a omezíme tak napěťové špičky výstupního napětí. Je však jasné, že se tímto způsobem špiček definitivně nezbavíme, protože výstupní cívka vykazuje sobě vlastní, parazitní kapacity, které zprostředkují rušivou vazbu mezi spínaným uzlem a výstupním napětím. Cestu, jak z toho ven, představuje výběr výstupní indukčnosti s malými parazitními kapacitami, které nebudou nežádoucí špičky dále podporovat. Na obr. 8 jsme celou situaci zobrazili graficky.

Obr. 8 Omezení výstupních napěťových špiček jde ruku v ruce s omezením parazitních kapacit

Nejkritičtější součástkou se v rámci našeho layoutu stává blokovací kondenzátor, zapojený mezi výkonové MOSFETy. Pro tuto pozici bychom tedy měli vybírat jen takové kapacity, které vykážou neobyčejně nízké hodnoty ESR a ESL. Jako nejvhodnější se pro tyto účely jeví keramické kondenzátory, které, pokud to bude možné, s výhodou použijeme. Kondenzátor přitom k výkonovým MOSFETům umístíme tak blízko, jak to jen bude možné. Pokud jde o parazitní indukčnosti, všechny vedou k extrémním napěťovým překmitům a mohou tak způsobit selhání napájecího zdroje. Kondenzátor se však s většinou vstupujícího, zvlněného proudu dokáže vypořádat, jen se při tom bude znatelně zahřívat. Pokud však na dané zvlnění s jednou kapacitou již nevystačíme a teplota nepřiměřeně narůstá, nezbývá než zvážit možnost paralelního řazení.

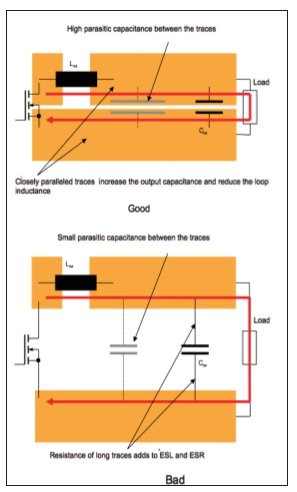

Obr. 9 Kritické smyčky

K dalšímu omezení parazitních impedancí přispějeme také tehdy, když zajistíme krátká propojení s výstupními filtračními kondenzátory. Udržením výstupních tras těsně vedle sebe vyrobíme malé, vzájemné parazitní kapacity. Takové parazitní kondenzátory pak mohou pomoci utlumit napěťové špičky, produkované spínaným uzlem.

Obr. 10 Těsně vedené výstupní trasy, podporující filtrační efekt, využívají parazitních kapacit desky plošného spoje

K potlačení nežádoucích kmitů a oscilací spínaného uzlu se někdy používá tlumící RC článek. Aby se však neminul účinkem, musí být k příslušnému bodu umístěn co nejblíže, přičemž zbytečně nelze protahovat ani propojení vůči zemi. Znovu zdůrazňujeme, že jakákoli indukčnost, představovaná delšími trasami, snižuje účinnost daného opatření a činí jej tak neupotřebitelným.

Jak již bylo zdůrazněno, největší hrozbu pro budicí stupeň MOSFETů představují parazitní indukčnosti. Klíčovou úlohu zde proto sehrávají krátké trasy spolu s malými smyčkami. Omezit indukčnost smyček se nám podaří tehdy, když navrhneme nejkratší možné cesty v souvislosti s hradlem a jeho zpětnou trasou. Zmíněné indukčnosti totiž vedou ke značným překmitům v signálové části, spojené s buzením hradla. Takové překmity způsobují EMI a mohou zničit MOSFETový budič řídicího integrovaného obvodu.

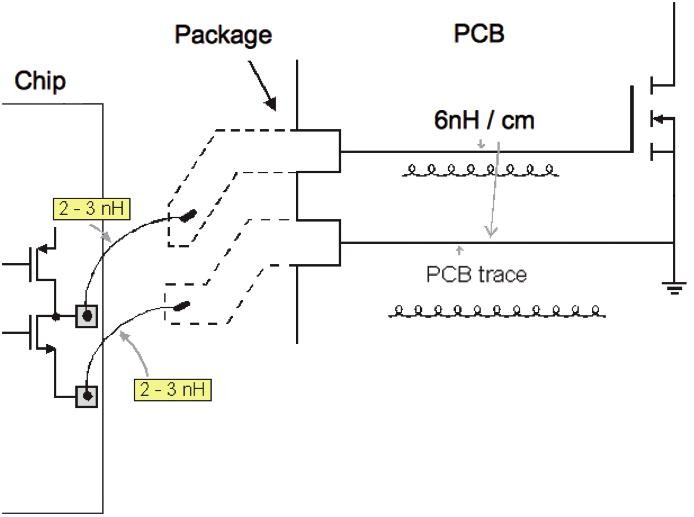

Obr. 11 Indukčnosti, zkoumané v souvislosti s buzením hradla a jeho trasami

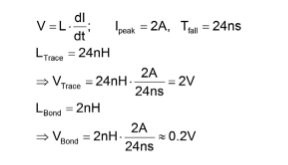

Prokovy by v cestě, určené k buzení hradla, neměly mít, pokud možno, žádné místo. Zvyšují totiž indukčnost a také odpor. Zase se však bude pochopitelně jednat o určitý kompromis mezi délkou trasy s a bez daného prokovu. Bude-li výsledná trasa bez prokovu mnohem delší než trasa s prokovem, zvolíme raději variantu s prokovem. Zapracujeme-li navíc důmyslné techniky layoutu, můžeme budicí stupeň včetně samotných MOSFETů často usadit na stejnou vrstvu a nasazení prokovů tak vyloučit úplně. Důležitost nejmenších možných indukčností, v souvislosti s návrhem tohoto druhu stupně, podtrhujeme krátkým výpočtem:

Drátová propojka mívá v integrovaném obvodu obvykle indukčnost přibližně 2 nH. Typický spínací čas pro lowside budič činí okolo 24 ns (uvažujeme kapacitní zátěž o velikosti 2,2 nF). Budeme-li dále předpokládat odpor budicího stupně RDSon o velikosti 5 ohmů, dostaneme při napětí budiče o velikosti 10 V špičkový proud přibližně 2 A. V rámci cesty dlouhé 4 cm pak získáváme následující napětí (předpokládáme 6 nH/cm délky trasy):

Na výstupu budiče hradla můžeme pozorovat překmity o velikosti 2,2 V. Takové stavy pak nejenže omezují fungování samotného driveru, ale mohou také znamenat, že MOSFETy s velmi malými prahovými úrovněmi pro spínání nebudou zcela vypnuty. Následně to pak spěje ke křížovému vedení, snížené účinnosti a v nejhorším případě až ke zničení napájecího zdroje.

Navrhujeme-li motivy pro integrovaný regulátor, bude nejdůležitější udržet vzdálenost k blokovacím kondenzátorům na nejmenší možné míře. Každá další indukčnost snižuje účinek těchto kapacit a znamená rušení na pinech integrovaného obvodu. Pro náležité fungování řídicího integrovaného obvodu nutně potřebujeme čisté napětí – pracovní a také referenční. Toto tvrzení pak získává na významu zejména v souvislosti s referenčním napětím nebo zdrojem, ze kterého interní referenci odvozujeme. Referenční napětí musí být mimořádně čisté, protože jinak můžeme do regulační části integrovaného obvodu vnášet rušení a získat naprosto nepředvídatelné chování. Součástky, které použijeme k vymezení funkcí regulačního obvodu např. jeho proudového omezení, spínacího kmitočtu, soft startu apod., musíme propojit se zemním ostrůvkem. Takový GND ostrůvek propojujeme jednoduchou propojkou přímo s pinem GND integrovaného obvodu. Má-li regulační obvod oddělené piny pro signálovou zem (SGND) a výkonovou zem (PGND), spojíme zemní ostrůvek nejprve s pinem SGND a odtud pak přímo s pinem PGND. Propojka mezi piny SGND a PGND musí být tak krátká, jak jen to bude fyzicky možné. Takový požadavek přitom vychází ze skutečnosti, že nesmíme naměřit žádné napěťové rozdíly mezi SGND a PGND, protože mohou způsobit zablokování integrovaného obvodu.

Regulační část řídicího integrovaného obvodu je nesmírně citlivá na rušení. Veškerá propojení by proto měla vykazovat velmi krátké trasy. Výstupní napěťový dělič bychom měli umístit co nejblíže samotnému čipu, přičemž spodní rezistor podepřeme zemním ostrůvkem SGND. Je potřeba vzít v úvahu, že všechny napěťové rozdíly mezi ostrůvkem SGND řídicího obvodu a zemním potenciálem GND výstupního napěťového děliče znamenají chybu výstupního napětí. Propojení, realizované s ohledem na malé impedance, takové chyby potlačuje. Zesilovač odchylky kromě toho zesiluje jakýkoli šum, přicházející z děliče výstupního napětí. Protože vstupem zesilovače odchylky rozumíme uzel s vysokou impedancí, budou k vedení nežádoucího rušení stačit jen malé parazitní kapacity. Jestliže signál ze spínaného uzlu s dV/dt o velikosti 1 V/ns navážeme do takového uzlu prostřednictvím malé parazitní kapacity 1 pF, můžeme jednoduše generovat proud o velikosti 1 mA. Impedance zpětnovazebního uzlu se běžně pohybuje v rozsahu 1 až 10 kΩ, takže takovými proudy můžeme vytvořit výrazné napěťové změny vstupu zesilovače odchylky. Takový stav se pak zpravidla projevuje kolísavým buzením hradla resp. oscilacemi, při kterých napájecí zdroj zkouší dorovnat chybu, generovanou zdrojem rušení. Z tohoto důvodu se důrazně doporučuje vést propojení mezi výstupem napájecího zdroje a souvisejícím výstupem napěťového děliče co nejdál od uzlů s vysokým dV/dt.

Při návrhu layoutu zkušební verze se vyplatí přidat vyhrazený prostor pro volitelné součástky. Může být například užitečné přidat zakončovací rezistor v sérii s horním rezistorem výstupního napěťového děliče, který využijeme při měření zpětnovazební smyčky síťovým analyzátorem. Při ladění zpětnovazební smyčky rovněž oceníme sériově či paralelně řazená místa v souvislosti s kompenzačními součástkami. Platí to ostatně i v případě, kdy bude požadována změna strmosti signálu, určeného pro buzení hradla. Stačí jen přidat plošky pro sériový rezistor, vřazený do cesty budicího signálu pro hradlo a nemusíme mít svázané ruce. V konečném návrhu pak takové prvky buď vynecháme nebo je nahradíme pevnými hodnotami.

Máme-li dokončen první prototyp, který se právě chystáme zapnout, nespěchejme – existují totiž určité procedury, které se před připojením napájecího napětí rozhodně vyplatí. V prvé řadě potřebujeme zkontrolovat polaritu diod a kondenzátorů. Další významný krok spočívá v prověření přerušených nebo zkratovaných tras ohmmetrem. Nezapomínáme ani na kontrolu zapojení s ohledem na studené spoje či zkraty, vzniklé při pájení sousedních vývodů.

Pokud vše proběhlo bez potíží, můžeme konečně přivést napájecí napětí. Pro tyto účely bychom však měli používat výhradně laboratorní zdroje s proudovým omezením a dostatečně filtrovaným výstupním napětím. Abychom snížili indukčnost, doporučujeme pro připojení výstupu laboratorního zdroje ke vstupu našeho prototypu použít kroucený kabel. Pro nízkoimpedanční zakončení dále přidáváme elektrolytický kondenzátor na vstupní svorky napájecího zdroje.

Důležitou úlohu rovněž hraje správné zemnění připojených měřidel. V některých případech můžeme osciloskopem a jeho sondami vyrobit zkraty v měřeném modulu. V případě izolovaných napájecích zdrojů a příslušného měření signálů na primární a také sekundární straně to pak může mít katastrofální následky. Vyhráno nemáme ani v případě dvou samostatných, ale uzemněných přístrojů. Zemní spojení, představované vodičem PE, bude totiž i zde znamenat zkrat mezi sondami a jejich zemním zakončením. V takových situacích musíme zkrátka použít vysokonapěťové, rozdílové sondy.

Připojujeme-li k výstupu testovaného zařízení (DUT) elektronickou zátěž, musíme se ujistit, že pracuje v „odporovém” režimu. Máme-li totiž zvolen režim „konstantního proudu” nebo „konstantního napětí”, bude zpětnovazební smyčka testovaného napájecího zdroje narušovat činnost regulační smyčky zátěže. Takový stav pak nevyhnutelně vede k oscilacím, přičemž zpětnovazební smyčka napájecího zdroje se bude jevit jako nestabilní. Takže dříve, než obviníme zpětnovazební smyčku z nestability, běžme zpět a zkontrolujme, zda elektronická zátěž ve skutečnosti pracuje v „odporovém” režimu.

Při prohlížení nejrůznějších průběhů, naměřených v našem zapojení, musíme čelit některým běžným problémům např. rozhodnutí o tom, co se skutečně děje. Když získáme průběh se spoustou šumu, bude takové rušení skutečné nebo má původ někde jinde? Jedním z velkých zdrojů takto vznikajícího, obrovského množství nežádoucího rušení se stává zemní vývod osciloskopické sondy. Krokodýlek i s jeho kabelem dlouhým 15 cm vytváří fantastickou anténu, přičemž vznikající výrazná smyčka nepochybně ovlivní čistotu naměřených průběhů.

Bude proto lepší se úplně zbavit jak samotné špičky osciloskopické sondy, tak i zemního vývodu a použít místo toho malé adaptéry. Nově vzniklé vývody musíme v rámci prototypu pájet tak blízko, jak to jen okolnosti dovolí, resp. s minimální smyčkou mezi zemí a skutečným středem použitého konektoru. Zapojíme-li pak také osciloskop, získáme mnohem lepší a také přesnější výsledky.

Pokud přesto vyžadujeme určitou míru flexibility, můžeme i takový adaptér využít jako sondu, jen bude potřeba provést určité rozšíření včetně nějaké „ohebné” země. Nesmíme však zapomenout, že již ale vytváříme smyčky, takže rozhodně zbytečně neprodlužujeme rozměry a zajišťujeme minimální plochu případných smyček, jen abychom dále nezhoršovali šumové pozadí.

Osciloskopická sonda by se měla zemnit přímo na regulačním integrovaném obvodu, protože je to místo, ke kterému vztahujeme všechny řídicí funkce.

Obr. 12 Měření se standardní sondou, vybavenou zemní svorkou (nahoře) a příslušným adaptérem (dole)

Obr. 12 porovnává dvě měření realizovaná na stejném uzlu jen s různým zakončením použité sondy. Na obrázku vlevo vidíme signál změřený běžnou sondou i s jejím, přibližně 15 cm dlouhým zemním zakončením. Pozorujeme zde přitom výrazný šum. Na obrázku vpravo jsme stejný signál změřili adaptérem, který byl nakonec zapájen. Takové měření zajišťuje výrazně lepší výsledky (čistotu signálu).

[1] Robert Kollman, “ConstructingYourPower Supply – Layout Considerations”, Texas Instruments Power Supply Design SeminarSEM1600, Topic 4, TI LiteraturenumberSLUP224 http://www-s.ti.com/sc/techlit/slup230.pdf