Přílišné vyzařování elektromagnetických vln spojené s přenosem spínaných signálů a citlivostí obvodů u rychlých digitálních systémů nutí návrháře DPS k vyvinutí nových technik návrhu desky.

The Australian Electronics Development Centre (AEDC) pravidelně pořádá v Austrálii a na Novém Zélandu dva kurzy: „Pokročilý návrh pro povrchovou montáž“ a „EMC – řešení problému“. Oba kurzy poskytují velmi užitečné informace pro návrh desky s ohledem na EMC.

Ačkoliv je většina problémů s EMC spojena se zemněním a stíněním šasi a kabelů, musí návrháři desek s rychlými obvody věnovat pozornost efektům přenosové linky.

Například v případě opodstatněných časovacích požadavků bude potřeba použít v návrhu součástky různých logických skupin. Kdekoliv je to možné, měly by být tyto skupiny uzavřené, ohraničené. Více zemnicích vývodů součástky nebo konektory s řízenou impedancí mohou sice znamenat menší prostor pro pokládání spojů nebo vyšší cenu součástky, ale mohou také být tím rozlišovacím faktorem mezi funkčním a nefunkčním výrobkem.

Geometrie přenosové linky (plošného spoje) a sestavení vrstev desky jsou kritickými faktory. Impedanční přizpůsobení, strmost hrany, přeslechy, souběžnost a připojení napájení, to všechno ovlivňuje tzv. signal integritu přenosu signálu. Ačkoliv jsou na trhu EDA programy, které mohou pomoci kontrolovat tyto problémy, nejlepší je rozumět příčinám a efektům elektromagnetické interference a kompatibility a vědět, jak si udržet nad návrhem desky kontrolu.

Při vysokých frekvencích se plošné spoje na desce chovají jako unipól nebo smyčková anténa. Tzv. nesouhlasné rušení (Differential-mode radiation) je elektromagnetické vyzařování způsobené proudy složek harmonických frekvencí proudících v desce ve smyčce. Vyzařování je úměrné ploše proudové smyčky a mocnině kmitočtu signálu. Souhlasné rušení (Common-mode radiation) je elektromagnetické vyzařování způsobené proudem v nepřizpůsobeném plošném spoji (nebo zakončeném připojením na vstup s vysokou impedancí) a může vyžadovat zakončovací rezistor k potlačení odrazů. Vyzařování je podobné dipólu antény a jeho velikost je úměrná proudu, délce plošného spoje a kmitočtu.

Vysokofrekvenční složky základu (nejnižší kmitočet v komplexní vlně) vyzařují naneštěstí ochotněji, protože jejich kratší vlnové délky jsou porovnatelné s délkou plošných spojů, které fungují jako antény.

I když amplituda složek harmonických frekvencí klesá se stoupající frekvencí, vyzařované frekvence se liší podle charakteristik antén/plošných spojů. Například interferenční signály generované digitálními obvody inklinují k hodnotám v rozsahu 10 až 300 MHz.

Při jaké rychlosti bychom se měli zajímat spíše o šíření vln, než jenom o proud ve vodičích? Efekty přenosové linky se zpravidla stávají důležitými v úvahách návrhu desky, když se délka plošného spoje blíží 1/7 vlnové délky přenášeného signálu. Při hodinovém kmitočtu systému 300 MHz je vlnová délka v materiálu desky FR4 kolem 0,5 m.

Systémové hodiny jsou opakovaný sled pulzů s pravoúhlým průběhem, kde informace o stavu „1“ nebo „0“ je přenášená na vstupní hraně pulzu.

Této hraně pulzu musí být umožněno stoupat a klesat co nejrychleji. Kmitočet a náběžná hrana signálu jsou vzájemně vázány vztahem:

Tr (náběžná hrana v ns) = 0,35 / kmitočet v GHz

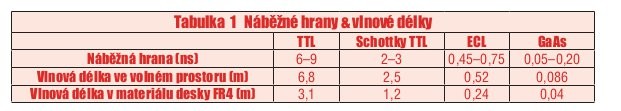

Tabulka 1 Náběžné hrany & vlnové délky

Tabulka č. 1 ukazuje náběžnou hranu a vlnové délky pro různé integrované obvody.

Např. pro ECL:

kmitočet = 0,35 / 0,45 = 777 MHz

Z této frekvence vychází vlnová délka kolem 375 mm ve vzduchu nebo 175 mm v FR4 materiálu desky a 100 mm v keramice. Z toho vyplývá, že pokud je délka plošného spoje větší než 25 mm na desce vyrobené z FR4, musí být potom brány v úvahu elektromagnetické vlastnosti ECL signálu a efekt přenosové linky.

Z toho také vyplývá, že strmost náběžné hrany a ne hodinový kmitočet signálu určují kritickou rychlost signálu. Strmá náběžná/sestupná hrana může být ztlumena zatížením spoje signálu rezistorem blízko zdroje signálu.

V návrzích desek s rychlými obvody je často používaná charakteristická impedance 50–80 Ω. Nižší hodnoty impedance způsobují přílišné dI/dt přeslechy a mohou zdvojnásobit spotřebu napájecí energie, což může způsobit problém s odvodem tepla. Vyšší hodnoty impedance mohou způsobit nejen silné přeslechy, ale také větší EMI citlivost obvodů a vyzařování.

Tabulka č. 2 ilustruje jaký vliv mají fyzikální vlastnosti na impedanci (Zo) přenosové linky.

Tabulka 2 Dopad fyzikálních vlastností na impedanci

Pole vycházející z povrchu konvenční jednostranné/dvoustranné desky se šíří nekontrolovatelně, protože nemá vazbu na zpětné vedení signálu např. referenční napájecí vrstvou desky. Pole mají spíše tendenci vybít se na vedlejších spojích, což způsobuje přeslechy. Některé z těchto polí zcela uniknou z povrchu desky a vyzáří ven.

Na druhé straně vícevrstvé desky mají rozvod napájecího napětí zabudovaný v podobě napájecích vrstev desky. Proud se tedy vrací ze signálních plošných spojů přes referenční vrstvu, která je v těsné blízkosti plošného spoje. Navíc použití napájecích vrstev zajišťuje nízkou impedanci napájecího rozvodu, která je nutností pro dobré blokování napájecího zdroje.

Vložení signálních plošných spojů mezi zemnicí a napájecí vrstvu zajišťuje stínění, které omezí vyzařování (až 45 dB) a náchylnost k vyzařování, stejně jako zajišťuje ochranu proti elektrostatickému výboji (ESD). Je dobrým zvykem routovat rychlé signály se strmou náběžnou hranou mezi napájecími vrstvami desky kvůli eliminaci vyzařování. Pokud je mezi napájecími vrstvami desky velká kapacita, potom se mohou obě napájecí vrstvy použít jako referenční.

Studie provedené firmou Hewlett-Packard ukázaly, že plošné spoje na okraji desky vyzařují až o 20 dB více v porovnání se spoji umístěnými uprostřed desky na vnějších vrstvách desky. Testy provedené na stejných plošných spojích umístěných uvnitř desky neukázaly žádné rozdíly s ohledem na umístění spojů blíže k okrajům desky.

V současné době jsou k dispozici různé programy pro výpočet impedance a rychlosti šíření pro danou šířku plošného spoje na každé vrstvě desky. Pro snížení přeslechů by měly být alternativní signální vrstvy navzájem pootočeny o 90 ° (např. vrstva 1 = horizontální, vrstva 3 = vertikální, vrstva 4 = horizontální atd.).

Hodinové obvody mají nejvyšší frekvenci překlápění ze všech obvodů a jsou primárním zdrojem šumu generovaným v číslicových obvodech.

Střída a strmost hran jsou kritické faktory, které ovlivňují výkon obvodu. Nejlepší je umístit zdroj hodinového signálu centrálně a pulzy rozvádět radiálně od středu. Pole vyzařované z proudu tekoucího směrem ven má tendenci se zrušit, což snižuje a synchronizuje zpoždění v přenosu signálu přes desku. Průběh signálu s 50% střídou a kontrolovanou náběžnou a sestupnou hranou rovněž pomůže snížit šum odstraněním sudých harmonických.

V systémech s rychlými obvody je doba hodinového cyklu obvykle kratší než je zpoždění přenosu signálu od jedné součástky ke druhé. Aby systém pracoval perfektně při vysokých rychlostech, je potřeba dobře nastavit časování šíření signálu, přičemž pro některé signály může být nezbytné upravit časové poměry s ohledem na vzájemné posunutí průběhů signálů. Zpoždění přenosu signálu lze odladit s pomocí software. K zabránění časovým diferencím na více připojených vstupech je potřeba mít spoje stejně dlouhé, což je možné provést manuálně položením spojů paprskovitě od zdroje signálu.

Aby se velikost desky mohla minimalizovat a snížila se doba potřebná k přenosu signálu, je deska osazena SMD součástkami tak hustě, jak je to jen možné. Výsledkem ovšem je, že plošné spoje musí být položeny blízko sebe, což způsobuje přeslechy. Přeslechy jsou důsledkem přenosu pulzu energie elektromagnetickým polem od zdrojového spoje k napadenému. Intenzita indukovaného signálu se zmenšuje s kratší délkou přiléhajících segmentů spojů, širší mezerou, nižší impedancí spoje a delší náběžnou hranou pulzu.

Při zvyšující se rychlosti hodin bývá nutné použít software pro analýzu elektromagnetického pole. S jeho pomocí lze získat přesnější odhad charakteristické impedance přenosové linky, přenosových rychlostí, přeslechů a návrh skladby vrstev desky. Výsledkem je rychlá a přesná charakteristika navrhovaných plošných spojů, která se za chodu dynamicky aktualizuje. Dielektrická konstanta materiálu FR4 kolísá až o 20 %.

Vzhledem k rozdílům v rozpětí napájecích napětích, v šumových a logických úrovních nelze kombinaci různých druhů číslicových obvodů doporučit. Zatímco napěťový rozkmit je např. u Schottky TTL 3 V, u ECL skupiny je šumová imunita pouze 100 mV DC. Použití těchto dvou druhů logických součástek by mohlo způsobit výrazné nežádoucí spřažení obvodů. U rychlých obvodů je spínací aktivita doprovázena rovnocennými rychlými požadavky na změny v odběru proudu z napájecího zdroje. Když několik součástek spíná ve stejný okamžik, musí být napájecí systém schopen dodat proud a udržet napájecí napětí v zadaném rozpětí. Tento problém zmenšují napájecí spoje s nízkou indukčností (jedna z mnoha výhod SMD součástek) a vysoká kapacita přes celou desku.

Blokovací kondenzátory dodávají proud součástce až do doby, než je toho schopen napájecí zdroj. Rychlé spínání způsobující široké spektrum proudových frekvencí vyžaduje několik nízko až vysokofrekvenčních kondenzátorů. Tento požadavek je zde proto, že jeden kondenzátor se nemůže postarat o tak široký rozsah frekvencí.

Kondenzátor by měl být umístěn co nejblíže k napájecím vývodům součástky. Aby se zmenšila indukčnost, měly by být pájecí plošky kondenzátoru připojeny k napájecím vývodům součástky spojem širokým nejméně 0,5 mm. K zabránění šumu by měl být spoj co nejkratší a neměl by být přímo napojený na napájecí vrstvu přes termální odlehčení.

Tantalové kondenzátory (např. 10 μF) by měly být rozestavěny rovnoměrně po celé desce, přibližně 1 na každých 6 integrovaných obvodů. Tyto tantalové kondenzátory dodávají proud pro nízkofrekvenční složku přechodné spínací spotřeby.

Když jsou na jedné desce použity analogové i digitální součástky, potom je obvykle nutné dělit napájecí plochu. Součástky by měly být rozděleny do skupin a rozmístěny takovým způsobem, aby žádné digitální signály nešly přes analogovou zemnicí plochu a žádné analogové signály přes digitální zem.

Dělené nebo izolované napájecí plochy mohou efektivně dostat proud spojený s určitým obvodem do specifické oblasti, kde může být blokován, nebo uzemněn. Dělené plochy omezí vysokofrekvenční proudy a jejich zpětné cesty tak, že se nemohou dostat na sousední nízkofrekvenční obvod, čímž se zabrání přeslechům.

Kvůli dodržení EMC pravidel vyžadují velké PQFP instalaci ve stíněném prostoru zařízení. Na druhé straně, ten samý čip umístěný v pouzdru PGA nebo BGA může dosáhnout shody s EMC. PGA a BGA pouzdra mají účinný chladič na horní straně pouzdra, který slouží nejenom k rozptýlení tepla, ale také jako EMI stínění.

Spoje by neměly mít pravoúhlé rohy. Se stoupající frekvencí a strmostí hran totiž pravoúhlé rohy zavádějí nadměrné kapacity a způsobují malé změny v charakteristické impedanci. To se stává přímo kritické při vyšších frekvencích např. 100 MHz, kdy elektrony z těchto spojů doslova vylétají. Lepším řešením je spoj pod úhlem 45 ° s krátkým segmentem, který je dvakrát delší než jeho šířka. Zaoblené rohy spojů (s vnitřním poloměrem alespoň rovným šířce spoje) jsou pak zdaleka nejlepším řešením pro rychlé signály.

Zvyšující se rychlost obvodů a hustota na desce nutí návrháře více se věnovat problémům spojeným s efektem přenosové linky. Aby bylo možné přesněji předpovědět potenciální problematickou část desky, minimalizovat elektromagnetickou interferenci a citlivost a ověřit návrh desky, musí návrháři nejenom plánovat s ohledem na EMC, ale musí také používat software pro analýzy navržené desky. Jakmile rychlost hodin dosáhne 50 MHz, měla by se brát v úvahu také problematika signal integrity přenosu signálu plošným spojem.

O autorovi:

Barry Olney je ředitelem firmy In-Circuit Design Pty Ltd. (Melbourne, Victoria, Australia), VeriBest Solutions Centre a CAD Services Bureau. In-Circuit Design se specializuje na návrh DPS s rychlými digitálními obvody a je držitelem Engineering Excellence Award for the MxP Sparc 20 od Institute of Engineers, Australia. Barry rovněž přednáší na Advanced Design for Surface Mount Technology při Australian Electronics Development Centre.

This article is used by permission of Barry Olney, In-Circuit Design Pty Ltd (www.icd.com.au)