V minulých číslech tohoto časopisu jsme stručně uvedli novou generaci ATE – automatického testovacího systému pro osazené desky plošných spojů. Systém byl vyvinut ve firmě Ryston Electronics pro vlastní výrobní testy, ale po uplatnění v sériové výrobě byl dopracován do stadia produktu. Má jednoduchý základ, avšak je flexibilní a rozšiřitelný pro další aplikace.

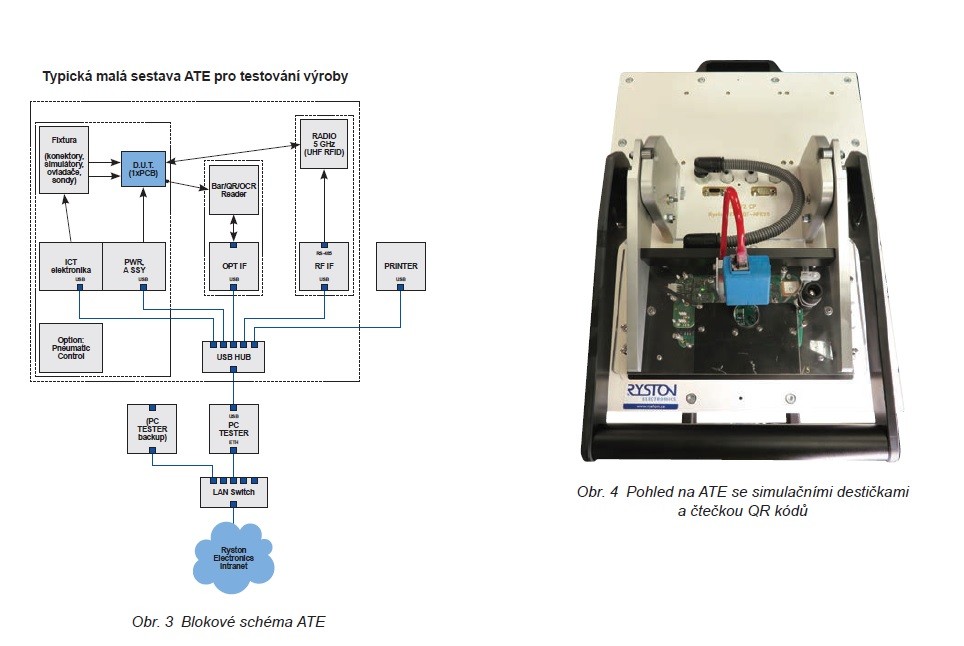

Elektronickou část testeru jsme předělali na „stavebnici“ modulů s analogovými/výkonovými a digitálními testovacími funkcemi a s ovládacími prvky např. pro solenoidy. Celý systém sice může pracovat samostatně, ale lze ho přes USB připojit k běžnému PC. To umožňuje samočinnou elektronickou evidenci kusů, které prošly daným krokem procesu, do databázového souboru či po síti do firemního systému řízení jakosti.

Při výrobě menších sérií jsme se však nemohli vyhnout kompromisům při zajišťování materiálu, hlavně integrovaných obvodů, které se blíží konci dostupnosti u distribuce (neblahé zkratky EOL – End-of-Life, NRND – Not Recommended for New Designs, LTB – Last Time Buy).

V řadě našich výrobních zakázek se jedná o malé počty desek, stovky i desítky, ale závisí na nich zákazník. Buď se v nejisté době musíme předzásobit riskantními součástkami s vysokou cenou, nebo riskovat nákup „z volného trhu“, kdy se může jednat o mimotoleranční, nebo rovnou padělané součástky.

Proto jsme sáhli k netradičnímu využití automatického testeru pro vstupní kontrolu součástek. Snažíme se vystavit testované prvky takovému tepelnému, časovacímu a funkčnímu stresu, který je co nejblíže pracovnímu zatížení, nebo i za jeho hranicí, abychom eliminovali „nahnilé“ kusy.

Nejjednodušší je použít funkční vzorek desky plošného spoje a upnout ji do ATE fixtury vyvinuté pro zapájené desky, ale u kritické součástky použít ZIF objímku (ZIF – Zero Insertion Force, nulová zasouvací síla). Pokud na to při návrhu DPS myslíte a máte-li štěstí, lze objímku zapájet přímo do DPS. Častěji je nutno použít ještě redukci pro vývody anebo pečlivě připájet drátky od vývodů na plošky. Čím kratší, tím lepší a je nutno myslet na případné opravy. ZIF objímka je největší cenovou položkou, stojí řádově stokrát víc než ta normální a někdy je nutno ještě použít mezikus, např. patro DPS s blokovacími kondenzátory na všechna napájení. Vzorky se dají pořídit za přijatelnou cenu.

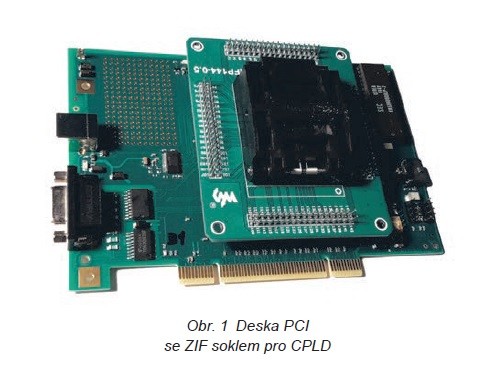

Příklad z praxe: v jednom výrobním projektu, desce do sběrnice PCI, již několik let používáme obvod CPLD se 144 vývody, jejichž výrobce byl koupen jinou firmou, a tyto obvody se staly zastaralými jednak kvůli napájecím hladinám, jednak proto, že nová firma nechce konkurenci k novým typům.

Můžete se buď předzásobit, ale u dvacetidolarových součástek to moc nejde. Nebo se dohodnete se zákazníkem, který zváží náklady na převyvinutí desky, ale za čas se opět ocitne v této situaci, anebo zkusíte volný trh. Cena hovoří jasně, ale nám se nechtělo nacházet vadné obvody až po osazení a zapájení, provádět rework desky a použít nové obvody ze stejného zdroje.

Napadlo nás použít originální design, již hotovou fixturu, poučit se a navrhnout speciální DPS jako adaptér. Ten poskytl základ pro dvě ZIF objímky pro kritické součástky: CPLD a CMOS RAM. Jednoduchá elektronika (řada nulových odporů jako rozpojovací body) umožnila měřit např. spotřebu součástek v různých režimech anebo zatížit kritické signály (časování) parazitními kapacitami pro vložení zpoždění. Stejná deska později umožnila vyzkoušet nový typ CPLD s jinými napájecími hladinami.

Při testování rozhraní sběrnice PCI jsme postupovali ve třech krocích. Nejprve „statický“ test odběru z napájení, který eliminuje zkraty. Programovatelné zdroje v ATE umožňují vystavit součástky napájení v doporučeném rozsahu a mají proudovou ochranu.

Druhý krok je „pomalý“ test integrity signálů sběrnice, tedy propojení zhruba půlky vývodů CPLD pomocí JTAG rozhraní se sběrnicí, která má rovněž signály JTAG. Druhá půlka vývodů je na desce propojena s vnitřní sběrnicí rozvedenou do obvodů uvnitř desky, např. pamětí a portů. Do konektorů desky je možno zapojit testovací protikusy, např. LED nebo propojení výstupy-vstupy.

JTAG v testovacím módu promění „hranice“ (Boundary), tedy vývody všech součástek zapojených v JTAG řetězci, v jeden dlouhý posuvný registr, který je možno v případě výstupů „nabít“ (povelem Preload) konfiguračními a úrovňovými daty a „vzorkovat“ (povelem Sample), vyčíst stav jejich vstupů. Také umí dalšími povely vyčíst některé vnitřní registry součástek, např. identifikaci. Zkušenost: V projektu vývoje ISDN ústředny jsme naletěli: použili jsme „fake“ obvody starší verze označené jako nová verze, což po měsících útrap bylo zjištěno právě JTAG testem.

Sekvence výstupních bitů a očekávaných vstupních bitů do/z posuvného registru se nazývá vektor a posloupnost vektorů tvoří test. Pokud deska projde testem napájení a „pomalým“ testem, je velká šance, že nezničí zdroj či matkodesku počítače v dalším kroku.

Aby test netrval příliš dlouho, je JTAGem otestováno jen propojení se sběrnicí počítače a provedeno několik vektorů, které otestují vnitřní signály proti vzájemným zkratům a přerušení. Testuje se metodou „putující jednička a nula“, tedy mezi samými nulami do výstupů se z jednoho vyšle jednička a ověří se, že došla všude, kam měla, atd.

Třetí krok: v počítači s reálnou sběrnicí PCI je proveden „rychlý“ test vnitřního propojení desky dynamicky, přiměřeným testem bloků paměti a periferií. Tak bylo mimochodem odhaleno několik záludných chyb ručního osazení: nesprávně umístěných blokovacích kondenzátorů mezi daty a adresami.

Obvod CPLD tak dostal pořádný nápor dynamické zátěže pomocí sběrnicových operací (šíře 32 bitů, 33 MHz), stejně jako vnitřní sekvenční automat – řadič sběrnice a kontrolér parity. Přitom jsme na vzorku několika desítek kusů měřili infra- -teploměrem oteplení pouzdra obvodu v objímce a porovnali ho se zaručeně originálními součástkami. Potom jsme celé zkušební PC umístili do teplotní komory a zatopili na horní hranici průmyslového teplotního rozsahu a nechali cyklovat. Když začaly kolabovat jiné obvody PC, usoudili jsme, že to stačí.

Výsledek byl příznivý. Kromě několika deformovaných vývodů obvodů CPLD nedošlo v žádném kroku k selhání součástky. Lehká deformace se vysvětlila nesprávným zabalením součástek do trayů – plat, která měla být přepáskována, ale byla jen stažena gumičkami. Vývody (v rastru 0,5 mm) stačilo jemně srovnat. Zkušební dávka ostrých desek byla poslána na normální zapájení se zbytkem ostatních součástek. Potěšilo zjištění, že všechny součástky byly zapájeny správně. Jedině se nám moc nelíbil vzhled pájených spojů, které vypadaly poněkud studeně. Ale tak je tomu u bezolovnatého pájení pravidelně.

Všechny desky pak prošly funkčním zátěžovým testem trvajícím několik dní: zahořováním „Burn-In“ a výstupní kontrolou. Po úspěšné kontrole byly desky expedovány. Zdá se, že jsme měli štěstí.

Co kdyby se ale projevily nějaké chyby, statisticky nebo soustavně? Celou dávku bychom stáhli a provedli další testy, aby vyšla najevo příčina. Ale vše by se zpozdilo.

Proto jsme se zásobili i originálními obvody z posledního nákupu, osadili desky a jejich zásobu držíme v pohotovosti. Něco to stálo, ale zato jsme schopni pokrýt i nečekané požadavky zákazníka. Ten byl zainteresován na dlouhodobém plánování dodávek, jsme s ním v neustálém kontaktu a monitorujeme jeho spokojenost. Něco nového jsme se naučili i pro další vývojové zakázky: navrhovat DPS tak, aby byly nejen testovatelné, ale aby šly použít jako platforma pro nové testy. Je to skoro zadarmo.

Základní deska testeru je připojená přes USB Hub k počítači a obsahuje osvědčenou směs digitálního testovacího rozhraní JTAG, analogových vstupů a výstupů a výkonových obvodů, které mohou pracovat jako zkušební zdroje nebo zátěže. V případě potřeby je možné přes USB Hub expandovat další desku, a tím zvětšit počet připojitelných bodů.

V našem popsaném případě jsme ještě přidali testovací obvody pro zálohovací baterii, která je častou příčinou oprav.

Pokud nestačí mix testovacích rozhraní nabízený základní deskou ATE systému, je možno doplnit je např. o vnější měřicí ústřednu ze sortimentu firmy HP/Agilent/Keysight HP34900. To je pouzdro na volitelné moduly analogových testovacích obvodů, selektorů signálů, radiofrekvenční spínače atd. Je to velmi kvalitní programovatelný systém, ale ne zrovna levný. Programuje se po sběrnici HP-IB (IEEE-488) nebo po sériové lince (přes USB-RS232 konvertor v řídicím PC).

Díky vestavěnému mini PC lze využít všechny výhody OS Windows, ovladače a síťový software, případně i grafické výstupy CAD softwaru pro lokalizaci vadné součástky či spoje (pin-pairu) na desce.

Automatický testovací systém (ATE) vyvinutý ve firmě Ryston Electronics je velmi flexibilní. Umožňuje pomocí jednou vytvořené fixtury s jehlovým polem testování jak zapájených desek, tak i vstupní testy součástek pomocí ZIF objímek. Součástky je možno vkládat a vyjímat šetrně a ještě před jejich zapájením může být provedena řada testů pro jejich schválení, máte-li nejistotu o jejich kvalitě.

ATE podporuje spolupráci v podnikové síti kvality, připojení externích jednotek jako měřicí ústředna nebo mechanická či pneumatická zařízení, antény, kamery či čtečky. Při vývoji byly rozvedeny poznatky z vývoje testovacích přípravků pro oživování a malé série.

[1] Firemní literatura na www.ryston.cz