Zkratka DfT znamená Design for Testability, návrh pro testovatelnost výrobku. Začala se používat u výrobců VLSI integrovaných obvodů, jejichž složitost a jemnost struktury již vyloučila možnost testování systémů uvnitř čipů nanosondami, a tvůrcům zbyly pro připojení jen okrajové plošky a vývody. Vzniklo tak umění přidat testovací obvod, který umožní přepnout čip do testovacího módu, a původně vnitřní signál, jehož stav je citlivý případné chyby návrhu nebo technologie, vyvést na testovací plošku nebo na vývod.

Toto pojetí bylo zobecněno pro testování osazených desek plošných spojů. Aby bylo možné zajistit dostatečnou kvalitu výrobků, je třeba během výrobních procesů výrobky testovat.

Cílem výrobců elektronických zařízení je dosáhnout nejvyššího zisku při vydání nejnižších nákladů na výrobu, včetně testování. Na druhou stranu, testování snižuje náklady na pozdější opravy nebo reklamace. Zákazník vždy požaduje všechny výrobky bez vad. Vhodný testovací postup, který odhalí většinu chyb daného kroku co nejdříve, je vždy kompromisem, i podle počtu kusů, které se mají vyrobit.

Teoretickým ideálem je test úplný, což u číslicových obvodů znamená, že konečnou kombinací či sekvencí vstupních signálů, či u analogových obvodů, že existuje takový (spojitý) signál na vstupu, který umožní detekovat na dostupných výstupech odlišné chování při chybě v kterémkoli místě vnitřní struktury (vnitřních signálů). Chybou se rozumí: rozpojení signálu, zkrat dvou signálů navzájem nebo zkrat signálu na napájení anebo u analogových signálů významná změna charakteristické vlastnosti součástky či svod (je nutno definovat toleranci a významnost). Jako vše ideální to často není dosažitelné, protože by test trval příliš dlouho.

Nemá smysl zabývat se přílišnou teorií (citlivostní analýza, řiditelnost atd.). Na praktické testování osazených desek plošných spojů ve výrobě je kladena řada mnohdy protichůdných požadavků (časových, funkčních, ekonomických a návrhových), a proto se používá řada metod, přípravků a zařízení, které testování zefektivní a poskytne kompromisní výsledky.

Mezi preferované metody testování patří především:

Optická inspekce je proces, kdy se „pohledem“ kontroluje kvalita pájených spojů, správná poloha a osazení součástek. Optickou inspekci lze provádět pouhým okem (prototypy a kusová výroba) nebo pomocí automatů, které obsahují pohyblivé kamery, jimiž je snímána osazená DPS. Automat je „naučen“ na vzhled správně a nesprávně osazené či zapájené součástky a je schopen rozpoznat vady pájeného spoje, chybějící součástky, zkraty a další vady, které zobrazí obsluze, a ta prověří, zda se jedná skutečně o vadu osazené desky.

Obr. 1 Příklad špatně zapájené součástky (tombstoning)

Optická kontrola však vyžaduje dobrou přístupnost testovaných míst pro pohled, a tedy vzniká požadavek při návrhu vhodně rozmísťovat součástky s velkými rozestupy. Vzdálenost součástek od sebe je jedním z volitelných návrhových pravidel, které lze při návrhu zkontrolovat. Další možností pro zachycení defektu je pohled nejen shora, ale i ze šikma nebo endoskopicky z boku pod pouzdro součástky.

Poddruhem optické kontroly je rentgenová defektoskopie (RTGI), která je však kvůli vysoké ceně výsadou větších osazoven. Umožňuje zobrazit zejména kvalitu pájení součástek v pouzdru BGA ve spojení s počítačovou analýzou obrazu.

Touto metodou je testována většina levných výrobků nebo je funkční test použit při závěrečné kontrole. Výrobek se testuje jako celek bez kontroly vnitřních signálů. Tester na vstupy přivádí pomocí speciálních propojovacích kabelů budicí signály a kontroluje odezvu na výstupech výrobku. Pokud zařízení obsahuje programovatelné prvky, obvykle se do nich nahrává tzv. testovací firmware, který umožňuje snazší detekci chyb. Testování tímto způsobem obvykle vyžaduje interakci operátora. U kvalitnějších testerů jsou operátoři nahrazeni pomocí robotů a jednoúčelových automatů. Tyto automaty kontrolují mechanické díly a signalizační komponenty (LED indikátory, displeje, akustickou signalizaci, tlačítka atd.).

Obr. 2 Nesprávná poloha součástek, často způsobená osazovací hlavou nebo vibracemi

Funkční testování je vhodné zejména pro kusovou výrobu a malé série, protože výsledná cena testeru pro funkční testování je nízká. Je však třeba zvážit vyvedení důležitých signálů na konektor. Kompromisy nastávají při simulaci elektromechanických prvků, kontrole displejů kamerou atd.

Testy v přípravcích (In-Circuit Testing, ICT) jsou poměrně rozšířenou metodou při výrobním testování elektronických zařízení po osazení plošného spoje. Testování ICT spočívá v měření signálů přímo na DPS, kdy se pro systém generují budicí signály a kontroluje se, zda je reakce obvodu správná. Testovací signály jsou k měřenému výrobku připojovány pomocí testovacích jehlových kontaktů. Jehly v pouzdrech tvoří jehlové pole, které je součástí testovací fixtury – přesného držáku na desku, často s víkem. Každá deska plošných spojů, která je testovatelná touto metodou, musí tedy obsahovat tzv. „testpointy“, testovací plošky nebo body, obvykle na spodní straně.

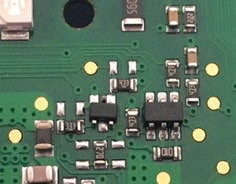

Obr. 3 Testovací plošky na desce

Z výše uvedeného je tedy jasné, že na tento typ testování je výrobek třeba připravit již během vývoje DPS. Deska musí být připravena tak, aby každý testovací bod na desce bylo možné spolehlivě a opakovatelně připojit na testovací jehly a aby bylo opravdu možné vygenerovat budicí signály a změřit výsledné signály a jejich průběhy. Obvykle je umístění zajištěno přesnými naváděcími trny a přítlačnými sloupky ve víku fixtury. Deska pro ICT testování musí již návrhem umožňovat připojení přítlakových bodů a naváděcích trnů pro jednoduché vkládání výrobku do fixtury.

Obr. 4 Fixtura pro ICT systém: vespod testovací jehly, shora přítlačné sloupky a držák SIM karty

HW návrh testovacích bodů na desce musí splňovat kromě základních pravidel pro návrh DPS i technologické požadavky na jeho výrobu, osazení a pájení.

Samotná testovací jehla je přesným výrobkem, který provádí pružný kontakt na desku. Její vršek má ostré hranky nebo hrot(y), které mají rozrušit povrchovou vrstvičku nečistot na pájeném spoji a zajistit malý přechodový odpor podle proudu, který jí při testu teče. Tomu má odpovídat i velikost a povrchová úprava testovací plošky na DPS. Při velkém počtu testovacích bodů je plocha jimi zabraná velká a velká musí být i přítlačná síla, což zase může ovlivnit rozmístění součástek. Pouzdro jehly zasazené do nosné desky umožňuje její výměnu při opotřebení nebo zlomení. K propojovacím drátům do elektroniky se připojuje většinou ovíjením.

Samostatnou kapitolou je, jak vytvořit kombinaci nebo sekvenci testovacích signálů pro určitou desku. Samotný počet test-pointů není zárukou úspěšného testu. Obvykle se vytvoří sada nezávislých (ortogonálních) budicích signálů, což může být „putující jednička“ nebo injekce zvlnění do analogové sítě, a test, zda tento signál dojde právě tam, kam má, popř. ve správné úrovni.

Je třeba se zmínit o rozhraní JTAG, které nabízí snížení počtu HW testovacích bodů a umožňuje otestování obvodů, které tuto technologii podporují. Používá se jak při funkčním testování pro programování součástek, tak v automatickém režimu pro programování i testování. Pro testování osazených DPS (pro test integrity propojení mezi vývody obvodů) se JTAG používá přesně naopak než při testování vnitřků čipů: V testovacím módu se obvody podporující JTAG změní v dlouhý posuvný registr, do/z nějž je možné zapsat a přečíst obsah pomocí příkazů. Jiné příkazy slouží pro vyčtení signatur obvodů, takže je možno se přesvědčit o správnosti zapájených součástek. Systém JTAG vyžaduje vyvést na konektor nebo alespoň na testovací plošky svoje signály a napájení.

Tento systém dokáže v přímém módu najít na osazené desce následující chyby:

Přímý mód JTAG umožňuje otestovat části desky tvořené nejčastěji hustě montovanými BGA digitálními součástkami s mnohavodičovým propojením (např. 32bitovou sběrnicí), které prakticky nelze testovat jinak.

Každý krok testu je popsán „vektorem“, tedy posloupností nul a jedniček, které popisují nastavení výstupů a očekávané úrovně na vstupech. Vektor se nasune do posuvného registru tvořeného „hraniční oblastí“ součástek s JTAGem, vyšle se paralelně na výstupy a porovná se očekávaný stav vstupů se skutečností. JTAG test je posloupnost vektorů, která se vygeneruje na základě předem známých souborů popisujících součástky (BSDL soubory od výrobce) a seznam spojů (net-list) desky plošného spoje. To může proběhnout automaticky generátorem test-vektorů.

V nepřímém módu lze otestovat další část součástek na desce a jejich zapojení, které jsou připojeny k JTAG vývodům součástek, například D/A převodníky nebo komunikační rozhraní, ale pro to je nutno k testovacím bodům nebo konektorům připojit testovací adaptéry. Pro nepřímý test se tedy musejí vytvořit další vektory, ale ty už není možno generovat automaticky, ale na základě znalosti propojení obvodů mimo JTAG oblast a jejich fyzikální funkce.

JTAG není schopen otestovat např. oscilátory nebo jiné nezávislé obvody, zde je nutno je zkontrolovat osciloskopem, nejlépe s nastavenými žádoucími hodnotami impulsů. Bohužel každý z výrobců programovatelných součástek si nadefinoval svůj konektor JTAG, takže se nevyhnete úpravě jejich programátorů nebo programovacích kabelů ve smíšených systémech.

Automatický testovací systém (ATE) vyvinutý ve firmě Ryston Electronics využívá naše zkušenosti s testováním smíšených DPS a je velmi flexibilní. Umožňuje pomocí fixtury s jehlovým polem testování jak zapájených desek, tak i součástek, detailní i funkční testy a disponuje i adaptéry pro elektromechanické, pneumatické a výkonové obvody. Využívá systém JTAG v přímém i nepřímém módu a k tomu „stavebnici“ analogových, napájecích a zátěžových modulů pro nepřímé testy.

Díky vestavěnému mini PC lze využít všechny výhody OS Windows, jako jsou ovladače a síťový software, případně i grafické výstupy CAD softwaru, pro lokalizaci vadné součástky či spoje (pin-pairu) na desce.

ATE podporuje spolupráci v podnikové síti kvality díky připojení k síti, připojení externích jednotek jako měřicí ústředna nebo mechanická či pneumatická zařízení, antény, kamery či čtečky. Při vývoji byly rozvedeny poznatky z vývoje testovacích přípravků pro oživování a malé série a funkčních testerů.

Základní deska testeru je připojená přes USB k počítači a obsahuje osvědčenou směs digitálního testovacího rozhraní JTAG, analogových vstupů a výstupů a výkonových obvodů, které mohou pracovat jako zkušební zdroje nebo zátěže. V případě potřeby je možné přes USB Hub expandovat další desky, a tím zvětšovat počet připojitelných bodů.

V našem případě jsme ještě přidali testovací obvody pro zálohovací baterii, která je častou příčinou oprav.

Pokud nestačí mix testovacích rozhraní nabízený základní deskami ATE systému, lze je doplnit např. o vnější měřicí ústřednu ze sortimentu firmy Keysight HP34900. To je pouzdro na volitelné moduly analogových testovacích obvodů, selektorů signálů, radiofrekvenční spínače atd. Je to velmi kvalitní programovatelný systém, ale ne zrovna levný. Programuje se po sběrnici HP-IB (IEEE-488) nebo po sériové lince (přes USB-RS232 konvertor v řídicím PC).

Správný návrh DPS pro testování je založen na zkušenostech a znalosti testovacích technik. Jde ruku v ruce s návrhovými pravidly pro funkčnost a nízké EM emise a též pro technologii výroby a osazení DPS.

Volba způsobu testování je velkým kompromisem závisejícím na vyráběném počtu desek, vnitřním zapojení, signálech a časových požadavcích. Pokud je deska navržena podle dobře vybraných pravidel, může být výrobě užitečný automatický testovací systém vyvinutý Rystonem.

foto: Roman Blahout

Odkazy: [1] Firemní literatura na www.ryston.cz

[2] technobyte.org/what-is-dft-design-for-testability-introduction/

[3] en.wikipedia.org/wiki/Nanoprobing

[4] cs.wikipedia.org/wiki/Joint_Test_Action_Group

[5] Automatický testovací systém. DPS 2019/2