Tato kapitola představuje souhrn základních principů vývoje aplikací pro programovatelná hradlová pole. Vše je podáno v obecné rovině, aby pro pochopení nebyla nutná znalost konkrétních technologií nebo HDL jazyků. Pokud bude v textu použit úryvek z HDL, bude se vždy jednat o jednoduchý výraz pochopitelný každému, kdo se někdy setkal s libovolným počítačovým jazykem. Samozřejmě pro vlastní implementaci popsaných základů bude nutné nastudovat další literaturu a dokumentaci, která bude souhrnně uvedena v závěru seriálu.

Vývoj pro FPGA je v mnoha ohledech podobný vývoji zákaznických číslicových integrovaných obvodů, ale umožňuje ve vývojovém cyklu využít mnoha zjednodušení. Pro úspěšný vývoj aplikací pro FPGA je dobré dodržovat několik zásad:

Jednotlivé body jsou vysvětleny dále. Jejich dodržování sice nezaručí stoprocentně úspěšný návrh, ale pomůže vyhnout se mnoha typickým problémům a vývojářským chybám.

Přestože strukturou a syntaxí se HDL jazyky, jako je třeba Verilog nebo VHDL, podobají programovacím jazykům, je třeba mít neustále na paměti, že se jedná o popis číslicových obvodů. Na rozdíl od běžných programovacích jazyků, které – zjednodušeně řečeno – popisují sekvenci postupně vykonávaných příkazů, HDL definují strukturu logického obvodu. Takto definovaný obvod nevykonává žádnou posloupnost činností, ale pracuje neustále paralelně. Každá jeho součást popsaná jednotlivou konstrukcí v HDL vykonává svou funkci po celou dobu, kdy je obvod napájen.

Přestože se tento bod zdá být samozřejmý, mnoho vývojářů, kteří znají běžné programovací jazyky, v něm při přechodu na FPGA chybuje. Zlom nastane ve chvíli, kdy si uvědomí rozdíl mezi programovacím jazykem a HDL.

Jak bylo popsáno dříve, dnešní FPGA obsahují kromě bloků obecné logiky i mnoho specializovaných funkčních bloků. Pro efektivní implementaci výsledné aplikace je důležité znát strukturu cílového obvodu včetně speciálních bloků. Vlastní návrh je vhodné uzpůsobit tak, aby využíval maximum prostředků poskytovaných programovatelným obvodem.

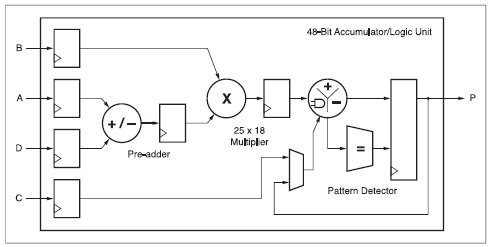

Obr. 1 Blok DSP48E1 v obvodech řady 7 firmy Xilinx

Jako typický příklad je možné uvést například aritmetiku v pevné řádové čárce. Snad všechny dnešní FPGA obsahují bloky DSP, které se skládají z rychlé násobičky, akumulátoru, několika multiplexerů a logiky rychlého přenosu. Pokud uživatelský návrh aritmetické funkce využije blok DSP, bude výsledná implementace velmi rychlá a nebude zbytečně obsazovat bloky obecné logiky, které mohou být využity pro další funkce. Pokud bude široká násobička v uživatelské aplikaci vytvořena z bloků obecné logiky, bude pomalejší a zabere velké množství logických bloků. Pro ilustraci je na obrázku 1 zjednodušené schéma bloku DSP48E1 převzaté ze „7 Series DSP48E1 Slice User Guide“ firmy Xilinx.

Využití speciálních bloků v návrhu je možné dvěma způsoby. Buď vložením instance daného bloku do návrhu z knihovny dodané výrobcem obvodu, nebo správným vysokoúrovňovým popisem funkce daného bloku. Pro výše uvedený příklad násobičky pak může její vysokoúrovňový popis vypadat takto jednoduše:

result <= a * b;

Pokud budou vstupní signály a a b a výstup result definovány shodně jako znaménkové nebo bezznaménkové vektory, šířka vektoru result bude rovna součtu šířek vektorů a a b, využije implementační nástroj pro implementaci násobičky blok DSP.

Další důležitou vlastností programovatelných logických obvodů, kterou je třeba během návrhu vzít v úvahu, je určení jednotlivých pinů. Přestože je struktura většiny vstupně-výstupních buněk FPGA shodná nebo velmi podobná, ne všechny piny jsou navzájem záměnné. Některé vstupně-výstupní piny podporují pouze některé vstupní nebo výstupní standardy a napěťové úrovně, některé piny jsou vhodné pro vstup hodinových signálů, některé dvojice pinů tvoří diferenciální páry, některé piny mohou být použity pro vstup nebo výstup rychlých sériových dat nebo třeba připojení pamětí DDR. Vstupně- výstupní piny jsou obvykle rozděleny do takzvaných bank, které například sdílejí napájecí a referenční napětí. Před návrhem schématu zapojení desky s FPGA je vždy vhodné zkontrolovat zapojení pinů podle dokumentace k programovatelnému obvodu a nejlépe i připravit základní návrh pro FPGA s přiřazenými piny. Implementace takového návrhu pak odhalí případné problémy a je možné schéma zapojení změnit.

Jednotlivé prostředky dostupné v obvodech FPGA je možné rozdělit na lokální a globální. V tomto kontextu se jedná především o dostupné propojovací prostředky. Programovatelná hradlová pole obsahují obvykle tři rozdílné typy propojovacích prostředků:

Krátké rychlé spoje s omezeným dosahem mohou propojit například pouze sousední funkční bloky. Příkladem takových spojů je například vertikální propojení logických buněk sloužící k rychlému šíření přenosu.

Globální rychlé spoje se používají pro společné signály, které jsou potřebné téměř po celé ploše čipu s co nejmenším zpožděním a především s co nejnižším rozptylem hodnot zpoždění. Tyto spoje se používají hlavně pro globální hodinové signály nebo třeba globální set/reset. Množství těchto spojů na čipu je omezené. Některé „globální“ spoje jsou ve skutečnosti omezeny do takzvaných regionů, například pouze na polovinu nebo čtvrtinu plochy FPGA.

Běžných spojů je na ploše čipu nejvíce. Slouží pro propojení jednotlivých funkčních bloků. Rychlost šíření signálu těmito spoji je obvykle nižší než u předchozích dvou skupin a koherence jednotlivých zpoždění ve skupině podobných signálů je nižší.

Pro efektivní návrh je důležité správně využívat vhodné propojovací prostředky. Globální hodinové signály a další důležité globální signály by měly vždy využívat odpovídající globální spoje. Lokální hodiny a jiné rychlé signály s lokální působností by měly využívat různé specializované lokální propoje. Pouze obecná logika by měla být propojena pomocí běžných spojů. Důležité je dobře si rozmyslet například nutnost použití globálních resetů. Na rozdíl od ASIC je možné ve většině FPGA definovat počáteční stavy registrů a globální reset pak často není nutný. V některých částech obvodu pak jeho funkci zastane lokálně generovaný reset pro tuto konkrétní část obvodu, zatímco většina obvodu může v FPGA často správně fungovat kompletně bez resetu.

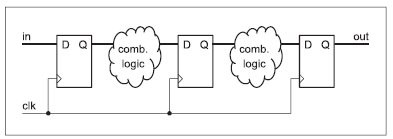

Až na některé výjimky jsou FPGA navržena pro efektivní implementaci plně synchronního návrhu. To znamená, že samotný návrh aplikace by měl dodržovat pravidla synchronního návrhu. Popis synchronního obvodu ve formě signálových toků pomocí střídajících se úrovní kombinační logiky a registrů se nazývá „register-transfer level“ – RTL. Tento princip je zjednodušeně znázorněn na obrázku 2.

Obr. 2 Synchronní popis obvodu

Kombinační logické funkce na obrázku 2 jsou proloženy registry, které pracují na společném hodinovém signálu. Takováto struktura odpovídá struktuře logických elementů FPGA, kde je vždy LUT následována registrem. Implementace takto strukturovaného obvodu v FPGA vede k nejlepším výsledkům.

Pro správný synchronní návrh je velmi důležité dodržet několik bodů:

Redukce počtu hodinových domén může být někdy dosaženo například použitím jednoho společného hodinového signálu s nejvyšší společnou frekvencí a vygenerováním povolovacích signálů (clockenable) pro jednotlivé domény obvodu. Problematika hodinových domén a použití asynchronních signálů je natolik široká, že jí bude věnována samostatná kapitola.

Před vlastní implementací popisu obvodu je důležité ověřit jeho funkci. V případě synchronního návrhu pro FPGA stačí pro ověření správné funkce návrhu jeho verifikace pomocí funkční simulace. Simulace by měla ideálně pokrýt veškeré možné stavy celého obvodu a veškeré možné kombinace vstupů a vnitřních stavů včetně chybných a nepředpokládaných možností.

Oblast číslicových simulací a verifikace obecně je velice rozsáhlá a přesahuje rámec tohoto seriálu. Touto problematikou se detailně zabývá velké množství literatury, která bude uvedena v závěru seriálu.

Funkční simulace sama o sobě nezaručuje správnou funkčnost výsledného obvodu po implementaci. Na rozdíl od plně zakázkového návrhu ASIC je však situace ve světě FPGA mnohem jednodušší. Celý návrh je implementován pomocí pevně daných obvodových struktur, které byly plně charakterizovány. Pro ověření správnosti implementace a správné funkce výsledného obvodu proto stačí kromě funkční simulace pouze nadefinovat všechny časové vlastnosti obvodu, tzv. „timing constraints“, a provést statickou časovou analýzu (STA). Kroky jako extrakce parametrů z implementace a post-implementační simulace známé z ASIC nejsou v případě návrhů pro FPGA nutné.

Před spuštěním syntézy a implementace návrhu je nutné mít nadefinovány všechny časové poměry v obvodu – timing constraints. Současné implementační nástroje tyto parametry nepoužívají pouze pro statickou časovou analýzu, ale i pro vlastní syntézu a implementaci. Timing constraints musí být úplné a musí definovat:

Splněním všech těchto bodů jsou veškeré časové poměry v návrhu známy a STA může provést kompletní kontrolu všech hodinových a signálových cest v implementovaném obvodu a nahlásit případné problémy, jako je překročení maximální možné frekvence, porušení setup a hold časů synchronních prvků a podobně. Časové parametry jednotlivých prvků FPGA i spojů mezi nimi jsou známy z tovární charakterizace obvodu a výsledku implementace. Dalším výsledkem STA bývá často odhad maximální možné frekvence jednotlivých hodinových signálů.