V případě spínaných napájecích zdrojů (switch‑mode power supplies – SMPS), je správný návrh desky plošných spojů kritický, ale velmi často podceňovaný krok k dosažení dobrého výkonu a spolehlivosti. Chyby v návrhu desky způsobují různé problémy, které zahrnují špatnou regulaci napětí, zakmitávání při spínání, či dokonce selhání napájecího zdroje. Těmto problémům by se mělo předejít za každou cenu, protože jejich odstranění obvykle vyžaduje předělání návrhu desky. Na druhé straně lze těmto problémům předejít, pokud jsou odhaleny včas a návrhu desky se věnuje náležitá pozornost. Tento článek popisuje pět základních kroků, které mohou zajistit, že váš návrh desky pro snižující (step‑down) napájecí zdroj bude správný a použitelný.

Když se navrhuje server, tablet nebo elektronická pokladna, je nejlepším a nejméně riskantním způsobem okopírování volně dostupného návrhu desky v podobě ukázkového modulu, jak je ukázáno v katalogovém listu. To však není z nejrůznějších důvodů vždy možné. Tento článek byl napsán právě pro tyto případy a ukazuje detailně postup správného návrhu desky pro jakýkoliv snižující spínaný zdroj založený na obvodu TPS62xxx.

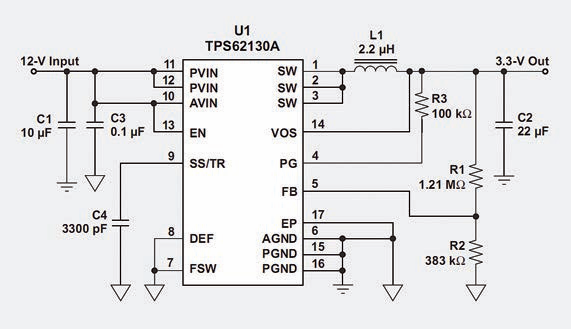

Vnitřní MOSFETy a integrovaný obvod kompenzační smyčky zjednodušují návrh desky. Univerzální TPS62130A je použit jako příklad snižujícího konvertoru, který může být použit v každé aplikaci. Obr. 1 ukazuje kompletní schematické zapojení typického obvodu napájecího zdroje.

Obr. 1 TPS62130A je použit ve snižujícím napájecím zdroji 12–3,3 V

Vstupní kondenzátor (C1) je nejdůležitější samostatnou součástkou pro spolehlivou funkci jakéhokoliv snižujícího konvertoru. Proto by měl být umístěn na desku jako první hned po hlavním integrovaném obvodu (U1). Hned po jeho položení na desku ho propojte plošnými spoji s IO (U1), aby v cestě jeho spojů nic nestálo. Extra parazitická indukčnost mezi oběma vývody kondenzátoru a vývody IO (U1) PVIN a PGND vytváří napěťové špičky v důsledku spínání o velikosti V = L × dI/dt. To může způsobit selhání IO.

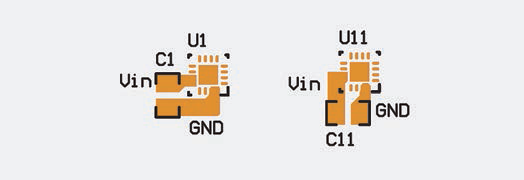

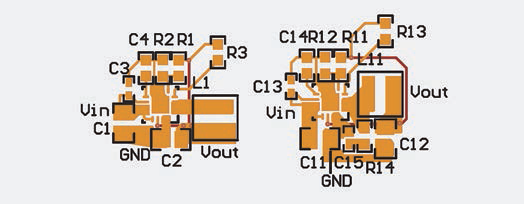

Umístěte vstupní kondenzátor tak blízko k IO, jak to jen pravidla pro osazení desky povolují. Propojení s IO je provedeno pomocí měděné plochy. Takové široké a krátké spojení minimalizuje indukčnost plošného spoje. Až v kroku 5 přidáte propojovací otvory (via) k napojení na napájení a zem systému, protože nyní to není tak důležité. Obr. 2 ukazuje správnou vzájemnou polohu obou součástek a způsob jejich propojení, a to ve dvou variantách (C1 a C11, U1 a U11). Vývod 1 obvodu IO je v pravém dolním rohu.

Obr. 2 Rozmístění a propojení IO a vstupního kondenzátoru k omezení napěťových špiček

Druhou nejdůležitější součástkou k umístění a propojení je tlumivka a filtrační člen (pokud je vyžadován). Tyto obvody jsou někdy potřebné ke snížení elektromagnetické interference (EMI) SMPS tím, že zpomalí doby náběhu a sestupu na vývodu SW. Naneštěstí, zpomalení časových průběhů snižuje účinnost, protože dochází ke zvýšení spínacích ztrát. Protože napětí na vývodu SW kolísá od napájecího napětí až k nule s velmi rychlými náběhy a sestupy, je to hlavní zdroj EMI v SMPS. Moderní SMPS mívají zabudovanou techniku k omezení EMI, která eliminuje potřebu pro filtrační člen. Aby to bylo účinné, přidejte RC filtr do návrhu desky už v tomto kroku, protože je nyní možné provést nejkratší propojení mezi SW a PGND (GND) vývody, čímž se minimalizují parazitní indukčnosti [1].

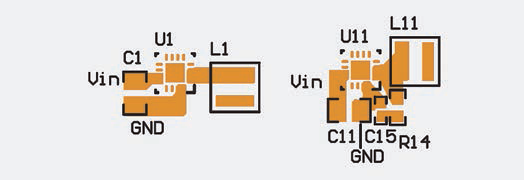

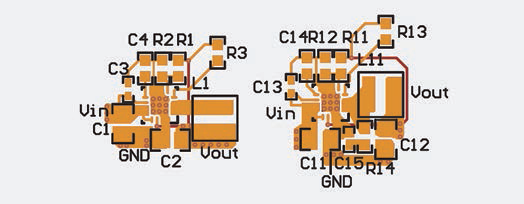

Pro snížení vyzařované EMI umístěte cívku co nejblíže k IO tak, aby plocha mědi SW‑node byla minimální. Všechna měď připojená k SW‑node je jednou vrstvou parazitního kondenzátoru, když jeho druhou vrstvou je každý připojený bod obvodu. Otočte cívkou podle potřeby pro snadné připojení k výstupnímu kondenzátoru (krok 3). Na obr. 3 je vidět správné umístěné cívky (L1 a L11) s/bez RC filtru (R14 a C15) od SW k PGND (GND).

Obr. 3 Umístění a propojení cívky L1, případně L11, s RD obvodem C15, R14

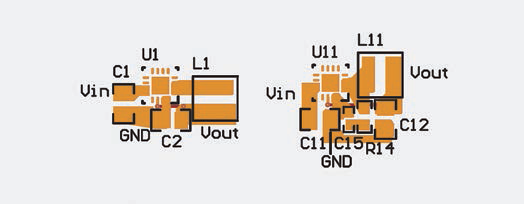

Výstupní kondenzátor uzavírá kapitolu propojení výkonových součástek (interní MOSFETy, vstupní a výstupní kondenzátor, tlumivka a volitelný filtr). Je poslední součástkou připojenou na zemnicí svorku systému a je umístěn tak, aby minimalizoval vzdálenost cívky k zemi. Nevhodné umístění výstupního kondenzátoru způsobuje obtížnou regulaci výstupního napětí.

Každý výkonový prvek je umístěn tak, aby jejich vzájemné propojení bylo co nejkratší. SMPS pracuje nejlépe, když jsou tyto spoje krátké. K propojení by neměly být použity žádné propojovací otvory (via), protože ty výrazně přidávají plošným spojům indukčnost. Pouze ve specifických případech by bylo možné je použít na propojení k SW‑node – viz poznámky na konci tohoto článku.

Ze signálních spojů je nejvíce kritické propojení k vývodu VOS. Nevhodné propojení k VOS nebo takové, které je zamořené šumem, způsobuje obtíže s regulací výstupního napětí, zakmitávání, a někdy i selhání IO. Položte plošný spoj nyní, aby měl přednost před ostatními signálovými spoji. Proveďte plošný spoj k VOS jako krátké a přímé spojení s výstupním kondenzátorem. Kvůli rozložení vývodů součástky TPS62130A propojte VOS vývod přes dva via otvory a samostatný plošný spoj k výstupnímu kondenzátoru. K omezení sejmutí šumu izolujte dva via otvory od ostatních spojů s výjimkou spoje k VOS vývodu a měděné ploše výstupního napětí na horní straně desky. Nepropojujte VOS vývod součástky TPS62130A přímo na horní straně, protože by to přerušilo spoj k PGND, který je důležitější. Obr. 4 ukazuje správné umístění a propojení výstupních kondenzátorů C2 (případně C12) a položení plošného spoje k VOS na spodní straně desky.

Obr. 4 Rozmístění a propojení výstupního kondenzátoru k vývodu VOS pro správnou regulaci výstupního napětí

Součástky, které pracují se slabým signálem, jsou analogové a číslicové, a nejsou přímo zapojeny do převodu výkonu. Jsou to součástky jako FB vývod děliče napětí, kondenzátor pro soft‑start a jakékoliv blokovací kondenzátory s malou hodnotou, např. 0,1 μF. Zatímco výkonové součástky generují šum, analogové součástky zpracovávající slabé signály jsou citlivé na šum. Umístěte každou z těchto součástek blízko IO a propojte je krátkým a přímým plošným spojem kvůli citlivosti na šum. Zejména je důležité mít FB uzel tak malý, jak je to jen možné, za účelem minimalizace vlivu šumu a zajištění dobré regulace výstupního napětí. Použijte společnou analogovou nebo klidnou zem. Ponechte všechny součástky na jedné straně desky, aby jejich propojení bylo jednoduché. Známé problémy spojené s nevhodným rozmístěním a propojením signálových součástek zahrnují špatnou regulaci výstupního napětí, nepředvídatelný soft‑start a funkční problémy součástek.

Jakékoliv digitální signály, jaké jsou např. na vývodech EN a PG, nejsou důležité z pohledu propojení a umístění spojů, takže je nechte až nakonec. Výstupy digitálních vývodů mají typicky nízkou impedanci. Jakýkoliv pull‑up nebo pull‑down rezistor, který je obecně vyžadován, může být umístěn kdekoliv podél cesty signálu a nemusí být umístěn blízko k SMPS. Obr. 5 ukazuje správné umístění a propojení signálových součástek: FB rezistory (R1, R2 a R11, R12), SS/TR kondenzátor (C4 a C14), AVIN blokovací kondenzátor (C3 a C13) a pull‑up rezistor u vývodu PG (R3 a R13).

Obr. 5 Rozmístění a propojení digitálních a signálových součástek

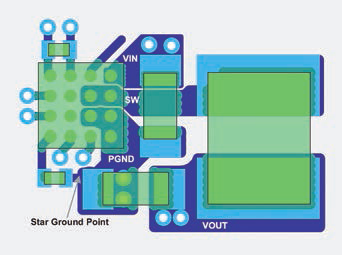

Vždy sledujte doporučení pro zemnění uvedené v katalogových listech. Obecně to znamená dodržet jednu zem pro výkonové součástky, které bývají zdrojem šumu, a oddělenou zem pro součástky pracující se slabými signály, které bývají klidné. Stačí dodržet doporučení a jednotlivé kroky, které jsou zde uvedené. Spojte obě zmíněné země do jednoho bodu, typicky do obnažené termální plošky pod IO, která by také měla být propojena se zemí. S odvoláním na obr. 5, jediným zásahem do země je úplné vylití měděné plochy mezi vývody PGND a termální ploškou. Katalogový list pro TPS62130A jde ještě dále, když požaduje toto propojení jako povinné. Pokud by se tak neprovedlo, mohly by nastat problémy spojené se šumem, jako špatná regulace výstupního napětí, nebo dokonce nesprávné logické úrovně na vývodech digitálních vstupů. To je způsobeno rozdílem napětí mezi zeměmi během činnosti obvodu. Správné provedení země také zajišťuje nejlepší termální odlehčení součástky.

Když je zemnění ukončeno, je čas propojit tento obvod se zbytkem systému. To může být provedeno pomocí průchozích otvorů na vstupní a výstupní napětí, zatímco zem je typicky provedena pomocí ploch vnitřních vrstev desky, aby bylo možné propojit všechna potřebná místa. V případě země je nejlepší umístit tyto otvory přímo pod IO, takže termální ploška může předávat teplo vrstvám desky. To je vyžadováno kvůli správnému odvodu tepla IO. Průchozí otvory jsou také normálně umístěné u zemnicích vývodů vstupních a výstupních kondenzátorů. Umístění otvoru v zemnicí ploše na klidných uzemněných součástkách není doporučeno, protože to může způsobit šíření šumu ze zemnicí plochy do těchto sítí. Tyto země je nejlepší propojit přímo s vývodem AGND, kde budou tvořit jediný bod připojení do termální plošky.

Průchozí otvory jsou také potřebné k propojení vstupního a výstupního napětí zpět do systému. Nejlepší je umístit via otvory vně obvodu, ne mezi vstupní kondenzátor a IO, aby nepřekážely kritickým plošným spojům mezi součástkami. Dobrým pravidlem pro stanovení počtu průchozích otvorů je 1 via na 1 A proudu. I tak ale je lepší jich mít více, pokud to prostor dovolí. Ukončený návrh desky je vidět na obr. 6.

Obr. 6 Dokončený návrh desky, propojení přes via otvory a zemnění v jednom bodě

Vždy se řiďte doporučeními v katalogovém listu dané součástky a vzorovým příkladem. Upozornění a příklady tam obsažené jsou dostatečné pro většinu návrhů. Jeden typ návrhu desky, který způsobuje zmatky, lze obvykle nalézt na WCSPs (wafer chip‑scale packages), jakým je například TPS62360. U mnohých WCSP step‑down konvertorů je rozmístění vývodů IO takové, že vývod SW je mezi vývody VIN a PGND (GND). Pokud se řídíme popsaným krokem 1, vstupní kondenzátor blokuje přístup k vývodu SW, pokud je vývod SW propojen pod kondenzátorem. To se může zdát nevhodné, protože to propojení musí být dosti tenké, aby mohlo projít mezi vývody malé součástky, jakou je vstupní kondenzátor. To potom vypadá tak, jak je ukázáno na obr. 7.

Obr. 7 Doporučené provedení návrhu s TPS62360 v provedení WCSP pouzdra [2]

Preferovanou metodou návrhu desky je propojení vývodu SW pod vstupním kondenzátorem (obr. 7). Plošný spoj od vývodu SW je nejen tenký, ale také velmi krátký, což udržuje SW uzel malý. To odpovídá kroku 2 pro zamezení EMI. Pokud není možné takový spoj zhotovit, potom použijte via otvory k připojení vývodu SW k indukčnosti. Via otvory v tomto spoji zřídka kdy vytváří EMI kvůli delšímu spoji. Nicméně, přidaná indukčnost těchto průchozích otvorů není tak kritická, jako je parazitní indukčnost v sérii s indukčností cívky. Použití průchozích otvorů tímto způsobem je lepší volbou, než je přesunutí vstupního kondenzátoru z jeho ideální polohy.

Když navrhujete desku pro SMPS, vždy se podívejte na katalogový list součástky, kde naleznete různé příklady a praktická doporučení. V případech, kdy není možné se přesně řídit danými doporučeními, nebo i v případě, kdy nejsou k dispozici, řiďte se pěti jednoduchými pravidly pro správný návrh snižujícího konvertoru:

Provedením těchto kroků si zajistíte robustní návrh desky, která bude dobře sloužit v serverech, tabletech a dalších zařízeních, která používají snižující konvertor.

Literatura a odkazy:

[1] Jeff Falin, „Minimizing Ringing at the Switch Node of a Boost Converter“, Application Note, Texas Instruments, September 2006 (www.ti.com/lit/an/slva255/slva255.pdf)

[2] Layout example taken from the TPS62360 datasheet, figure 52, page 35. (www.ti.com/lit/ds/symlink/tps62360.pdf)

[3] www.ti.com/product/tps62130a

[4] www.ti.com/lit/ds/slvsau9c/slvsau9c.pdf

[5] Zdroj: Five steps to a great PCB layout for a step‑down converter (Chris Glaser, Applications Engineer), Analog Applications Journal, First Quarter, 2015