Cílem tohoto příspěvku je ukázat moderní trendy v oblasti programovatelných hradlových polí typu FPGA. Příspěvek je rozdělen na sekci aplikační, kde jsou uvedeny oblasti využití hradlového pole a na sekci popisující moderní trendy v oblasti softwarového vybavení. Cílem článku není detailně popisovat strukturu hradlového pole a ani jednotlivých softwarových nástrojů, ale spíše čtenáře seznámit s vybranými aplikacemi.

Je známo, že základním stavebním blokem dnešních digitálních systémů je mikroprocesor nebo mikrořadič, který vykonává instrukce sekvenčně a to v pořadí, v jakém byly zapsány v programu. Mikroprocesor je neustále považován za součástku, respektive elektronický obvod, poskytující určitou škálu funkcí a periferních zařízení, což je na jedné straně nesporná výhoda, ale na straně druhé omezení, kterými se vývojář musí řídit a v podstatě čekat na to, jak se zachová výrobce dané platformy.

Zvýšení flexibility a mnohdy i výkonu přináší technologie hradlových polí typu CPLD nebo FPGA umožňující prakticky neomezenou tvorbu uživatelských bloků a požadované funkcionality na jednom čipu s ohledem na cenu a dostupnost vhodných komponentů na trhu. Další nespornou výhodou je, že vzniklé řešení prakticky nestárne a technologicky nezaostává, a dá se říci, že je nezávislé na změnách součástkové základny ba dokonce i na výrobci daného pole (to samozřejmě nemusí platit obecně).

Existuje několik přístupů, jak využít programovatelných struktur typu FPGA v aplikacích. Prvním a vlastně dnes už klasickým přístupem je kombinace mikroprocesor a hradlové pole. V tomto případě bylo CPLD/FPGA převážně využíváno jako adresový dekodér nebo jednoduchá periferie procesoru (obvody typu GAL/PAL/CPLD). V současnosti se tato kombinace spíše uplatňuje na úrovni procesor – FPGA, kdy FPGA přebírá funkci výkonného akcelerátoru např. pro zpracování a kompresi obrazu, náročné výpočty, generování obrazových dat, inteligentní periferie – řadiče displejů a pamětí, sběrnice PCI express, přepínače linek, rozhraní Ethernet, kamerová rozhraní nebo jako nezávislý řídicí systém SoC s integrovanými procesory Power PC, soft-jádry Mircoblaze, Nios II nebo OpenSPARC.

Obr. 1 Podíl FPGA v technických odvětvích

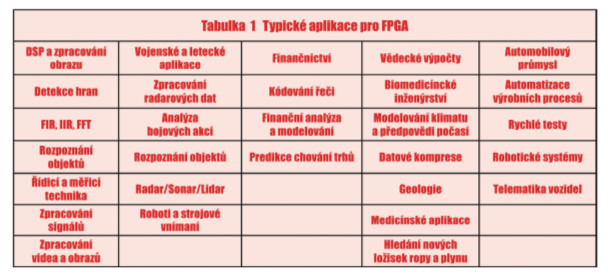

Procentuální zastoupení FPGA v jednotlivých oborech ukazuje obr. 1 (zdroj: firma Xilinx říjen 2009). Z obrázku vyplývá, že hlavní doménou pro hradlové pole jsou telekomunikace a průmyslová odvětví. Postupem času bude docházet k masivnímu nasazení FPGA v automobilech – tento trend se zatím neprojevuje z důvodu relativně dlouhého vývojového cyklu v automobilovém průmyslu způsobeného náročnou certifikací. Jedno z prvních vozidel vybavených hradlovým polem Virtex 4 s integrovaným procesorem Power PC je BMW řady 7. Další příklady využití FPGA v různých technických oborech shrnuje tab. 1.

Tabulka 1 Typické aplikace pro FPGA

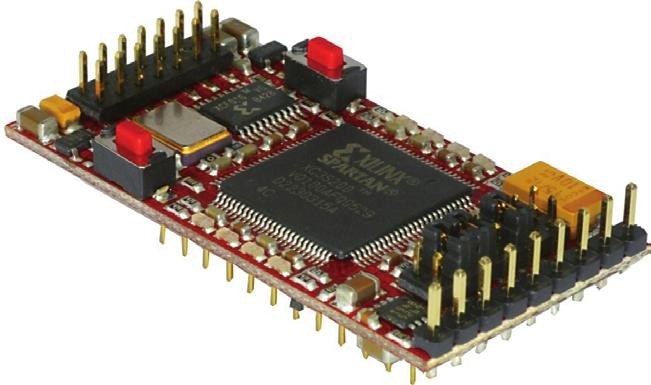

V automatizační technice se jedná především o zpracování dat a signálů, řízení technologických procesů, ve kterých je požadována rychlá odezva, funkční bezpečnost nebo paralelní zpracování několika nezávislých úloh. Obvykle se v aplikacích využívají menší pole typu FPGA z tzv. „low cost“ segmentu (Xilinx – Spartan 3 a 6 nebo Altera – Cyclone III a IV) v pouzdrech TQFP nebo hotové moduly, které mají osazeny rozšiřující periferie potřebné pro funkci systému (oscilátory, konfigurační paměti, paměti FLASH, DDR, napájecí zdroje). Takto koncipovaný systém pracuje s tzv. soft-core procesory – standardně se jedná o procesory Microblaze/NIOS II (RISC 32 bitů, pracovní frekvence 50–150 MHz), PicoBlaze (8 bitů, pracovní frekvence 50–200 MHz), který nahradí a převezme funkci externího procesoru. Řešení je cenově výhodné a také robustní, protože vyžaduje minimální počet externích spojů, které by mohly podléhat nežádoucímu rušení nebo naopak rušením ovlivňovat činnost jiné elektroniky. Nezapomeňme na fakt, že FPGA je ve své podstatě masivně paralelní systém, dovolující vytvářet takový počet bloků (instancí), který se do daného pole úspěšně rozmístí. Pro představu uveďme, že v poli Spartan 3E-500 (v cenové relaci < 400 Kč) lze vytvořit 16 procesorů Pico-Blaze, kdy je ke každému procesoru připojen sériový port s 16úrovňovým vyrovnávacím buferem a v poli je spotřebováno 65 % zdrojů. Příklad jednoduchého řídicího modulu zobrazuje obr. 2.

Obr. 2 Řídicí modul s FPGA

V měřicí technice se jedná o úlohy zpracovávající signály z atypických rozhraní. Příkladem mohou být smart kamerové systémy určené k vyhodnocování stopy laserového svazku s vysokým rozlišením (1280×1024 obrazových bodů v bitové hloubce 10–12 bitů) a snímkovou frekvencí přesahující 500 Hz. Systém s těmito parametry musí za 1 sekundu vyhodnotit data v objemu větším než 750 MB, což je objem pro běžný mikroprocesor takřka nezpracovatelný. Obdobně je tomu u akvizice dat z AD převodníků nebo generování logických a analogových datových sekvencí. Hradlová pole dokážou přijímat a zpracovávat signály na frekvencích přesahujících 200 MHz.

Typickou doménou hradlových polí jsou aplikace zaměřené na komunikace v rozsahu od jednoduchých sériových rozhraní typu RS232 nebo RS485 přes rozhraní LVDS a Ethernet až po rozhraní typů PCI Express nebo 10Gbit Ethernet, OC-192 a v současnosti hojně diskutovaný 100Gbit Ethernet. Výhodou moderních hradlových polí je integrace sofistikovaných periferních zařízení, které uživateli umožní rychlejší a spolehlivější aplikování cílové funkce. Příkladem muže být již zmiňované rozhraní PCI Express, které je dnes již standardně integrováno v hradlových polích firem Xilinx – řada Virtex 5, 6 popř. „low cost“ varianty v řadách Spartan 6 LXT nebo v řadách Aria GX, Cyclone IV a Stratix IV a V firmy Altera. Hradlová pole pochopitelně nacházejí uplatnění i v oblasti bezdrátových komunikací, přenosu televizního signálu, mobilních sítích GSM a v neposlední řadě v přenosu satelitních signálů (modulace, kódování, zabezpečení, komprese). Pro zpracování velkého objemu dat jsou hradlová pole vybavena DSP bloky podporujícími funkce MAC (Multiply and Accumulate). DSP blok je schopen pracovat na frekvencích do 600 MHz a zpracovávat datové signály v šířce 25 bitů. Největší pole typu FPGA obsahují více než 1000 DSP bloků na jednom čipu.

Oblast komunikací a zpracování signálů vyžaduje odkládací prostor pro zpracovávaná data a mezivýsledky. Malé objemy dat jsou ukládány do vnitřních paměťových bloků FPGA a rozsáhlejší datové soubory obvykle ukládány do externích pamětí typu DDR, DDR 2, DDR 3 a QDR II. Hradlová pole mají podporu pro připojení těchto typů pamětí až do 800 milionů transakcí na pin za sekundu.

K méně typickým, ale dnes rozšířeným aplikacím patří finanční analýzy, zpracování finančních dat, modelování a predikce burzovních operací, kde se využívá masivního paralelního zpracování dat na clusterech FPGA (systém obsahuje stovky až tisíce FPGA).

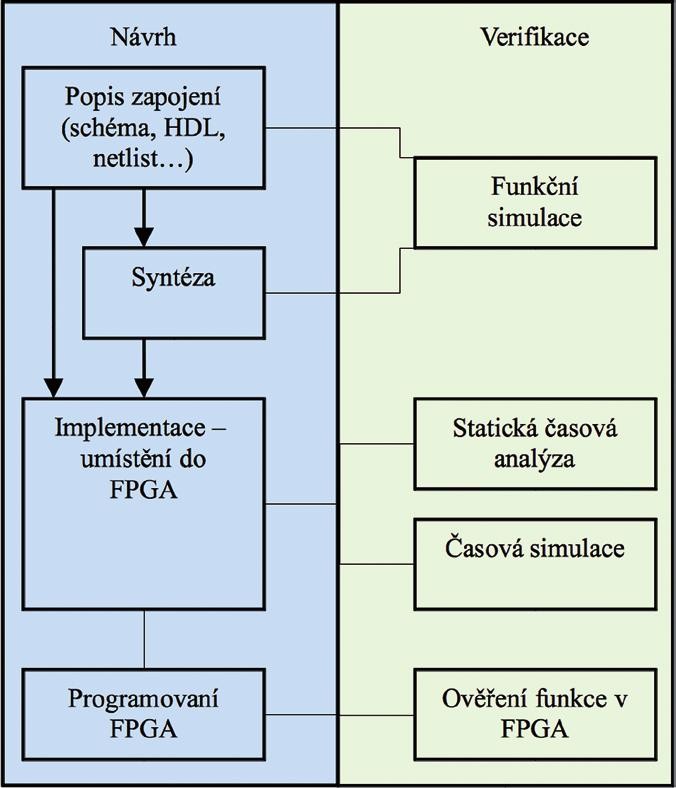

Nedílnou součástí technologie hradlových polí je softwarové vybavení, které se vyvíjí společně s hardwarovými prostředky dané platformy. Velmi zjednodušený postup návrhu funkcionality v FPGA je uveden na obr. 3. Pokud pomineme vlastní ideovou část návrhu, tak prvním krokem bývá popis zapojení nebo funkcionality realizované v FPGA. V dřívějších dobách byl obvyklý popis ve schematických značkách s využitím jednoduchých předdefinovaných bloků (klopné obvody, čítače, aritmetické funkce). V dnešní době se využívá pro popis vyšší forma abstrakce v podobě strukturovaných textů – HDL jazyků (VHDL, Verilog, Impulse C, System C) nebo generátorů IP (Intelectual Property) funkcí, což jsou obvykle sofistikované bloky – PCI Express endpoint, FFT, hranový filtr, float point jednotka a jiné. V určitých případech je vhodné využít systémy pro podporu výstavby platforem typu SoC (Systém on Chip), které jsou určeny pro návrh komplexních celků s jedním nebo více procesory, sběrnicovým systémem, podporou různých typů periferních zařízení a řadiči paměti. V případě návrhu typu SoC se používá grafické rozhraní, které pomocí skriptů vygeneruje odpovídající HDL kód celého designu.

Obr. 3 Typický postup při návrhu designu FPGA

Při vzniku a tvorbě designu je dobré pamatovat na verifikaci vznikajícího řešení. V prvním případě se jedná o ověření funkce nově vzniklé komponenty. Např. tvoříme funkci součtu dvou celých čísel. Operaci součtu lze zapsat ve vyšších jazycích jednoduše pomocí operátoru „+“ nebo ve schématu symbolickou značkou obvodu sčítačky. Ovšem to neznamená, že náš zápis bude provádět korektně součet pro úplnou množinu celých čísel, a zda správně ošetřuje přetečení nebo zpracovává záporná čísla. Ověření funkce v této etapě designu se nazývá funkční simulace a lze ji provádět v simulátorech. Simulátor je program řízený diskrétní událostí, což znamená, že simulace se spustí, jen když nastane zájmová událost – řekněme změna na vstupu. Změny jsou simulátorem pravidelně vyhodnocovány a tak získáváme obraz vstupů a výstupů, podle kterého dokážeme rozhodnout, zda 2 + 2 = 4 a –1–1 je skutečně –2. Simulátory jsou obvykle dodávány jako součást softwarových balíků od výrobce FPGA (jedná se o ModelSim od firmy Mentor Graphics nebo Active-HDL od firmy Aldec). Bezplatné verze jsou limitovány rozsahem simulovaného zapojení nebo rychlostí simulace.

Když víme, že zapojení je funkční, můžeme přistoupit k syntéze zapojení pomocí syntetizéru, který převede HDL kód do netlistu – tedy do popisu pomocí elementárních bloků, které daná cílová platforma FPGA podporuje (hradla, LUT, klopné obvody). Následně přejdeme na fázi rozmisťování designu do FPGA (rozložení pinů, umístění bloků v FPGA, časová omezení a další). Z hlediska verifikací se provádí časové analýzy a ověřuje se, zda je naše zapojení schopno splnit časové nároky na ně kladené – pracovní frekvence, zpoždění vstup-výstup, hold a setup-time. Po úspěšné implementaci do FPGA zbývá provést ověření funkčnosti celého zapojení v reálné aplikaci.

Pro ověření funkce a ladění funkce v reálné aplikaci se používají osciloskopy, logické analyzátory nebo prostředky dodávané výrobci hradlových polí pro verifikaci pomocí rozhraní JTAG, které se využívá pro řízení a přenos získaných dat. Data jsou ukládána do interních pamětí hradlového pole. Spouštění a ukládání dat zajišťuje funkční blok vygenerovaný nástroji výrobce dané platformy. Firma Xilinx používá obchodní označení ChipScope a firma Altera SignalTAP. Získaná data jsou zobrazována ve formě průběhu podobně jako na logickém analyzátoru nebo osciloskopu. Verifikace touto formou je vysoce účinná a efektivní, nevyžaduje žádné speciální testovací body ani neklade nároky na hardwarová vybavení. Nevýhodou je spotřeba vnitřních zdrojů FPGA, které jsou využity pro řízení vzorkování a archivaci dat v interních paměťových blocích.

Z výše uvedeného popisu vyplývá, že návrh a implementace složitých bloků může být časově a finančně náročné, a proto se v současné době začínají využívat techniky s ještě vyšší formou abstrakce. Především se jedná o překladače kódu C do jazyka HDL, generátory funkčních celků nebo využití již existujících a ověřených funkcí. Jednou ze zajímavých cest se ukazuje překlad jazyka C do HDL. Nespornou výhodou je rychlá modifikace vznikajícího kódu, velmi vysoká rychlost ověření funkčnosti zapojení simulací přímo v jazyku C při použití standardních nástrojů Microsoft Visual C nebo open source balíku Mingw. Nevýhodou jazyků C2H je zatím horší využití cílové platformy než při implementaci v HDL a bohužel i chybějící standard.

Více informací, referenčních příkladů a návodů je možno získat u společnosti DFC Design na adrese www.dfcdesign.cz.

Společnost DFC Design je zaměřena na vývoj hardwaru a softwaru v oblasti číslicového zpracování signálu, emdedded zařízení a průmyslových aplikací. Jednou z oblastí, ve kterých společnost dosahuje významných výsledků, je vývoj aplikací na bázi programovatelné logiky a mikroprocesorových systémů.