Simulace a verifikace HDL jazyků (VHDL, System Verilog, Verilog, SystemC, …) je součástí vytváření jak zákaznických ASIC, tak FPGA obvodů. Stále složitější funkce realizované jedním čipem vyžadují komplikované programy, které mají tuto funkci realizovat. Proto programy pro simulaci poskytují rozšířené možnosti, lze detekovat nejen, zda program proběhl správně, ale i zda splnil zadané úkoly a také kolik procent kódu bylo otestováno.

Cena výroby waferu (reálného čipu z křemíku) je taková, že se vyplatí použít k odstranění většiny závad náročný proces verifikace zahrnující drahý software. I přesto ASIC čipy dosahují pouze 30% funkčnosti při prvním procesu výroby. Nejúspěšnější návrhy jsou potom použitelné ve druhé, odladěné vyrobené verzi. Oproti tomu FPGA čipy mají nižší náklady na vývoj, ale vyplatí se pouze pro produkty s nižším objemem produkce. (Jejich pořizovací cena s větším objemem neklesá na rozdíl od ASIC.) S rostoucí složitostí, která má za následek vzrůst kapacity a schopností dnešních FPGA až k složitým SoC FPGA, začíná být tradiční přístup k těmto typům obvodů nedostatečný a blíží se tak postupně ASIC.

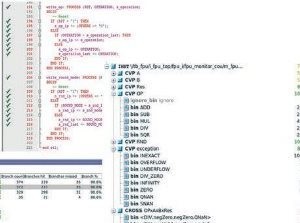

Obr. 1 Ukázka jednotlivých segmentů z prostředí verifikace,

zleva shora průběh jednotlivých signálů, ověřené řádky v HDL kódu a vpravo a dole míra verifikace kódu

Funkce nástrojů pro vytváření a ověřování HDL programů odpovídají rostoucím nárokům. Jedním z nich je již zmíněná informace, do jaké míry byl kód otestován dodatečně k tomu, jestli proběhl správně. Existuje dokonce několik přístupů k rozhodování, kdy je verifikace u konce, kdy je ověření všech částí programu splněno. Patří sem pokrytí kódu (code coverage), tvrzení (assertions coverage), transakcí (transaction coverage), funkční pokrytí (functional coverage) a další.

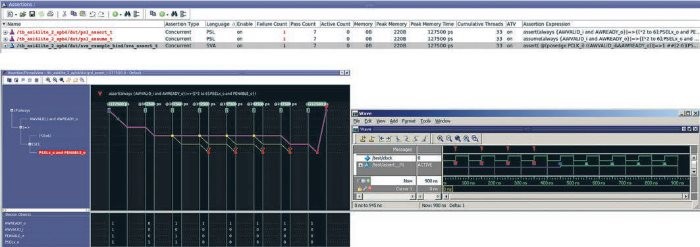

Obr. 2 Zobrazení časového průběhu assertions. V levé části logické zobrazení, v pravé potom v časových průbězích

Tyto a další funkce implementuje velké množství programů od těch poskytovaných zdarma s FPGA obvody pro jejich vývoj až po programy schopné verifikovat jak ASIC, tak FPGA popsané ve více než jednom jazyku. Mezi nejznámější patří IES od Cadence, ModelSim/ Questa od Mentoru, Active-HDL/Riviera-PRO od Aldecu, VCS od Synopsys nebo ISE/Vivado od Xilinx. Z poskytovaných zdarma pak zmiňme Icarus Verilog od Stephena Williamse.

Verifikační nástroj IES je moderní verzí simulátoru NC-Verilog, který vznikl po nákupu programu Verilog-XL (akvizici celé firmy Gateway Design společností Cadence) jako odpověď na rychlejší simulátory konkurence a jeho výhodou proto i dnes zůstává rychlost. Program ModelSim má největší podíl na trhu a dalo by se říci, že je standardem v oboru. Je využíván především pro ověřování FPGA a je jedním z nejlepších pro návrh kombinovaný z více HDL jazyků. Questa (vyšší program od stejného výrobce) potom podporuje všechny nejnovější metodologie a standardy pro ověřování kódu (OVM, UVM, constrained random a functional coverage). Program VCS podporuje stejně jako ostatní všechny používané jazyky a pokročilé metody ověřování.

V předchozím odstavci jsou zmíněné tři komerčně nejpoužívanější programy, jejichž nejnižší úroveň, leckdy ještě uměle oslabená co do výkonosti, je často dodávána s FPGA obvody. Asi nejčastějším takovým případem je právě ModelSim, který již v základní sestavě poskytuje nástroje nutné pro základní verifikaci pomocí assertions (tvrzení) a code coverage (zjištění, do jaké míry byl kód verifikací pokrytý). Dále ModelSim dokáže sestavit logický obvod na základě zapsaného kódu a určit signály, které ovlivňují vstupy a výstupy. V rozšířených sestavách potom zvládá ověřování obou jazyků (VHDL, Verilog) současně a v případě Questy pak umožňuje používat i randomizaci, využívat UVM standard a další nástroje pro plánování verifikace a zpracování výstupů o pokrytí testovaného kódu.

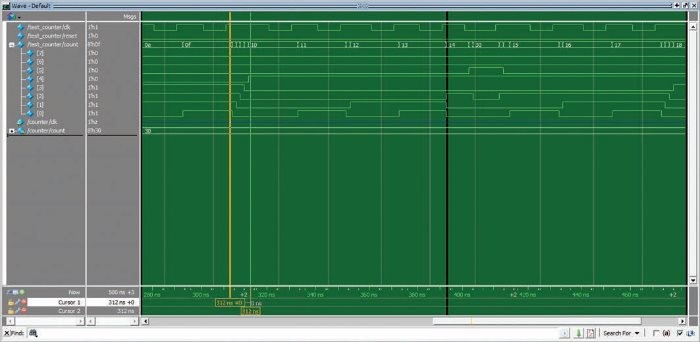

Obr. 3 Ukázka rozdělení jednoho kroku hodin do několika postupných změn

v různých signálech – ModelSim (expanded time delta mode)

Nejvyšší řady těchto programů (např. Questa Prime) podporují přístup verifikace nazvaný constrained random (omezená náhoda). V přímém přístupu k verifikaci (directed verification), který je opakem constrained random, jsou testy vytvořeny přímo verifikačním inženýrem k ověření určitých podmínek. Pro jejich počet je jejich správa náročná a pochopitelně i časová náročnost je větší, přestože ověřují pouze očekávané chování. Vnesení (omezené) náhody do procesu ověřování snáze dosáhne okrajových případů napsaného kódu. Obvykle lze použít několik přímých testů pro ověření zřejmých postupů a náhodnou změnou některých parametrů potom ověřit zbytek kódu. Zpětnou vazbou potom může být faktor function coverage a další testy je tak možné přizpůsobit (ne)provedenému kódu. Kód, který nebyl proveden (a tím ověřen) totiž může skrývat neodhalené chyby.

Výběr programů pro verifikaci HDL jazyků je velký, ale ve většině případů se uživatelé omezují na program dodaný s vyvíjenou platformou (ISE, ModelSim*-Intel® FPGA, …), dokud nedosáhnou omezení těchto nástrojů. Potřeba výkonnějšího programu co do rychlosti i schopností verifikovat celou strukturu přichází v případě vytváření stále větších a složitějších projektů.

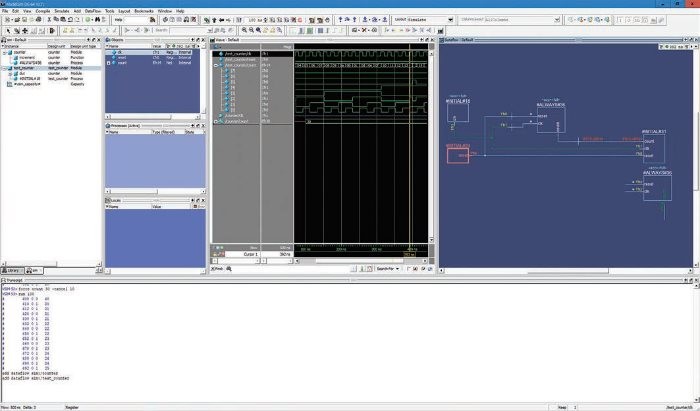

Obr. 4 Celkový pohled na program ModelSim s okny knihoven, průběhy,

obvodové znázornění jednoduchého programu s příkazovým řádkem dole

radek@cadware.cz